| ID |

Date |

Author |

Subject |

|

790

|

Tue May 26 11:10:27 2020 |

xggg | Domino wave |

Hi Stefan,

According to the datasheet DRS_rev09, the write signal is always 16 cells wide. So when the domino wave runs in infinite mode and be stopped by setting DENABLE low , there are always 16 cells capicitors tracking the input signal . It means that the effective sample cells is 1024-16=1008? That's confusing. |

|

791

|

Tue May 26 12:44:16 2020 |

Stefan Ritt | Domino wave |

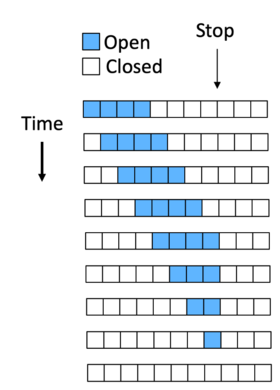

Look at the attached picture. For simplicity, only 4 cells are open and tracking the input signal. Time is flowing from top to bottom. So initially, a train of 4 cells is open. When it's stopped, the train stops not immediately, but kind of "runs against a wall" at the stop cell. So each cell is open for four time ticks effectively, and you can use all 1024 cells.

| xggg wrote: |

|

Hi Stefan,

According to the datasheet DRS_rev09, the write signal is always 16 cells wide. So when the domino wave runs in infinite mode and be stopped by setting DENABLE low , there are always 16 cells capicitors tracking the input signal . It means that the effective sample cells is 1024-16=1008? That's confusing.

|

|

| Attachment 1: Screenshot_2020-05-26_at_12.43.40_.png

|

|

|

619

|

Fri Jun 16 17:34:20 2017 |

Laura Gonella | Driver installation on Windows 10 |

Hello,

I am trying to get a DRS4 board to run on Windows 10. I am having problems with the driver installation. I am getting the follwoing message

"There is no driver selected for the device information set or element"

I had specified the path to look for the driver as C:\ProgramFilesx86\DRS\driver\. I also tried the option to look online for the driver. None works. Can anyone help?

Thanks,

Laura |

|

625

|

Thu Jul 20 13:00:44 2017 |

Volodymyr Rodin | Driver installation on Windows 10 |

Dear Laura

You need to disable driver signature enforcement. Then try again with path option.

It helped me.

http://www.drivethelife.com/windows-drivers/how-to-disable-driver-signature-enforcement-on-windows-10-8-7-xp-vista.html

Best regards,

Volodymyr

| Laura Gonella wrote: |

|

Hello,

I am trying to get a DRS4 board to run on Windows 10. I am having problems with the driver installation. I am getting the follwoing message

"There is no driver selected for the device information set or element"

I had specified the path to look for the driver as C:\ProgramFilesx86\DRS\driver\. I also tried the option to look online for the driver. None works. Can anyone help?

Thanks,

Laura

|

|

|

457

|

Wed Dec 23 15:38:14 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony |

|

458

|

Wed Dec 23 15:48:42 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

459

|

Thu Dec 24 10:51:31 2015 |

mony orbach | Dtap stops toggling after 40msec |

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

460

|

Thu Dec 24 12:45:41 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

Draft

|

Sun Dec 27 15:06:59 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

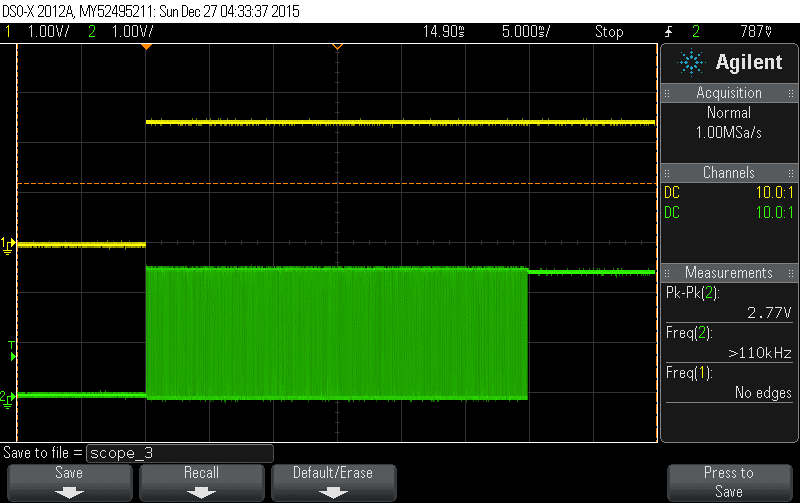

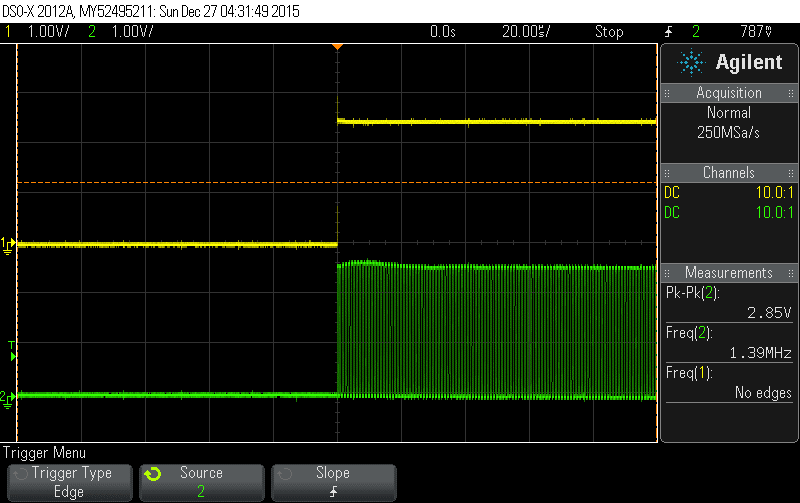

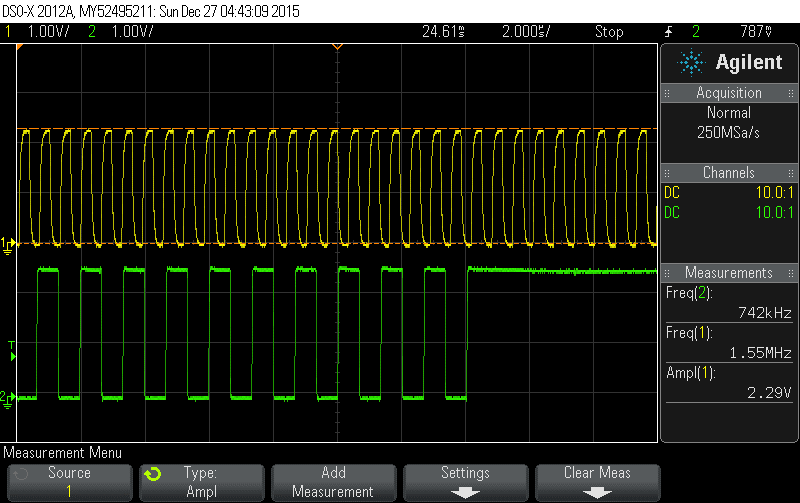

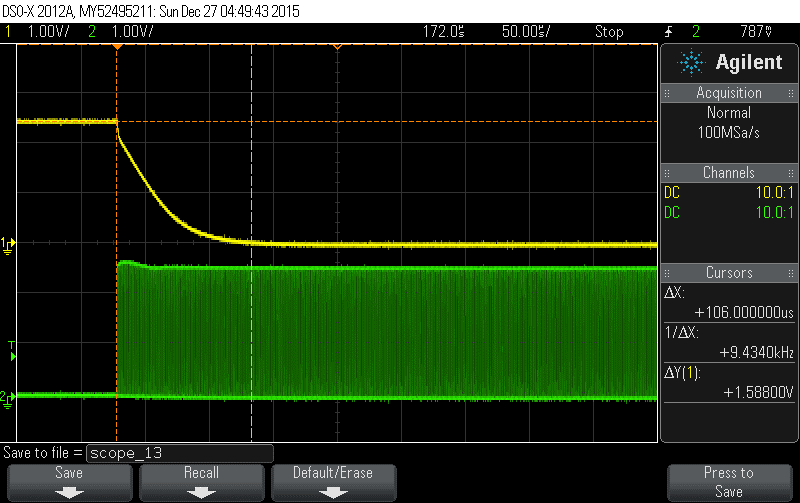

We have some meesurs to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Ref+

- Dtap + Dspeed

From the screen shots it can be seen that ref+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

| Stefan Ritt wrote: |

|

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

|

462

|

Sun Dec 27 15:41:32 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

| Stefan Ritt wrote: |

|

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

| Attachment 1: Dtap-Denable.gif

|

|

| Attachment 2: dtap-Danable2.gif

|

|

| Attachment 3: Dtap-refck.gif

|

|

| Attachment 4: Dtap-Dspeed.gif

|

|

|

463

|

Mon Dec 28 11:05:15 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|

|

464

|

Mon Dec 28 11:21:54 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi Stefan

Thanks for your input.

We are in the process of assemble another PCB board.

so soon we can compere between two boards.

As for the PLLEN bit, we set it.

We checked several times the soldering of the DRS4 using a microscope.

Everything looks ok.

In what method do you recommend to solder the DRS4?

Thanks for the invitation to meet.

120Km is not so far J

mony

| Stefan Ritt wrote: |

|

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|

|

|

465

|

Wed Dec 30 16:25:35 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

We have resolve the problem, the Dtap is now working correctly.

There were two problems:

- After configuration we put the all address bits to one (standby mode)

We are now setting the address bits to all zero. Failure

to do so result in Dtap stop toggling after several hundred milliseconds.

- The DMODE bit in contradiction to the data sheet should be set to 0

And not to 1.

Is this a known bug in the chip?

Only bay setting DMODE to zero we got the Dtap to work correctly.

The PLL locks after 1 milisec.

If we set it to one we get Dtap that stop toggling after several hundred milliseconds.

We have test it on two boards, they both worked in the same.

Never did we get a One shot Dtap.

Did you published a errata page to the drs4?

Thanks, Mony

| mony orbach wrote: |

|

Hi Stefan

Thanks for your input.

We are in the process of assemble another PCB board.

so soon we can compere between two boards.

As for the PLLEN bit, we set it.

We checked several times the soldering of the DRS4 using a microscope.

Everything looks ok.

In what method do you recommend to solder the DRS4?

Thanks for the invitation to meet.

120Km is not so far J

mony

| Stefan Ritt wrote: |

|

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|

|

|

|

466

|

Wed Dec 30 17:00:00 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

While I can understand 1., I'm puzzeled by 2.

If you put the chip in standby mode, the internal current sources are switched off, which of course make the domino wave non-functional. This is clearly stated in the data sheet.

Concerning the DMODE bit, we operate all (!) our chips with DMODE=1. Actually this is the default value. After a reset, all register bits are "1", which enables the PLL and causes DTAP to oscillate. If DMODE=1, the DTAP signal should toggle only once (!) since the domino loop is not closed. So the scope traces you showed previously are consistent with the standby mode, but not possible with ANY setting of DMODE.

Stefan

| mony orbach wrote: |

|

Hi

We have resolve the problem, the Dtap is now working correctly.

There were two problems:

- After configuration we put the all address bits to one (standby mode)

We are now setting the address bits to all zero. Failure

to do so result in Dtap stop toggling after several hundred milliseconds.

- The DMODE bit in contradiction to the data sheet should be set to 0

And not to 1.

Is this a known bug in the chip?

Only bay setting DMODE to zero we got the Dtap to work correctly.

The PLL locks after 1 milisec.

If we set it to one we get Dtap that stop toggling after several hundred milliseconds.

We have test it on two boards, they both worked in the same.

Never did we get a One shot Dtap.

Did you published a errata page to the drs4?

Thanks, Mony

|

|

|

473

|

Thu Jan 14 14:00:26 2016 |

mony orbach | Dtap stops toggling after 40msec |

surrey i forgot to update..

after carefully examining our VHDL we found out that there are brief times that we put A0-A3 in 1111

after making shore that a0-a3 never get 1111 value thae drs4 woks as expected.

The dtap toggols ok.

We can sample and read all the data channels.

So, putting A0-A3 value of 1111 even for very short period " confuse " the DRS and then it start to behave in a strange manner.

mony

| Stefan Ritt wrote: |

|

While I can understand 1., I'm puzzeled by 2.

If you put the chip in standby mode, the internal current sources are switched off, which of course make the domino wave non-functional. This is clearly stated in the data sheet.

Concerning the DMODE bit, we operate all (!) our chips with DMODE=1. Actually this is the default value. After a reset, all register bits are "1", which enables the PLL and causes DTAP to oscillate. If DMODE=1, the DTAP signal should toggle only once (!) since the domino loop is not closed. So the scope traces you showed previously are consistent with the standby mode, but not possible with ANY setting of DMODE.

Stefan

| mony orbach wrote: |

|

Hi

We have resolve the problem, the Dtap is now working correctly.

There were two problems:

- After configuration we put the all address bits to one (standby mode)

We are now setting the address bits to all zero. Failure

to do so result in Dtap stop toggling after several hundred milliseconds.

- The DMODE bit in contradiction to the data sheet should be set to 0

And not to 1.

Is this a known bug in the chip?

Only bay setting DMODE to zero we got the Dtap to work correctly.

The PLL locks after 1 milisec.

If we set it to one we get Dtap that stop toggling after several hundred milliseconds.

We have test it on two boards, they both worked in the same.

Never did we get a One shot Dtap.

Did you published a errata page to the drs4?

Thanks, Mony

|

|

|

|

474

|

Thu Jan 14 14:11:06 2016 |

Stefan Ritt | Dtap stops toggling after 40msec |

Thanks for the update, I will add a note into the data sheet.

| mony orbach wrote: |

|

surrey i forgot to update..

after carefully examining our VHDL we found out that there are brief times that we put A0-A3 in 1111

after making shore that a0-a3 never get 1111 value thae drs4 woks as expected.

The dtap toggols ok.

We can sample and read all the data channels.

So, putting A0-A3 value of 1111 even for very short period " confuse " the DRS and then it start to behave in a strange manner.

mony

| Stefan Ritt wrote: |

|

While I can understand 1., I'm puzzeled by 2.

If you put the chip in standby mode, the internal current sources are switched off, which of course make the domino wave non-functional. This is clearly stated in the data sheet.

Concerning the DMODE bit, we operate all (!) our chips with DMODE=1. Actually this is the default value. After a reset, all register bits are "1", which enables the PLL and causes DTAP to oscillate. If DMODE=1, the DTAP signal should toggle only once (!) since the domino loop is not closed. So the scope traces you showed previously are consistent with the standby mode, but not possible with ANY setting of DMODE.

Stefan

| mony orbach wrote: |

|

Hi

We have resolve the problem, the Dtap is now working correctly.

There were two problems:

- After configuration we put the all address bits to one (standby mode)

We are now setting the address bits to all zero. Failure

to do so result in Dtap stop toggling after several hundred milliseconds.

- The DMODE bit in contradiction to the data sheet should be set to 0

And not to 1.

Is this a known bug in the chip?

Only bay setting DMODE to zero we got the Dtap to work correctly.

The PLL locks after 1 milisec.

If we set it to one we get Dtap that stop toggling after several hundred milliseconds.

We have test it on two boards, they both worked in the same.

Never did we get a One shot Dtap.

Did you published a errata page to the drs4?

Thanks, Mony

|

|

|

|

|

793

|

Sat Aug 29 22:00:30 2020 |

Hans Steiger | Dynamic Range Evaluation Board and Software |

Dear Evaluation Board Team,

currently I am facing the problem of digitizing pulses with an amplitude of -0.6V to -0.8V. As the dynamic range of the board is 1Vpp, this should be feasible. However, I do not know how to set in the software a correct range. I see only -0.5V/0.5V, and the two positive options. Normally I would use -0.5V/0.5V and give the thing an offset of 0.4V or so? Is this possible? Where can I set such a offset?

All the best,

Hans |

|

794

|

Mon Aug 31 10:52:42 2020 |

Stefan Ritt | Dynamic Range Evaluation Board and Software |

You cannot go below -0.5V for the inputs, since the board does not have an internal negative power supply, which would be necessary for that. If you have -0.8V pulses, the easiest is to use a passive inverter at the input to convert it to a 0.8V pulse.

Stefan

| Hans Steiger wrote: |

|

Dear Evaluation Board Team,

currently I am facing the problem of digitizing pulses with an amplitude of -0.6V to -0.8V. As the dynamic range of the board is 1Vpp, this should be feasible. However, I do not know how to set in the software a correct range. I see only -0.5V/0.5V, and the two positive options. Normally I would use -0.5V/0.5V and give the thing an offset of 0.4V or so? Is this possible? Where can I set such a offset?

All the best,

Hans

|

|

|

204

|

Thu Dec 6 09:23:36 2012 |

Martin Petriska | EVM rev4 board trigger change and drs_example |

I switched from rev 3 to rev 4 board, but have some problems with triggering, board is now waiting for trigger (rev.3 is working). How to do in drs_exam.cpp for example triggering on Ch0 && CH1 ?

Software 4.0.0, windows version.

Here is old trigger initialisation:

b->EnableTrigger(0,1);

b->SetTriggerSource(0);

b->SetTriggerLevel(0.25, false);

b->SetTriggerDelayNs(0);

Btw. Is it possible to set up different trigger Levels for each channel ?

(If there is some interest here is my code in Qt, still aplha) http://sourceforge.net/p/qtpals/code |

|

211

|

Fri Dec 14 21:49:29 2012 |

Stefan Ritt | EVM rev4 board trigger change and drs_example |

| Martin Petriska wrote: |

|

I switched from rev 3 to rev 4 board, but have some problems with triggering, board is now waiting for trigger (rev.3 is working). How to do in drs_exam.cpp for example triggering on Ch0 && CH1 ?

Software 4.0.0, windows version.

Here is old trigger initialisation:

b->EnableTrigger(0,1);

b->SetTriggerSource(0);

b->SetTriggerLevel(0.25, false);

b->SetTriggerDelayNs(0);

Btw. Is it possible to set up different trigger Levels for each channel ?

(If there is some interest here is my code in Qt, still aplha) http://sourceforge.net/p/qtpals/code

|

Sorry the late reply.

In V4, triggering has changed. You can trigger now on an OR or AND of channels. Therefore you have to supply a bitmask, where the 1st bit = CH1, 2nd bit = CH2 and so on. Have a look at the most recent drs_exam. It contains code:

/* use following lines to enable hardware trigger on CH1 at 50 mV positive edge */

if (b->GetBoardType() == 8) { // Evaluaiton Board V4

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

} else { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

b->SetTriggerSource(0); // use CH1 as source

}

So if you want CH1 && CH2, you look at the source code of SetTriggerSource. It contains

// Set trigger configuration

// OR 0=CH1, 1=CH2, 2=CH3, 3=CH4, 4=EXT

// AND 8=CH1, 9=CH2, 10=CH3, 11=CH4, 12=EXT

So an AND between CH1 and CH2 needs a

b->SetTriggerSource(1<<8 | 1<<9);

Your code looks interesting. Do you have a screenshot or can you explain what it does? |