| ID |

Date |

Author |

Subject |

|

217

|

Wed Feb 13 16:58:40 2013 |

Martin Petriska | Nonuniform sampling | Are there any plans to include reconstruction of nonuniform sampling in DRS4 to get uniformly sampled data?

Im now reading article IEEE Trans on Circ. ans Systems I, Vol.55 No.8 sept. 2008 Reconstruction of Nonuniformly Sampled Bandlimited Signals Usinga Differentiator–Multiplier Cascade by Stefan Tertinek and Christian Vogel

and plan to implement it, but may be somebody has it done before me.

|

|

216

|

Tue Feb 5 14:38:35 2013 |

Stefan Ritt | variation of sampling capacitors |

| Jinhong Wang wrote: |

|

Hi Dr. Stefan,

So the sampling capacitors store the input voltage instead of the charge. What about the readout circuits? I saw there is a buffer followed each sampling capacitor. Do you buffer the charge (like a charge sensitive amplifier) or the voltage? From Fig.12, 14 in datasheet, it seems most probably the readout is a charging or discharging of a capacitor. Could you please add some comments on this?

Cheers,

Jinhong

|

The buffer buffers the voltage, not the charge. The curves in Fig. 12, 14 indicate that the voltage followers take some time until they settle.

Stefan |

|

215

|

Fri Feb 1 17:43:48 2013 |

Jinhong Wang | variation of sampling capacitors |

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan,

A quick question, what is the typical variation of the sampling capacitors in DRS4? Will this variation be significant to affect your sampling result?

Best,

Jinhong

|

The capacitors sample the input voltage, not the charge, so the actual size of the capacitors does not matter on first order (the variations might be in the order of 5%). A bigger effect is the variation of the analog switches in the front of the capacitors, which is about 15%. So the actual bandwidth each cell sees varies by maybe 20% (given by the R and the C), but this comes only into play when sampling steep edges.

Stefan

|

Great to know this! Thanks~

Jinhong

|

Hi Dr. Stefan,

So the sampling capacitors store the input voltage instead of the charge. What about the readout circuits? I saw there is a buffer followed each sampling capacitor. Do you buffer the charge (like a charge sensitive amplifier) or the voltage? From Fig.12, 14 in datasheet, it seems most probably the readout is a charging or discharging of a capacitor. Could you please add some comments on this?

Cheers,

Jinhong |

|

214

|

Thu Dec 27 18:15:14 2012 |

Jinhong Wang | variation of sampling capacitors |

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan,

A quick question, what is the typical variation of the sampling capacitors in DRS4? Will this variation be significant to affect your sampling result?

Best,

Jinhong

|

The capacitors sample the input voltage, not the charge, so the actual size of the capacitors does not matter on first order (the variations might be in the order of 5%). A bigger effect is the variation of the analog switches in the front of the capacitors, which is about 15%. So the actual bandwidth each cell sees varies by maybe 20% (given by the R and the C), but this comes only into play when sampling steep edges.

Stefan

|

Great to know this! Thanks~

Jinhong |

|

213

|

Thu Dec 27 09:49:17 2012 |

Stefan Ritt | variation of sampling capacitors |

| Jinhong Wang wrote: |

|

Hi Stefan,

A quick question, what is the typical variation of the sampling capacitors in DRS4? Will this variation be significant to affect your sampling result?

Best,

Jinhong

|

The capacitors sample the input voltage, not the charge, so the actual size of the capacitors does not matter on first order (the variations might be in the order of 5%). A bigger effect is the variation of the analog switches in the front of the capacitors, which is about 15%. So the actual bandwidth each cell sees varies by maybe 20% (given by the R and the C), but this comes only into play when sampling steep edges.

Stefan |

|

212

|

Thu Dec 27 00:12:12 2012 |

Jinhong Wang | variation of sampling capacitors | Hi Stefan,

A quick question, what is the typical variation of the sampling capacitors in DRS4? Will this variation be significant to affect your sampling result?

Best,

Jinhong |

|

211

|

Fri Dec 14 21:49:29 2012 |

Stefan Ritt | EVM rev4 board trigger change and drs_example |

| Martin Petriska wrote: |

|

I switched from rev 3 to rev 4 board, but have some problems with triggering, board is now waiting for trigger (rev.3 is working). How to do in drs_exam.cpp for example triggering on Ch0 && CH1 ?

Software 4.0.0, windows version.

Here is old trigger initialisation:

b->EnableTrigger(0,1);

b->SetTriggerSource(0);

b->SetTriggerLevel(0.25, false);

b->SetTriggerDelayNs(0);

Btw. Is it possible to set up different trigger Levels for each channel ?

(If there is some interest here is my code in Qt, still aplha) http://sourceforge.net/p/qtpals/code

|

Sorry the late reply.

In V4, triggering has changed. You can trigger now on an OR or AND of channels. Therefore you have to supply a bitmask, where the 1st bit = CH1, 2nd bit = CH2 and so on. Have a look at the most recent drs_exam. It contains code:

/* use following lines to enable hardware trigger on CH1 at 50 mV positive edge */

if (b->GetBoardType() == 8) { // Evaluaiton Board V4

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

} else { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

b->SetTriggerSource(0); // use CH1 as source

}

So if you want CH1 && CH2, you look at the source code of SetTriggerSource. It contains

// Set trigger configuration

// OR 0=CH1, 1=CH2, 2=CH3, 3=CH4, 4=EXT

// AND 8=CH1, 9=CH2, 10=CH3, 11=CH4, 12=EXT

So an AND between CH1 and CH2 needs a

b->SetTriggerSource(1<<8 | 1<<9);

Your code looks interesting. Do you have a screenshot or can you explain what it does? |

|

210

|

Fri Dec 14 10:07:54 2012 |

Evgeni | DRS-4 trigger |

| Stefan Ritt wrote: |

|

| Evgeni wrote: |

|

| Stefan Ritt wrote: |

|

| Evgeni wrote: |

|

How to configure DRS oscilloscope for the oscillations with an amplitude greater than the value of the exposed

in the trigger (internal).

|

Sorry, I don't understand that question. The DRS4 Evaluation board input signal range is 1V. If you have larger signals, you have to attenuante them externally.

/Stefan

|

Can I adjust the internal trigger DRS oscilloscope for signal extraction 0.5 volts (for example) from any of the four channels. In our case, there is a lot of noise with low amplitude, which must be removed during the registration. We need to record the individual pulses of higher amplitude than the noise. So we want to use the internal trigger DRS oscilloscope to cut this noise by setting up its threshold amplitude noise.

|

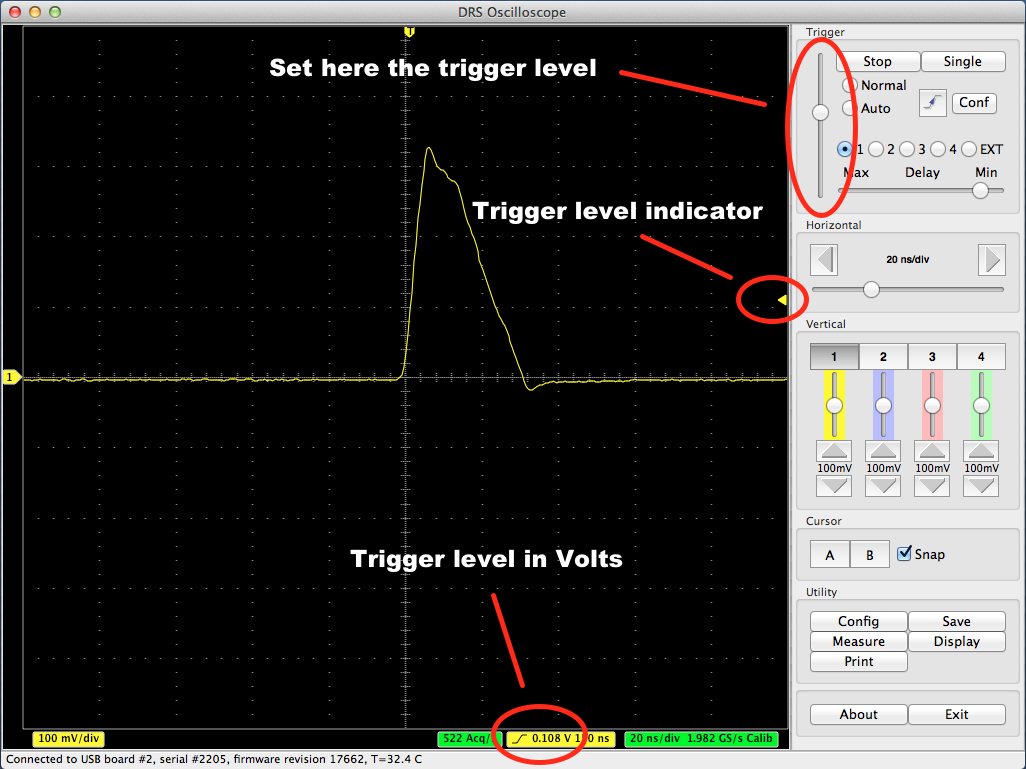

Sure, you can set the trigger level with the vertical slider (see attached figure). The trigger level works form -0.5V to +0.5V. Just like with a normal oscilloscope. I thought this would be obvious...

|

That's it? Thank you for your comprehensive answer. |

|

209

|

Fri Dec 14 10:07:14 2012 |

Evgeni | DRS-4 trigger |

| Evgeni wrote: |

|

How to configure DRS oscilloscope for the oscillations with an amplitude greater than the value of the exposed

in the trigger (internal).

|

|

|

208

|

Fri Dec 14 08:42:53 2012 |

Stefan Ritt | DRS-4 trigger |

| Evgeni wrote: |

|

| Stefan Ritt wrote: |

|

| Evgeni wrote: |

|

How to configure DRS oscilloscope for the oscillations with an amplitude greater than the value of the exposed

in the trigger (internal).

|

Sorry, I don't understand that question. The DRS4 Evaluation board input signal range is 1V. If you have larger signals, you have to attenuante them externally.

/Stefan

|

Can I adjust the internal trigger DRS oscilloscope for signal extraction 0.5 volts (for example) from any of the four channels. In our case, there is a lot of noise with low amplitude, which must be removed during the registration. We need to record the individual pulses of higher amplitude than the noise. So we want to use the internal trigger DRS oscilloscope to cut this noise by setting up its threshold amplitude noise.

|

Sure, you can set the trigger level with the vertical slider (see attached figure). The trigger level works form -0.5V to +0.5V. Just like with a normal oscilloscope. I thought this would be obvious... |

| Attachment 1: DRSOsc.png

|

|

|

207

|

Thu Dec 13 19:49:47 2012 |

Evgeni | DRS-4 trigger |

| Stefan Ritt wrote: |

|

| Evgeni wrote: |

|

How to configure DRS oscilloscope for the oscillations with an amplitude greater than the value of the exposed

in the trigger (internal).

|

Sorry, I don't understand that question. The DRS4 Evaluation board input signal range is 1V. If you have larger signals, you have to attenuante them externally.

/Stefan

|

Can I adjust the internal trigger DRS oscilloscope for signal extraction 0.5 volts (for example) from any of the four channels. In our case, there is a lot of noise with low amplitude, which must be removed during the registration. We need to record the individual pulses of higher amplitude than the noise. So we want to use the internal trigger DRS oscilloscope to cut this noise by setting up its threshold amplitude noise.

|

|

206

|

Thu Dec 13 12:14:35 2012 |

Stefan Ritt | DRS-4 trigger |

| Evgeni wrote: |

|

How to configure DRS oscilloscope for the oscillations with an amplitude greater than the value of the exposed

in the trigger (internal).

|

Sorry, I don't understand that question. The DRS4 Evaluation board input signal range is 1V. If you have larger signals, you have to attenuante them externally.

/Stefan |

|

205

|

Thu Dec 13 12:03:29 2012 |

Evgeni | DRS-4 trigger | How to configure DRS oscilloscope for the oscillations with an amplitude greater than the value of the exposed

in the trigger (internal). |

|

204

|

Thu Dec 6 09:23:36 2012 |

Martin Petriska | EVM rev4 board trigger change and drs_example | I switched from rev 3 to rev 4 board, but have some problems with triggering, board is now waiting for trigger (rev.3 is working). How to do in drs_exam.cpp for example triggering on Ch0 && CH1 ?

Software 4.0.0, windows version.

Here is old trigger initialisation:

b->EnableTrigger(0,1);

b->SetTriggerSource(0);

b->SetTriggerLevel(0.25, false);

b->SetTriggerDelayNs(0);

Btw. Is it possible to set up different trigger Levels for each channel ?

(If there is some interest here is my code in Qt, still aplha) http://sourceforge.net/p/qtpals/code |

|

203

|

Tue Dec 4 09:55:43 2012 |

Stefan Ritt | Question of drs4 using |

| Zhongwei Du wrote: |

|

| Stefan Ritt wrote: |

|

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan

|

"Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. "

In this process , should i config any registers( WSR,WCR,CR ) ?

|

After power-up reset, these registers are all set to "1", which should be ok to start.

BTW, Jinhong Wang <wangjinh@mail.ustc.edu.cn> from your institute hast the chip correctly working. Maybe he can help you in a more direct way than I can.

|

|

202

|

Tue Dec 4 09:50:11 2012 |

Zhongwei Du | Question of drs4 using |

| Stefan Ritt wrote: |

|

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan

|

"Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. "

In this process , should i config any registers( WSR,WCR,CR ) ? |

|

201

|

Tue Dec 4 09:39:44 2012 |

Stefan Ritt | Question of drs4 using |

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan |

|

200

|

Tue Dec 4 09:24:22 2012 |

Zhongwei Du | Question of drs4 using | When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now. |

|

199

|

Mon Dec 3 11:40:35 2012 |

Gyuhee Kim | Another question about using multi boards. |

| Stefan Ritt wrote: |

|

| Gyuhee Kim wrote: |

|

Hi.

I asked about using multi boards some days ago, and I got answer to use external trigger. (Thanks Stefan!)

And here is another question. I made two external triggers and try to acquire coincidence data using two boards. but DRS Oscilloscope program can connect only one board and don`t acquire both of them simultaneously.

So I tried to use two computer for each board separately, but, well, you already know, I failed to acquire because two computers don`t promise to synchronize the two boards acquisition.

Is there any method to solve this problem?

1. I want to acquire coincidence data from the two DRS 4 Evaluation board V4 simultaneosly.

2. I have external trigger to provide the two boards at the same time.

3. How can I get data from the two boards?

Best regards.

Gyuhee.

|

You have to write your own program. DRS Oscilloscope does not (yet) support this. Take drs_exam.cpp as a starting point and try to extend it to two boards. One tricky point is that the external trigger may only fire AFTER the two boards have been read out. So you need some means of re-enabling the external trigger after you read out both boards.

Stefan

|

That`s very bad news for me. I don`t have much time to study & write C programming...

Anyway, Thank you very much Stefan.

Best regards.

Gyuhee. |

|

198

|

Mon Dec 3 09:18:09 2012 |

Stefan Ritt | Another question about using multi boards. |

| Gyuhee Kim wrote: |

|

Hi.

I asked about using multi boards some days ago, and I got answer to use external trigger. (Thanks Stefan!)

And here is another question. I made two external triggers and try to acquire coincidence data using two boards. but DRS Oscilloscope program can connect only one board and don`t acquire both of them simultaneously.

So I tried to use two computer for each board separately, but, well, you already know, I failed to acquire because two computers don`t promise to synchronize the two boards acquisition.

Is there any method to solve this problem?

1. I want to acquire coincidence data from the two DRS 4 Evaluation board V4 simultaneosly.

2. I have external trigger to provide the two boards at the same time.

3. How can I get data from the two boards?

Best regards.

Gyuhee.

|

You have to write your own program. DRS Oscilloscope does not (yet) support this. Take drs_exam.cpp as a starting point and try to extend it to two boards. One tricky point is that the external trigger may only fire AFTER the two boards have been read out. So you need some means of re-enabling the external trigger after you read out both boards.

Stefan |

|