| ID |

Date |

Author |

Subject |

|

638

|

Thu Nov 16 02:55:44 2017 |

Diego Yankelevich | Averaging capabilities | The Display window in the Oscilloscope software shows averaging capabilites but I have not been able to activate these. Is it possible to activate averaging with the existing oscilloscope software? Thanks |

|

644

|

Wed Nov 22 14:52:31 2017 |

Stefan Ritt | Averaging capabilities | This feature is not yet implemented. The (disabled) software swtich is more like a kind of a reminder to myself to work on that one day...

| Diego Yankelevich wrote: |

|

The Display window in the Oscilloscope software shows averaging capabilites but I have not been able to activate these. Is it possible to activate averaging with the existing oscilloscope software? Thanks

|

|

|

17

|

Mon Oct 19 09:06:43 2009 |

Jinhong Wang | BIAS Pin of DRS4 | Dear Mr. Stefan Ritt.

Thank u for your timely response on "DSR4 Full Readout Mode", I received it from Professor Qi An, who is my PhD supervisor.

I am currently going through the DRS4 datasheet. Well, can you give some specification on the usage of "BIAS" pin of DRS4? It is just metioned in the datasheet as bias of internal buffer. What is the internal buffer exactly reffered to here? The MUXOUT buffer of channel 8 or else? Does it have some relationship to O_OFS? I mean, if the reference voltage to BIAS is changed, how will the output be influenced?

Looking forward to hearing from you soon.

Jinhong Wang

Fast Electronics LAB. of University of Science and Technology of China. |

|

18

|

Mon Oct 19 09:13:00 2009 |

Stefan Ritt | BIAS Pin of DRS4 |

| Jinhong Wang wrote: |

|

Dear Mr. Stefan Ritt.

Thank u for your timely response on "DSR4 Full Readout Mode", I received it from Professor Qi An, who is my PhD supervisor.

I am currently going through the DRS4 datasheet. Well, can you give some specification on the usage of "BIAS" pin of DRS4? It is just metioned in the datasheet as bias of internal buffer. What is the internal buffer exactly reffered to here? The MUXOUT buffer of channel 8 or else? Does it have some relationship to O_OFS? I mean, if the reference voltage to BIAS is changed, how will the output be influenced?

Looking forward to hearing from you soon.

Jinhong Wang

Fast Electronics LAB. of University of Science and Technology of China.

|

"internal buffers" are all internal operational amplifiers in the DRS4 chip. Every OPAMP needs a bias (just look it up in any electronics textbook), which determines the linearity and the speed of the OPAMP. When designing DRS4, I was not sure if the required BIAS voltage changes over time, or between chips, so I made it available at a pin, which is a common technique in chip design. But it turns out now that this voltage is not very critical, so just keeping the pin open will work in most cases. |

|

62

|

Fri Apr 9 17:14:45 2010 |

Hao Huan | Baseline Variation In Data | Hi Stefan,

when I sample a constant input with the DRS 4 chip, there was a baseline variation showing up as a saw-tooth pattern which grows with the absolute value of the differential input. Do you think this is the kind of baseline variation mentioned in the evaluation board manual, i.e. coming from clock jitter in ADC sampling?

Thanks a lot!

|

|

65

|

Tue Apr 13 13:56:07 2010 |

Stefan Ritt | Baseline Variation In Data |

| Hao Huan wrote: |

|

Hi Stefan,

when I sample a constant input with the DRS 4 chip, there was a baseline variation showing up as a saw-tooth pattern which grows with the absolute value of the differential input. Do you think this is the kind of baseline variation mentioned in the evaluation board manual, i.e. coming from clock jitter in ADC sampling?

Thanks a lot!

|

Please post an oscilloscope screenshot here and I can tell you. |

|

517

|

Wed Apr 27 20:04:12 2016 |

Abaz Kryemadhi | Best settings for time measurements | I am studing some pulses that are about 200-300 ns wide and a rise time of few ns, which settings would be best for coincidence time measurements?

In some preliminary work I found for 700 MegaS the time measurement is better without time calibration (in -0.05 to 1V) rather than with time calibration in -0.5 to 0.5, my pulses are about 60 mV. Is it expected that always with time calibration time accuracy would be better or depends?

Also I use this code snippet to find time for channel 1 and the same idea for chan. 2.

// find peak in channel 1 above threshold

for (i=0 ; i<1022 ; i++)

if (waveform[0][i] < threshold1 && waveform[0][i+1] >= threshold1) {

tt1 = (threshold1-waveform[0][i])/(waveform[0][i+1]-waveform[0][i])*(time[0][i+1]-time[0][i])+time[0][i];

break;

}

Thanks!

Abaz |

|

518

|

Thu Apr 28 15:46:34 2016 |

Stefan Ritt | Best settings for time measurements | The DRS4 chip has been designed to work best at high sampling speeds. At 700 MSPS, the chip is at it's limit and timing is very poorr (ns?). In order to get good timing, run it at least at 2 GSPS.

Stefan

| Abaz Kryemadhi wrote: |

|

I am studing some pulses that are about 200-300 ns wide and a rise time of few ns, which settings would be best for coincidence time measurements?

In some preliminary work I found for 700 MegaS the time measurement is better without time calibration (in -0.05 to 1V) rather than with time calibration in -0.5 to 0.5, my pulses are about 60 mV. Is it expected that always with time calibration time accuracy would be better or depends?

Also I use this code snippet to find time for channel 1 and the same idea for chan. 2.

// find peak in channel 1 above threshold

for (i=0 ; i<1022 ; i++)

if (waveform[0][i] < threshold1 && waveform[0][i+1] >= threshold1) {

tt1 = (threshold1-waveform[0][i])/(waveform[0][i+1]-waveform[0][i])*(time[0][i+1]-time[0][i])+time[0][i];

break;

}

Thanks!

Abaz

|

|

|

557

|

Thu Nov 10 04:41:24 2016 |

Abhishek Rajput | Break Statements in DRS4 Binary to ROOT Macro | Hello,

I recently modified the binary to ROOT convertor written by Stefan (https://midas.psi.ch/elogs/DRS4+Forum/361) so it can decode data taken with any channel or set of channels on the DRS4. In the process of testing this modifed version for data taken on all 4 channels, I encountered problems with decoding some of the event data. More specifically, upon hitting a certain event in some channel, the histograms for that channel would no longer be filled and the histograms for subsequent channels would not be filled with any event at all.

After considerable bug hunting, I discovered the source of this problem was due to the break statement in the following code extract from the ROOT to binary macro:

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < 1)

break;

For some events apparently, the event header fails to be read properly (fread line returns 0 in this case). Moreover, when I used the feof and ferror functions on a particular file I was testing, the feof function returned a value of 1.

So my questions deal with two scenarios.

Firstly, in the event of an fread error, is a break statement is necessary? Is it not possible to skip the voltage data for those events whose event header fails to be read properly? Or is it the case that when some "corrupted" event header is encountered, all waveform data subsequent to that event is likewise corrupted? If the former is the case, is it advisable to replace the break condition with an fseek line that advances the position indicator of the stream by an additional 2052*n_channels + 32 bytes (in accordance with the binary file specifications of page 25 on the DRS4 manual) so that the next set of voltage data can be read?

Secondly, in the case of an end of file error, does there exist any possible solution? Or is such an error an indication of a faulty drs4 channel or corrupted binary file?

Any help with the aforementioned issues would be greatly appreciated.

Abhishek

|

|

558

|

Thu Nov 10 09:56:04 2016 |

Stefan Ritt | Break Statements in DRS4 Binary to ROOT Macro | Hi,

fread() returns the number of bytes read and zero (I believe) if there is an end of file. So this break statement is a simple end-of-file test. There might be other erros such as hard disk failures, but these are extremely rare.

If course the file should not end in the middle of an event header. If it does, it means the file is corrupted and truncated, and we should not continue to read that file, that's why there is the break. The internal file is just a series of bytes, it does not know about the event header, so there will be no "error" if we have for example a missing event header but a voltage array. To be correct, the code should actually read

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < sizeof(eh))

break;

Hope this helps,

Stefan

| Abhishek Rajput wrote: |

|

Hello,

I recently modified the binary to ROOT convertor written by Stefan (https://midas.psi.ch/elogs/DRS4+Forum/361) so it can decode data taken with any channel or set of channels on the DRS4. In the process of testing this modifed version for data taken on all 4 channels, I encountered problems with decoding some of the event data. More specifically, upon hitting a certain event in some channel, the histograms for that channel would no longer be filled and the histograms for subsequent channels would not be filled with any event at all.

After considerable bug hunting, I discovered the source of this problem was due to the break statement in the following code extract from the ROOT to binary macro:

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < 1)

break;

For some events apparently, the event header fails to be read properly (fread line returns 0 in this case). Moreover, when I used the feof and ferror functions on a particular file I was testing, the feof function returned a value of 1.

So my questions deal with two scenarios.

Firstly, in the event of an fread error, is a break statement is necessary? Is it not possible to skip the voltage data for those events whose event header fails to be read properly? Or is it the case that when some "corrupted" event header is encountered, all waveform data subsequent to that event is likewise corrupted? If the former is the case, is it advisable to replace the break condition with an fseek line that advances the position indicator of the stream by an additional 2052*n_channels + 32 bytes (in accordance with the binary file specifications of page 25 on the DRS4 manual) so that the next set of voltage data can be read?

Secondly, in the case of an end of file error, does there exist any possible solution? Or is such an error an indication of a faulty drs4 channel or corrupted binary file?

Any help with the aforementioned issues would be greatly appreciated.

Abhishek

|

|

|

560

|

Thu Nov 10 19:24:52 2016 |

Abhishek Rajput | Break Statements in DRS4 Binary to ROOT Macro | Hello,

I am wondering why the code should be changed to i < sizeof(eh), since doesn't fread(&eh,sizeof(eh),1,f) return 1 in this scenario? I've confirmed with a cout statement that this is the case, so this break condition will therefore always trigger as sizeof(eh) is 32 bytes.

Either way, I believe I figured out my problem. In my revised version of your code, I had two nested loops, the outer one being a loop over the channels and the inner one being a loop over the events. However, I really should have been doing the reverse considering the binary structure of the file. Otherwise, the end of the file will be reached for only a single iteration of the channel loop if I choose to loop through all the events in the data file.

Once I modified the code to have the outer loop be over all the events and the inner one be over all the channels, I no longer suffered from breaks in the loops.

Many thanks for your assistance.

Abhishek

| Stefan Ritt wrote: |

|

Hi,

fread() returns the number of bytes read and zero (I believe) if there is an end of file. So this break statement is a simple end-of-file test. There might be other erros such as hard disk failures, but these are extremely rare.

If course the file should not end in the middle of an event header. If it does, it means the file is corrupted and truncated, and we should not continue to read that file, that's why there is the break. The internal file is just a series of bytes, it does not know about the event header, so there will be no "error" if we have for example a missing event header but a voltage array. To be correct, the code should actually read

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < sizeof(eh))

break;

Hope this helps,

Stefan

| Abhishek Rajput wrote: |

|

Hello,

I recently modified the binary to ROOT convertor written by Stefan (https://midas.psi.ch/elogs/DRS4+Forum/361) so it can decode data taken with any channel or set of channels on the DRS4. In the process of testing this modifed version for data taken on all 4 channels, I encountered problems with decoding some of the event data. More specifically, upon hitting a certain event in some channel, the histograms for that channel would no longer be filled and the histograms for subsequent channels would not be filled with any event at all.

After considerable bug hunting, I discovered the source of this problem was due to the break statement in the following code extract from the ROOT to binary macro:

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < 1)

break;

For some events apparently, the event header fails to be read properly (fread line returns 0 in this case). Moreover, when I used the feof and ferror functions on a particular file I was testing, the feof function returned a value of 1.

So my questions deal with two scenarios.

Firstly, in the event of an fread error, is a break statement is necessary? Is it not possible to skip the voltage data for those events whose event header fails to be read properly? Or is it the case that when some "corrupted" event header is encountered, all waveform data subsequent to that event is likewise corrupted? If the former is the case, is it advisable to replace the break condition with an fseek line that advances the position indicator of the stream by an additional 2052*n_channels + 32 bytes (in accordance with the binary file specifications of page 25 on the DRS4 manual) so that the next set of voltage data can be read?

Secondly, in the case of an end of file error, does there exist any possible solution? Or is such an error an indication of a faulty drs4 channel or corrupted binary file?

Any help with the aforementioned issues would be greatly appreciated.

Abhishek

|

|

|

|

562

|

Thu Nov 10 22:07:40 2016 |

Stefan Ritt | Break Statements in DRS4 Binary to ROOT Macro | You're right, fread() return the number of objects read, so indeed it should be one if successful.

| Abhishek Rajput wrote: |

|

Hello,

I am wondering why the code should be changed to i < sizeof(eh), since doesn't fread(&eh,sizeof(eh),1,f) return 1 in this scenario? I've confirmed with a cout statement that this is the case, so this break condition will therefore always trigger as sizeof(eh) is 32 bytes.

Either way, I believe I figured out my problem. In my revised version of your code, I had two nested loops, the outer one being a loop over the channels and the inner one being a loop over the events. However, I really should have been doing the reverse considering the binary structure of the file. Otherwise, the end of the file will be reached for only a single iteration of the channel loop if I choose to loop through all the events in the data file.

Once I modified the code to have the outer loop be over all the events and the inner one be over all the channels, I no longer suffered from breaks in the loops.

Many thanks for your assistance.

Abhishek

| Stefan Ritt wrote: |

|

Hi,

fread() returns the number of bytes read and zero (I believe) if there is an end of file. So this break statement is a simple end-of-file test. There might be other erros such as hard disk failures, but these are extremely rare.

If course the file should not end in the middle of an event header. If it does, it means the file is corrupted and truncated, and we should not continue to read that file, that's why there is the break. The internal file is just a series of bytes, it does not know about the event header, so there will be no "error" if we have for example a missing event header but a voltage array. To be correct, the code should actually read

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < sizeof(eh))

break;

Hope this helps,

Stefan

| Abhishek Rajput wrote: |

|

Hello,

I recently modified the binary to ROOT convertor written by Stefan (https://midas.psi.ch/elogs/DRS4+Forum/361) so it can decode data taken with any channel or set of channels on the DRS4. In the process of testing this modifed version for data taken on all 4 channels, I encountered problems with decoding some of the event data. More specifically, upon hitting a certain event in some channel, the histograms for that channel would no longer be filled and the histograms for subsequent channels would not be filled with any event at all.

After considerable bug hunting, I discovered the source of this problem was due to the break statement in the following code extract from the ROOT to binary macro:

for (n=0 ; n<5 ; n++) {

// read event header

i = fread(&eh, sizeof(eh), 1, f);

if (i < 1)

break;

For some events apparently, the event header fails to be read properly (fread line returns 0 in this case). Moreover, when I used the feof and ferror functions on a particular file I was testing, the feof function returned a value of 1.

So my questions deal with two scenarios.

Firstly, in the event of an fread error, is a break statement is necessary? Is it not possible to skip the voltage data for those events whose event header fails to be read properly? Or is it the case that when some "corrupted" event header is encountered, all waveform data subsequent to that event is likewise corrupted? If the former is the case, is it advisable to replace the break condition with an fseek line that advances the position indicator of the stream by an additional 2052*n_channels + 32 bytes (in accordance with the binary file specifications of page 25 on the DRS4 manual) so that the next set of voltage data can be read?

Secondly, in the case of an end of file error, does there exist any possible solution? Or is such an error an indication of a faulty drs4 channel or corrupted binary file?

Any help with the aforementioned issues would be greatly appreciated.

Abhishek

|

|

|

|

|

829

|

Wed Jul 14 14:55:09 2021 |

Mehrpad Monajem | C code to read the 4 channel with external trigger | Hi there,

Recently I bought a 5GSPS evaluation board with 2048 sampling points.

I want to read 4 inputs of the evaluation bord ar 5 GSPS or 2.5GSP and use an external trigger.

I've checked your website and download drs-5.0.5 which contains the source code in C. It seems that the file drs_exam.cpp can do what I am looking for.

So far I could make and compile the project in Linux Ubuntu, but I couldn't compile it in Windows 10. I've used Cygwin64 to compile the project in windows 10.

I have the following questions:

1- Since I only need to compile the drs_exam.cpp file, could please help me with how can I compile it directly(without making the entire project). Or tell me which version of Wxwidget and libusb I have to install.

2- If you have any sample code that can read 4 inputs with an external trigger, please tell me where can I find it.

In the end, I want to write a wrapper on this C file(which returns digitized data) and run it from my python program. Thank you in advance.

Best regards,

Mehrpad

|

|

830

|

Mon Aug 9 12:50:31 2021 |

Stefan Ritt | C code to read the 4 channel with external trigger | Sorry the late reply, I was on vacation.

Here are some answers:

1. I'm sorry I can't help much here, since I currently don't have a Windows 10 computer here to compile any code. I moved now completely to MacOSX, being very similar to Linux. I'm not allowed to run a Windows 7 computer any more for security reasons. Last time this worked for me was with Wxwidget version 3.0 and libusb 1.0, but I guess libusb is not critical so you can use a newer version. If you just compile drs_exam.cpp, you don't need any Wxwidget library. That one is only used for the oscilloscope program.

2. The program drs_exam_2048.cpp is meant to read channels in 2048-bin mode.

3. To adjust the delay between the trigger and the readout, use the function b->SetTriggerDelayNs(xxx)

Best,

Stefan

| Mehrpad Monajem wrote: |

|

Hi there,

Recently I bought a 5GSPS evaluation board with 2048 sampling points.

I want to read 4 inputs of the evaluation bord ar 5 GSPS or 2.5GSP and use an external trigger.

I've checked your website and download drs-5.0.5 which contains the source code in C. It seems that the file drs_exam.cpp can do what I am looking for.

So far I could make and compile the project in Linux Ubuntu, but I couldn't compile it in Windows 10. I've used Cygwin64 to compile the project in windows 10.

I have the following questions:

1- Since I only need to compile the drs_exam.cpp file, could please help me with how can I compile it directly(without making the entire project). Or tell me which version of Wxwidget and libusb I have to install.

2- If you have any sample code that can read 4 inputs with an external trigger, please tell me where can I find it.

In the end, I want to write a wrapper on this C file(which returns digitized data) and run it from my python program. Thank you in advance.

Best regards,

Mehrpad

|

|

|

831

|

Tue Aug 10 13:57:09 2021 |

Mehrpad Monajem | C code to read the 4 channel with external trigger | Thank you for the reply.

In the version that I have, I cannot find drs_exam_2048.cpp file. Could you please send me the link to download the software folder, which contain this file.

Best,

Mehrpad

| Stefan Ritt wrote: |

|

Sorry the late reply, I was on vacation.

Here are some answers:

1. I'm sorry I can't help much here, since I currently don't have a Windows 10 computer here to compile any code. I moved now completely to MacOSX, being very similar to Linux. I'm not allowed to run a Windows 7 computer any more for security reasons. Last time this worked for me was with Wxwidget version 3.0 and libusb 1.0, but I guess libusb is not critical so you can use a newer version. If you just compile drs_exam.cpp, you don't need any Wxwidget library. That one is only used for the oscilloscope program.

2. The program drs_exam_2048.cpp is meant to read channels in 2048-bin mode.

3. To adjust the delay between the trigger and the readout, use the function b->SetTriggerDelayNs(xxx)

Best,

Stefan

| Mehrpad Monajem wrote: |

|

Hi there,

Recently I bought a 5GSPS evaluation board with 2048 sampling points.

I want to read 4 inputs of the evaluation bord ar 5 GSPS or 2.5GSP and use an external trigger.

I've checked your website and download drs-5.0.5 which contains the source code in C. It seems that the file drs_exam.cpp can do what I am looking for.

So far I could make and compile the project in Linux Ubuntu, but I couldn't compile it in Windows 10. I've used Cygwin64 to compile the project in windows 10.

I have the following questions:

1- Since I only need to compile the drs_exam.cpp file, could please help me with how can I compile it directly(without making the entire project). Or tell me which version of Wxwidget and libusb I have to install.

2- If you have any sample code that can read 4 inputs with an external trigger, please tell me where can I find it.

In the end, I want to write a wrapper on this C file(which returns digitized data) and run it from my python program. Thank you in advance.

Best regards,

Mehrpad

|

|

|

|

173

|

Wed Aug 1 17:42:32 2012 |

Mayank S. Rajguru | Calculation of loop filter parameters (R,C1and C1) for 1 GHz | Hi,

we are planning to use the DRS4 in our board for 1 GHz sampling and digitization.

I have seen in the data sheet that "For the PLL to work, an external loop filter is required. This filter ensures quick locking and stable operation at the desired sampling frequency".

What formula do you use to calculate the values of R, C1 and C2?

Can we use the same given value for different frequencies?

Thanks,

Mayak |

|

174

|

Mon Aug 6 02:44:00 2012 |

Stefan Ritt | Calculation of loop filter parameters (R,C1and C1) for 1 GHz |

| Mayank S. Rajguru wrote: |

|

Hi,

we are planning to use the DRS4 in our board for 1 GHz sampling and digitization.

I have seen in the data sheet that "For the PLL to work, an external loop filter is required. This filter ensures quick locking and stable operation at the desired sampling frequency".

What formula do you use to calculate the values of R, C1 and C2?

Can we use the same given value for different frequencies?

Thanks,

Mayak

|

I never worked out an exact formula for the parameters. It also depends if you want a fast locking time, or a low phase jitter of the PLL. A good starting point are the values from the evaluation board:

R = 130 Ohm

C1 = 4.7 nF

C2 = 1 uF

They should work from 800 MHz to 5 GHz.

- Stefan |

|

350

|

Thu May 29 04:22:43 2014 |

Toshihiro Nonaka | CalibrationWaveform | I'm writing the drs_exam.cpp to use multi-boards(v3, firmware:4.0.0), and taking data succeeded. But I have several questions about function written in DRS.cpp.

- I wrote following code in drs_exam.cpp to set input range -0.4~0.6

b1->SetInputRange(0.1);

And the 100mV offset appeared(I attached a picture). I think this is due to the voltage calibration isn't done.(Calibrated to -0.5~0.5mV in DRS Oscilloscope)

If so, could you show me a simple usage of "CalibrationWaveform()" function in DRS.cpp? (or other function?)

2. Although this question might be the almost same with above, is there any way to execute voltage and timing calibration in drs_exam.cpp?

Now I start DAQ by executing drs_exam.cpp after I execute voltage and timing calibration to each board by DRS Oscilloscope program.

3. Which command is right to use external trigger?

b1->SetTriggerSource(4); or b1->SetTriggerSource(1<<4);

Best regards,

Toshihiro Nonaka |

| Attachment 1: offset.png

|

|

|

355

|

Thu Jun 12 17:16:13 2014 |

Stefan Ritt | CalibrationWaveform |

| Toshihiro Nonaka wrote: |

|

I'm writing the drs_exam.cpp to use multi-boards(v3, firmware:4.0.0), and taking data succeeded. But I have several questions about function written in DRS.cpp.

- I wrote following code in drs_exam.cpp to set input range -0.4~0.6

b1->SetInputRange(0.1);

And the 100mV offset appeared(I attached a picture). I think this is due to the voltage calibration isn't done.(Calibrated to -0.5~0.5mV in DRS Oscilloscope)

If so, could you show me a simple usage of "CalibrationWaveform()" function in DRS.cpp? (or other function?)

2. Although this question might be the almost same with above, is there any way to execute voltage and timing calibration in drs_exam.cpp?

Now I start DAQ by executing drs_exam.cpp after I execute voltage and timing calibration to each board by DRS Oscilloscope program.

3. Which command is right to use external trigger?

b1->SetTriggerSource(4); or b1->SetTriggerSource(1<<4);

Best regards,

Toshihiro Nonaka

|

1. b->CalibrateVolt(NULL);

2. see 1.

3. For the V3 boards use b->SetTriggerSource(4), for V4 and V5 boards, use b->SetTriggerSource(1<<4). I had to change that because from V4 on we can have logical combinations between channels (like channel 1 AND channel 2).

Best regards,

Stefan |

|

862

|

Sat Feb 12 13:06:56 2022 |

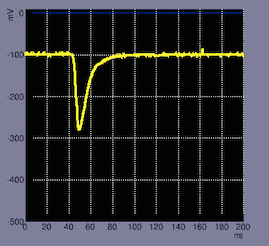

Matias Senger | Cannot trigger on pulses, have to trigger on undershoot | I am using the DRS4 board trying to measure pulses produced by an LGAD. I have no prior experience with this board, have just installed the `drsosc` application and am exploring. I am experiencing some strange trigger behavior. Consider the following screenshot:

Here nothing is strange, the board is triggering on the undershoot and it is working fine, I can trigger on rising/falling edge, different levels, etc.

Now, the strange thing is that if I pull the trigger up to trigger on the pulse itself it stops triggering:

I have tried many different setups for the trigger (rising, falling edge, different levels, etc) and nothing works. In the undershoot, everything works.

I have tried with the internal test signal and it works fine:

What could be the problem?

I have run the voltage and time calibrations as suggested in the manual. |

|