| ID |

Date |

Author |

Subject |

|

298

|

Mon Oct 21 14:43:21 2013 |

Stephane Debieux | DRS4 analog outputs - interfacing DRS4 to AD9222 ADC | Hi,

I wish to interface the DRS4 with the 8-channel ADC AD9222 (or AD9637).

I'm reading from the DRS4 datasheet that "the analog output of the DRS4 chip has been designed to match directly the input of the AD9222". OUT+ output of DRS4 is in the range from 0.8V to 1.8V and OUT- output is shifted by the voltage applied to the O-OFS pin.

The span of the AD9222 ADC core is defined by REFT and REFB which are resp. 1.4V and 0.4V in a typical case (AVDD=1.8V, VREF=1V). My understanding is that the ADC analog inputs must be within the voltage range defined by REFT and REFB and so I don't quite see how this matches the DRS4 outputs.

Can we use the full-scale range indeed? Do we have to use AC-coupling with mid-supply bias? What is the point I missed?

Thank you for your help.

|

|

377

|

Tue Oct 7 14:09:02 2014 |

Stephane Debieux | USB Microcontroller firmware | Hi,

I'm trying to recompile the USB microcontroller firmware starting from the drs_eval.c file but I'm not able to get a .iic file close to the one provided with the eval board. It seems to me that this drs_eval.iic file does not match the drs_eval.c and drs_eval.hex files or that I'm doing something wrong. Could you please help or give me an explanation.

Thank you.

Stephane

|

|

379

|

Mon Oct 13 17:08:40 2014 |

Stephane Debieux | USB Microcontroller firmware |

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

Hi,

I'm trying to recompile the USB microcontroller firmware starting from the drs_eval.c file but I'm not able to get a .iic file close to the one provided with the eval board. It seems to me that this drs_eval.iic file does not match the drs_eval.c and drs_eval.hex files or that I'm doing something wrong. Could you please help or give me an explanation.

Thank you.

Stephane

|

I did not touch the firmware since a couple of years, but I can confirm that the drs_eval.iic is the correct firmware file, since we use this one on all of our boards. To program it, you need the Cypress USB Console. You remove the jumper (to detach the EEPROM), then power the board (which then boots from the internal memory), connect to the board via the Cypress console, the put back the jumper while the board is running, then program the file into the EEPROM.

Best,

Stefan

|

Thank you Stefan.

Would that be possible to get the corresponding drs_eval.c source file since I'm assuming the one provided with the eval board is not the right one?

Thank you.

Stephane |

|

381

|

Tue Oct 14 16:21:07 2014 |

Stephane Debieux | USB Microcontroller firmware |

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

Hi,

I'm trying to recompile the USB microcontroller firmware starting from the drs_eval.c file but I'm not able to get a .iic file close to the one provided with the eval board. It seems to me that this drs_eval.iic file does not match the drs_eval.c and drs_eval.hex files or that I'm doing something wrong. Could you please help or give me an explanation.

Thank you.

Stephane

|

I did not touch the firmware since a couple of years, but I can confirm that the drs_eval.iic is the correct firmware file, since we use this one on all of our boards. To program it, you need the Cypress USB Console. You remove the jumper (to detach the EEPROM), then power the board (which then boots from the internal memory), connect to the board via the Cypress console, the put back the jumper while the board is running, then program the file into the EEPROM.

Best,

Stefan

|

Thank you Stefan.

Would that be possible to get the corresponding drs_eval.c source file since I'm assuming the one provided with the eval board is not the right one?

Thank you.

Stephane

|

There is only one drs_eval.c version around, and I confirm that it is the one in the distribution. If you use different compiler settings, like optimisations, you might get a different executable file (and thus a .iic file), but the files have the same functionality.

Stefan

|

I'm very sorry to insist but if I take the .hex of the distribution, convert it to .iic using the hex2bix utility, and reprogram the board, I can't read the board correctly (invalid magic number read with drscl for instance). Also, when using the uVision2 project file you provide and compiling the drs_eval.c, I get the same result (i.e. no way to generate a functional .iic file starting from the sources). So, either I'm doing something wrong (and I don't know what) or the drs_eval.c is not the correct one. |

|

383

|

Tue Oct 14 16:34:45 2014 |

Stephane Debieux | USB Microcontroller firmware |

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

Hi,

I'm trying to recompile the USB microcontroller firmware starting from the drs_eval.c file but I'm not able to get a .iic file close to the one provided with the eval board. It seems to me that this drs_eval.iic file does not match the drs_eval.c and drs_eval.hex files or that I'm doing something wrong. Could you please help or give me an explanation.

Thank you.

Stephane

|

I did not touch the firmware since a couple of years, but I can confirm that the drs_eval.iic is the correct firmware file, since we use this one on all of our boards. To program it, you need the Cypress USB Console. You remove the jumper (to detach the EEPROM), then power the board (which then boots from the internal memory), connect to the board via the Cypress console, the put back the jumper while the board is running, then program the file into the EEPROM.

Best,

Stefan

|

Thank you Stefan.

Would that be possible to get the corresponding drs_eval.c source file since I'm assuming the one provided with the eval board is not the right one?

Thank you.

Stephane

|

There is only one drs_eval.c version around, and I confirm that it is the one in the distribution. If you use different compiler settings, like optimisations, you might get a different executable file (and thus a .iic file), but the files have the same functionality.

Stefan

|

I'm very sorry to insist but if I take the .hex of the distribution, convert it to .iic using the hex2bix utility, and reprogram the board, I can't read the board correctly (invalid magic number read with drscl for instance). Also, when using the uVision2 project file you provide and compiling the drs_eval.c, I get the same result (i.e. no way to generate a functional .iic file starting from the sources). So, either I'm doing something wrong (and I don't know what) or the drs_eval.c is not the correct one.

|

And what happens if you program the .iic file from the distribution?

|

It works as expected. |

|

385

|

Tue Oct 14 16:51:37 2014 |

Stephane Debieux | USB Microcontroller firmware |

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

| Stefan Ritt wrote: |

|

| Stephane Debieux wrote: |

|

Hi,

I'm trying to recompile the USB microcontroller firmware starting from the drs_eval.c file but I'm not able to get a .iic file close to the one provided with the eval board. It seems to me that this drs_eval.iic file does not match the drs_eval.c and drs_eval.hex files or that I'm doing something wrong. Could you please help or give me an explanation.

Thank you.

Stephane

|

I did not touch the firmware since a couple of years, but I can confirm that the drs_eval.iic is the correct firmware file, since we use this one on all of our boards. To program it, you need the Cypress USB Console. You remove the jumper (to detach the EEPROM), then power the board (which then boots from the internal memory), connect to the board via the Cypress console, the put back the jumper while the board is running, then program the file into the EEPROM.

Best,

Stefan

|

Thank you Stefan.

Would that be possible to get the corresponding drs_eval.c source file since I'm assuming the one provided with the eval board is not the right one?

Thank you.

Stephane

|

There is only one drs_eval.c version around, and I confirm that it is the one in the distribution. If you use different compiler settings, like optimisations, you might get a different executable file (and thus a .iic file), but the files have the same functionality.

Stefan

|

I'm very sorry to insist but if I take the .hex of the distribution, convert it to .iic using the hex2bix utility, and reprogram the board, I can't read the board correctly (invalid magic number read with drscl for instance). Also, when using the uVision2 project file you provide and compiling the drs_eval.c, I get the same result (i.e. no way to generate a functional .iic file starting from the sources). So, either I'm doing something wrong (and I don't know what) or the drs_eval.c is not the correct one.

|

And what happens if you program the .iic file from the distribution?

|

It works as expected.

|

Then why don't you use the .iic file and forget about the hex and c files? Honestly speaking, I don't remember what source file I compiled a couple of years ago, and it could be that an older file slipped into the repository, but that's all I have. I would have to investigate myself, try to compile and program the c file, do the debugging, and find out what the differences are. But unfortunately I don't have time for that right now. So just stick with the .iic file.

|

Thanks for the help.

I'm not doing this for fun, checking that the source matches the .iic ! I know I could directly use the .iic and forget about the hex and c files.

I just wanted to use your source file as the starting point for my own board, as everybody is doing at the application level. |

|

657

|

Tue Feb 27 13:17:00 2018 |

Steven Block | WIndows Connection problem with drs507 SOLVED | Hello All,

I too have been struggling with trying to get the drs4 (507) to work on my windows machine and I found it to be a problem with the libusb library. My solution is as follows and has worked on multiple PC's. I ran this solution after I first plugged in the drs4 and installed 507.

Go to http://zadig.akeo.ie/ and install the corresponding software.

After that, you will need to plug in the DRS4 to your computer. From there go to ‘Options’, and select ‘List all Devices’.

Finally, choose the DRS4 evaluation board from the list and press install driver and let it run. You should be fine after that.

Best,

Steven |

|

659

|

Tue Feb 27 16:34:26 2018 |

Steven Block | DRS4 Dead times | Hello All,

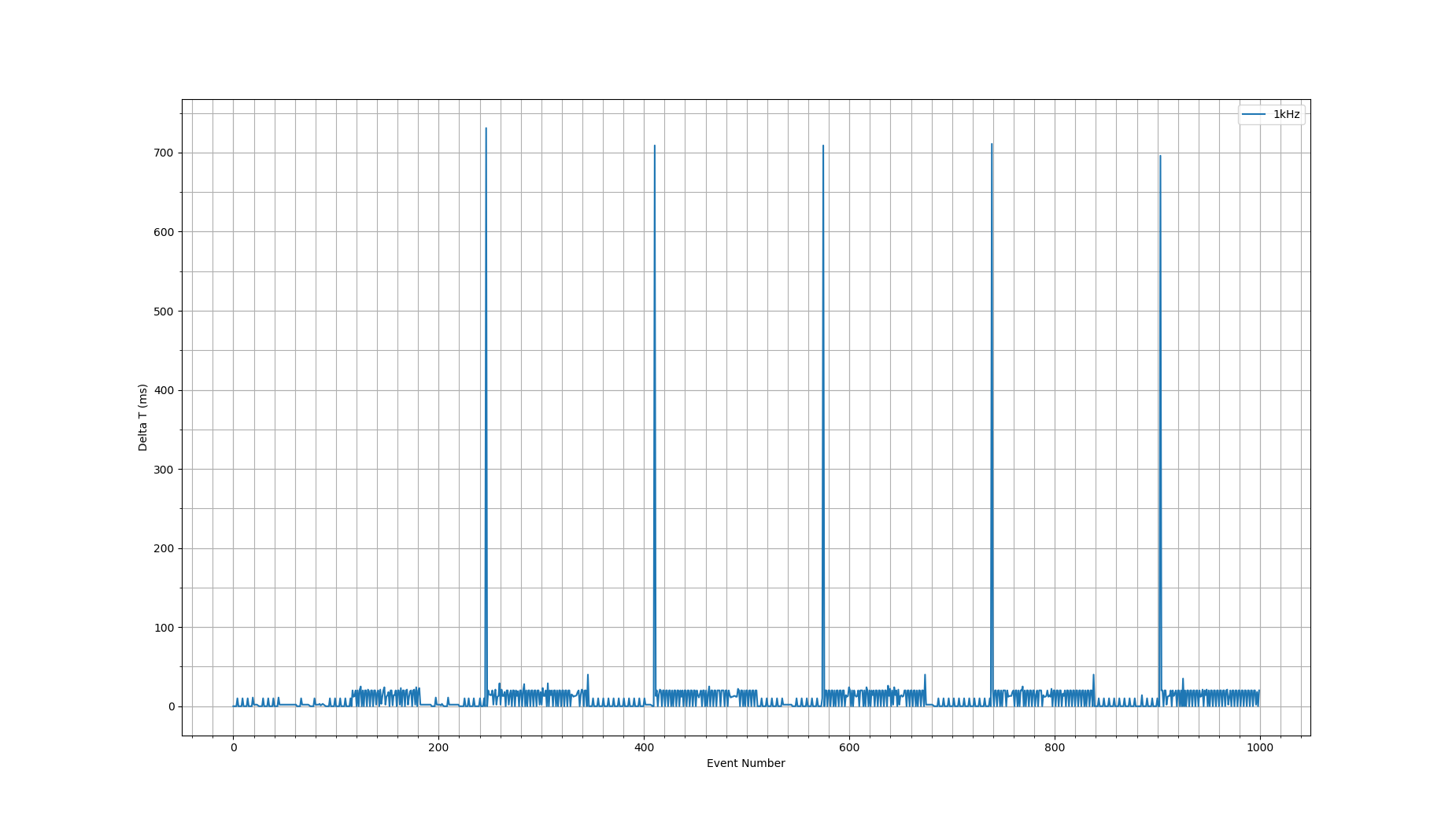

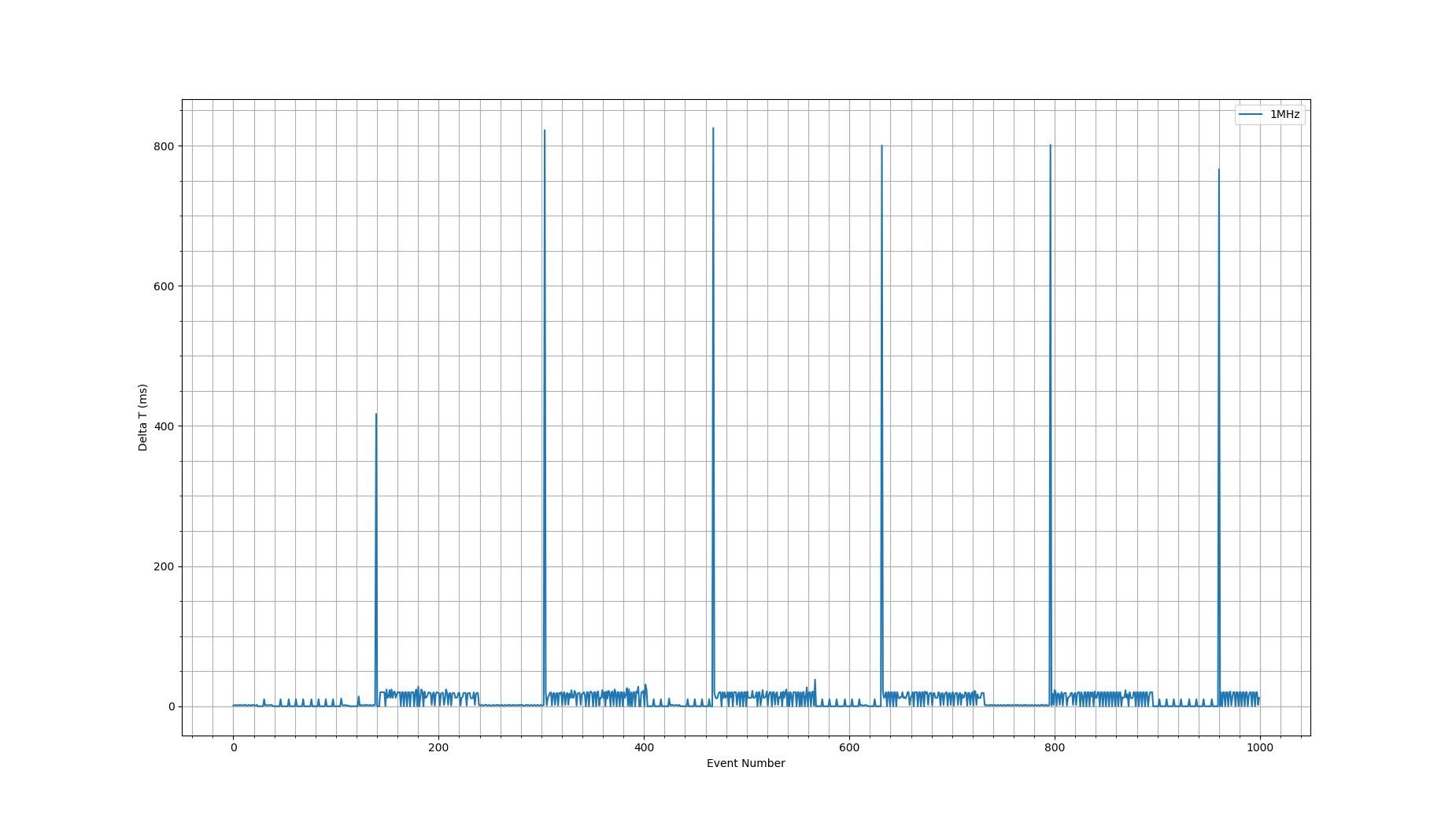

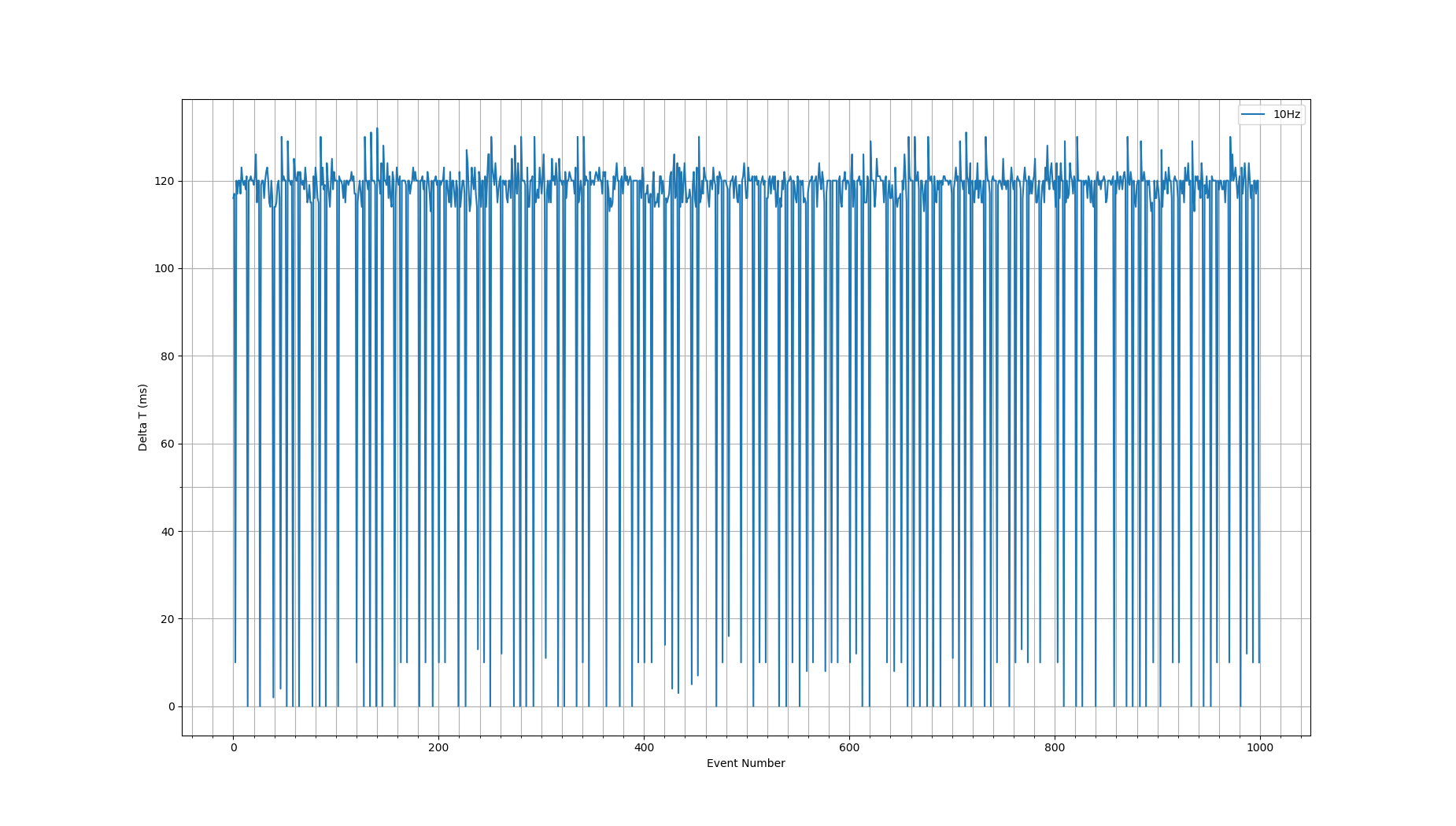

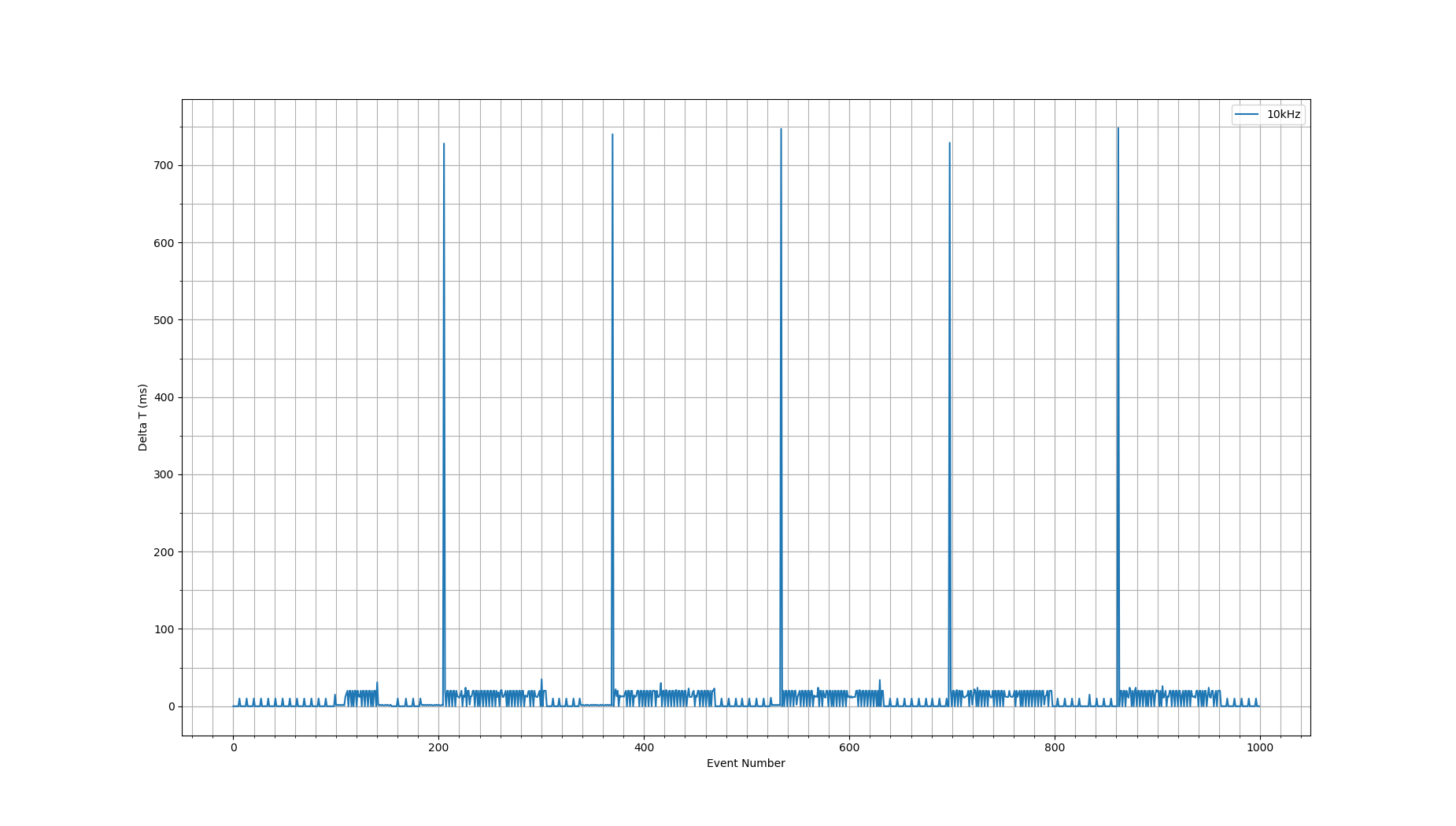

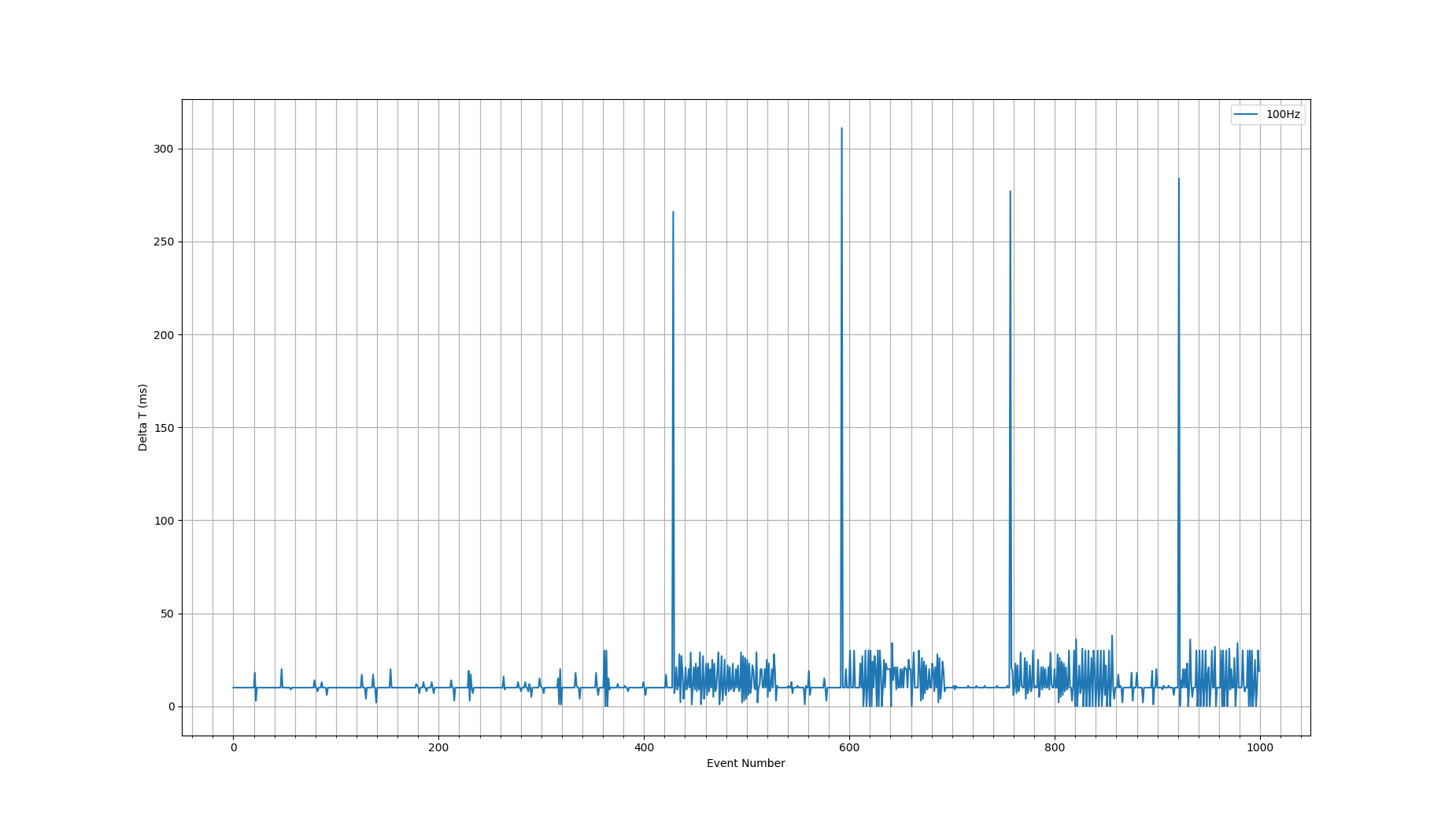

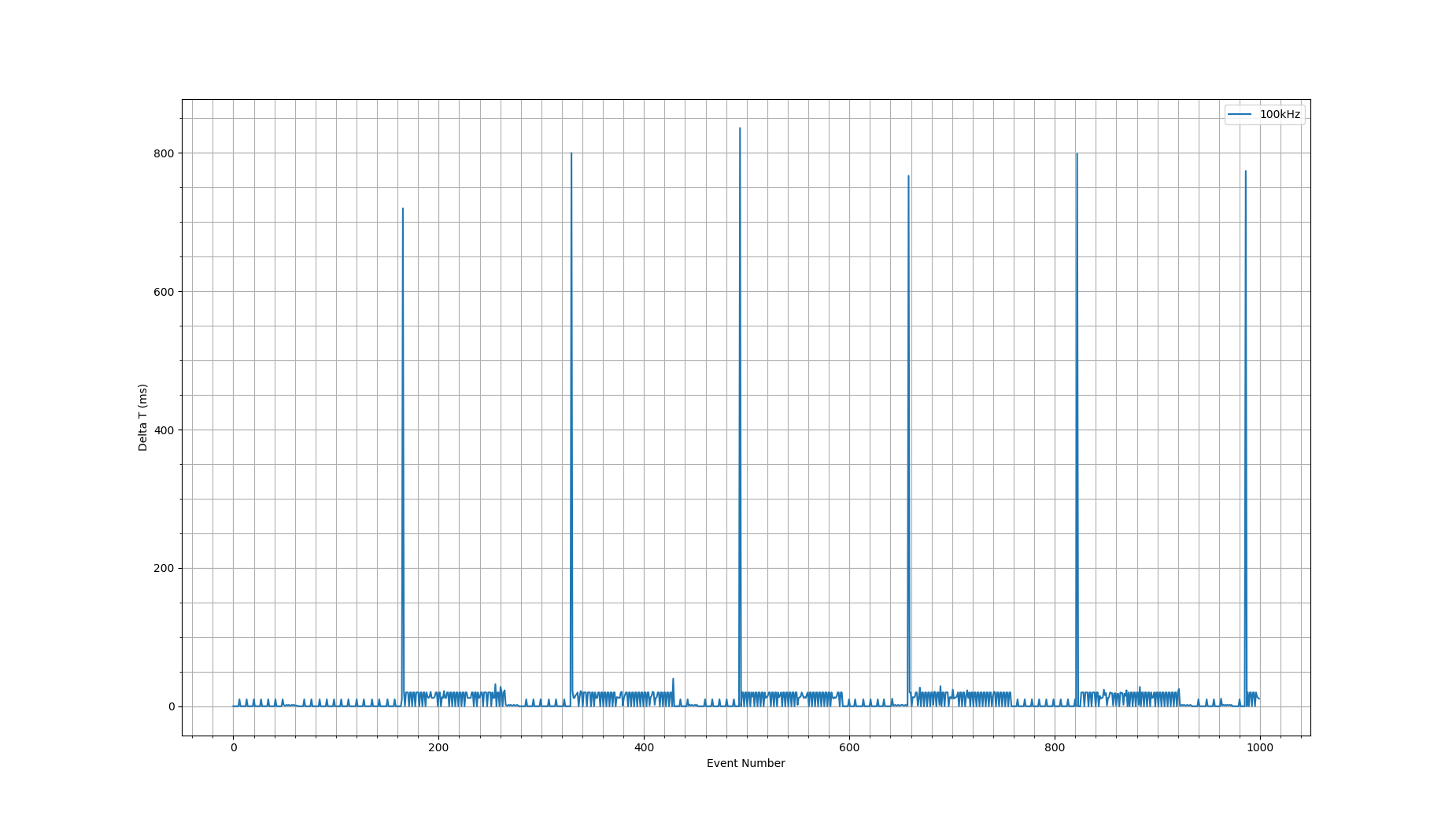

I am currently trying to figure out how to properly characterize the dead time of the DRS4 board. My most recent experiment to try and answer this question involved using an external trigger that can range from 1Hz to 2MHz. I fed this trigger into the DRS4 and collected 1000 samples with no input to any channels. I repeated this across the range of my external trigger by a factor of ten [10Hz, 100Hz, 1kHz...etc]. After I had saved these runs in XML format, I looked at the difference between timestamps on the events. Attached are my findings. Can someone offer an explanation for the periodic peaks? I am new to the DRS4 and don't really understand how it works. My guess is that there is a buffer that has to be emptied every so often, but if so, the buffer emptying time varies with the frequency of the trigger. I would ideally like to be able to know the relation of the dead time to a particular setting I change on the DRS4 such as locking the sampling speed or changing external trigger frequency.

Best,

Steven |

| Attachment 1: 1kHz.png

|

|

| Attachment 2: 1MHz.png

|

|

| Attachment 3: 10Hz.png

|

|

| Attachment 4: 10kHz.png

|

|

| Attachment 5: 100Hz.png

|

|

| Attachment 6: 100kHz.png

|

|

|

661

|

Tue Feb 27 18:04:18 2018 |

Steven Block | DRS4 Dead times | That is extremely helpful! Many thanks. One more question; If I were to take inputs from 2 channels at once, would that scale the dead time to 64us using your example?

Steven

| Stefan Ritt wrote: |

|

XML is very slow to write, and you are probably limited by that. Switch to binary mode, which is much faster. You will see in the end a maximum rate of ~500 Hz, and thus a dead time of 2ms, independent of the sampling speed. Note that you have only an evaluation board, which is optimized for ease of use. If you develop your own electronics, and do optimized readout, you can bring the deadtime down to 30ns x number of samples + 2us, or 32us if you read 1024 values from one channel.

Stefan

| Steven Block wrote: |

|

Hello All,

I am currently trying to figure out how to properly characterize the dead time of the DRS4 board. My most recent experiment to try and answer this question involved using an external trigger that can range from 1Hz to 2MHz. I fed this trigger into the DRS4 and collected 1000 samples with no input to any channels. I repeated this across the range of my external trigger by a factor of ten [10Hz, 100Hz, 1kHz...etc]. After I had saved these runs in XML format, I looked at the difference between timestamps on the events. Attached are my findings. Can someone offer an explanation for the periodic peaks? I am new to the DRS4 and don't really understand how it works. My guess is that there is a buffer that has to be emptied every so often, but if so, the buffer emptying time varies with the frequency of the trigger. I would ideally like to be able to know the relation of the dead time to a particular setting I change on the DRS4 such as locking the sampling speed or changing external trigger frequency.

Best,

Steven

|

|

|

|

663

|

Fri Mar 2 18:08:55 2018 |

Steven Block | ROI | Hello,

I have a question about how ROI works. From what I have read, it will only save data that ocurs some time [ta] dictated by the user after an event is triggered as well as a small time [tb] before the event. The technical manual seems to indicated that the deadtime assciated with operating in ROI mode can be reduced by the following factor:

. .

Where N is the number of points in the time window (ex. 2048 or 1024). Is it ok to describe this as:

Where N' is the number of samples in the ROI and N is the same as before.

For example, if I were running at 5Gsps (200ps between samples), only recording 1024 samples per event and I had an signal that lasted 2ns, that means the signal would last 10 samples. If I set the ROI to only save 20 samples around this signal, would my Deadtime go to:

? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly) ? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly)

I recognize that the caveat is that this would work only if the signal was detected during acquistion, which leads to my next question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (using the factor = 1 from above equation), or would it dump the earliest events in the buffer for the more recent ones until it detects a signal?

Finally, I assume this functionality can only be utilized with custom electornics with the DRS4, not the evaulation/demo board, please let me know if this is the case.

Best,

Steven |

|

665

|

Fri Mar 2 21:05:48 2018 |

Steven Block | ROI | Great! That is very helpful.

One more question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (or 30us depending on the supply) for, or would it dump the earliest events in the buffer for the more recent ones until it detects a signal to readout? Or rather, does filling the buffer force a readout or can it dynamically shift out old data until it detects a signal to readout.

Steven

| Stefan Ritt wrote: |

|

N'/N is correct. The 2 us "from the response you got from me" come from the fact that after readout, you have to start the DRS4 again. During this time, the power supply usually becomes slightly unstable, and it takes on the evaluation board about 2us to stabilize it again. Tha't why I add the 2 us. If you don't care about slight offset effect, or if you make a better power supply, you dead time would be 10*30ns = 300ns for 10 samples. Starting the DRS again will take one or two clock cycles from the FPGA, which might add another 30 ns or so, depending on how you program the FPGA. So the best you can achieve for 10 samples is maybe 330 ns, if you have a really good power supply (large capacitors).

You can achieve this functionality with the evaluation board, but you would have to make a special firmware for it.

Stefan

| Steven Block wrote: |

|

Hello,

I have a question about how ROI works. From what I have read, it will only save data that ocurs some time [ta] dictated by the user after an event is triggered as well as a small time [tb] before the event. The technical manual seems to indicated that the deadtime assciated with operating in ROI mode can be reduced by the following factor:

. .

Where N is the number of points in the time window (ex. 2048 or 1024). Is it ok to describe this as:

Where N' is the number of samples in the ROI and N is the same as before.

For example, if I were running at 5Gsps (200ps between samples), only recording 1024 samples per event and I had an signal that lasted 2ns, that means the signal would last 10 samples. If I set the ROI to only save 20 samples around this signal, would my Deadtime go to:

? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly) ? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly)

I recognize that the caveat is that this would work only if the signal was detected during acquistion, which leads to my next question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (using the factor = 1 from above equation), or would it dump the earliest events in the buffer for the more recent ones until it detects a signal?

Finally, I assume this functionality can only be utilized with custom electornics with the DRS4, not the evaulation/demo board, please let me know if this is the case.

Best,

Steven

|

|

|

|

605

|

Sat Apr 15 03:48:31 2017 |

Strahinja Lukic | Wave rotation during transfer from the board? | I don't know if this question is already documented elsewhere.

I am developing a DAQ code for the DRS evaluation board, v4 for a test beam experiment. I link parts of the existing DRS code as a library.

To understand the effect of various flags used in calls to the functions DRSBoard::GetTime() and DRSBoard::GetWave(), I performed several tests with the 100 MHz signal connected to the inputs of the chip (DRSBoard::EnableTcal()), and several tests with signals from scintillation counters.

My question is about the flag "adjustToClock" in the call to DRSBoard::GetWave(). From looking at the code, I expected it to cause the waveforms to be "rotated" to start from the trigger cell, in a similar way that the flag "rotated" in the call to DRSBoard::GetTime() does for the time array. However, "adjustToClock" seems to shift the waveforms wrongly. I.e., if I want both the time and the amplitude arrays "rotated" to start from the trigger cell, I should set rotated=true for time and adjustToClock=false for the amplitude. This is also how these functions are called in e.g., Osci::ReadWaveforms().

Is this correct, and does this mean that the amplitude array is "rotated" already during the transfer from the board?

I am using DRS evaluation board serial #2733, firmware revision 30000.

Many thanks,

Strahinja

|

|

607

|

Thu Apr 20 06:30:13 2017 |

Strahinja Lukic | Wave rotation during transfer from the board? | Thanks.

Strahinja

| Stefan Ritt wrote: |

|

This is correct. Actually the amplitude array is rotated already inside the DRS4 chip. So the readout starts with the stop cell plus one. If you do not do anything, the waveform is already "rotated". If you want the waveform to start with physical cell #0, you have to "unrotate" it.

Stefan

| Strahinja Lukic wrote: |

|

Is this correct, and does this mean that the amplitude array is "rotated" already during the transfer from the board?

|

|

|

|

807

|

Wed Jan 20 12:14:49 2021 |

Taegyu Lee | drs4 persistence | Dear all,

I have a question about the function that drs4 can perform.

Is there any function in drs4 that is analogous to that of "persistence display" in oscilloscope?? (accumulating pulses)

Thank you |

|

588

|

Fri Feb 24 17:34:28 2017 |

Tarik Zengin | Passing parameters to drscl | Hi everyone,

I wonder if there is a way to pass parameters to drscl. What I specifically want to do is calling drscl from a shell script and read/save some data. I want to schedule a measurement. Therefore I need to call drscl from the command line using some parameters.

It would look something like this;

#!/bin/bash

for i in {0..100}

do

echo "Reading $i"

./drscl read 0 0 test.xml

sleep 1

done

This doesn't work of course. drscl won't take arguments from the command line. Can you suggest a way to do this please?

Thank you. |

|

858

|

Tue Jan 25 14:15:00 2022 |

Thomas M. | Regarding measuring for a set time | Hello,

I'm working on a project wherein we're looking at photomultipliers. We've already acquired a DRS4 evaluation board with the intent of using it to gather our data.

I've looked at the source code for the software with the intent of maybe writing a patch to add additional functionality. I was hoping you could answer some quick questions in that regard.

Am I correct in assuming that drsosc and drscl are functionally equivalent regarding collecting data? We want to run the DRS4-EB for a predefined amount of time. However, the DRS4 scope application seems only to run for a predefined set of measurements. Have I got that right? Is there some reason to avoid running the DRS4-EB for a predefined amount of time that I should be aware of?

Appreciate any help you can provide. Thanks!

Kind regards,

Thomas

|

|

860

|

Tue Jan 25 14:44:49 2022 |

Thomas M. | Regarding measuring for a set time | Yes, you've got it exactly right. Thank you, that helps a lot!

Thomas

| Stefan Ritt wrote: |

|

drsosc is a graphical application contiously acquiring data from the board, and drscl is a command line tool for debugging, as written in the manual.

The drsosc application runs indefinitely, but I guess you refer to saving data (by hitting the "Save" button in the drsosc application). Yes the save functionality has a number of events, since you cannot store data indefinitely, since your harddisk does not have indefinite space!

I kind of sense that you want to convert the "number of event to save" into "number of seconds or hours to save". This is not build into the drsosc application. It's all open source, so feel free to change the code. Alternatively, you can use the drs_exam.cpp program coming with the distribution, wich is a simpel C++ program reading the board. It has a for loop over 10 events, but you can change the code easily to run for a predetermined amount of time.

Stefan

| Thomas M. wrote: |

|

Am I correct in assuming that drsosc and drscl are functionally equivalent regarding collecting data? We want to run the DRS4-EB for a predefined amount of time. However, the DRS4 scope application seems only to run for a predefined set of measurements. Have I got that right? Is there some reason to avoid running the DRS4-EB for a predefined amount of time that I should be aware of?

|

|

|

|

811

|

Fri Feb 26 17:05:26 2021 |

Tom Schneider | Trouble getting PLL to lock | Hello,

I am working on a custom PCB design with the DRS4 chip, and I can't get the PLL to lock. I'm feeding CLKIN with a 1MHz CMOS clock (REFCLK- tied to VDD/2), and I'm using the same loop filter as the eval board. I see from the datasheet that the PLL is enabled by default, so I'm not writing anything to the config register on startup. I am just driving DENABLE high approx. 100ms after startup and looking for the PLL lock bit to go high. When I look at DTAP, I see a 3MHz signal. Can anyone tell me what I'm doing wrong?

-Tom |

|

813

|

Fri Feb 26 18:33:52 2021 |

Tom Schneider | Trouble getting PLL to lock | Stefan,

Thanks for responding so quickly. Yes I have my clock source going to REFCLK+ (CLKIN is the signal name on my schematic). BIAS is 0.7V exactly, /RESET is high, A0-A3 are 0x0000, and the loop filter has a 4.7nF cap to GND with a 130ohm resistor + 1uF cap in parallel, just like the eval board.

Regarding the clock - I am not using an LVDS clock, but rather a 2.5V-level clock signal, with REFCLK- tied to 1.25V. Sheet 9 of the datasheet states: If no LVDS reference clock signal is available, a CMOS signal can be connected to REFCLK+ and the REFCLK input is connected to VDD/2 via a resistor divider.

Is that not a true statement?

-Tom

| Stefan Ritt wrote: |

|

I guess you mean "1 MHz clock at REFCLK+", and not CLKIN, there is no CLKIN, just a SRCLK, but that is someting else!

There could be many reasons why this is not working. It's hard for me to debug your board without actually having it in hands. So just some ideas:

- Supply a clean differential REFCLK, I never tried one end tied to VDD/2

- Is /RESET high?

- Is BIAS at roughly 0.7V?

- Is A0-A3 different from 1111, which puts the chip in standby

- Did you double check your loop filter?

The easiest usually is to start from a running evaluation board, then compare all pins 1:1 with your board.

Stefan

| Tom Schneider wrote: |

|

Hello,

I am working on a custom PCB design with the DRS4 chip, and I can't get the PLL to lock. I'm feeding CLKIN with a 1MHz CMOS clock (REFCLK- tied to VDD/2), and I'm using the same loop filter as the eval board. I see from the datasheet that the PLL is enabled by default, so I'm not writing anything to the config register on startup. I am just driving DENABLE high approx. 100ms after startup and looking for the PLL lock bit to go high. When I look at DTAP, I see a 3MHz signal. Can anyone tell me what I'm doing wrong?

-Tom

|

|

|

|

815

|

Fri Feb 26 21:24:39 2021 |

Tom Schneider | Trouble getting PLL to lock | Probe capacitance makes that tricky - if I put my probe on DSPEED, I see that it starts at approx. 2.5V then gradually decreases until it hits 0V. DTAP decreases from 3MHz to 0 during this time.

I'll try to get something together to show you.

| Stefan Ritt wrote: |

|

Can you post a scope trace of your refclk together with DTAP, DSPEED and DENABLE?

| Tom Schneider wrote: |

|

Stefan,

Thanks for responding so quickly. Yes I have my clock source going to REFCLK+ (CLKIN is the signal name on my schematic). BIAS is 0.7V exactly, /RESET is high, A0-A3 are 0x0000, and the loop filter has a 4.7nF cap to GND with a 130ohm resistor + 1uF cap in parallel, just like the eval board.

Regarding the clock - I am not using an LVDS clock, but rather a 2.5V-level clock signal, with REFCLK- tied to 1.25V. Sheet 9 of the datasheet states: If no LVDS reference clock signal is available, a CMOS signal can be connected to REFCLK+ and the REFCLK input is connected to VDD/2 via a resistor divider.

Is that not a true statement?

-Tom

| Stefan Ritt wrote: |

|

I guess you mean "1 MHz clock at REFCLK+", and not CLKIN, there is no CLKIN, just a SRCLK, but that is someting else!

There could be many reasons why this is not working. It's hard for me to debug your board without actually having it in hands. So just some ideas:

- Supply a clean differential REFCLK, I never tried one end tied to VDD/2

- Is /RESET high?

- Is BIAS at roughly 0.7V?

- Is A0-A3 different from 1111, which puts the chip in standby

- Did you double check your loop filter?

The easiest usually is to start from a running evaluation board, then compare all pins 1:1 with your board.

Stefan

| Tom Schneider wrote: |

|

Hello,

I am working on a custom PCB design with the DRS4 chip, and I can't get the PLL to lock. I'm feeding CLKIN with a 1MHz CMOS clock (REFCLK- tied to VDD/2), and I'm using the same loop filter as the eval board. I see from the datasheet that the PLL is enabled by default, so I'm not writing anything to the config register on startup. I am just driving DENABLE high approx. 100ms after startup and looking for the PLL lock bit to go high. When I look at DTAP, I see a 3MHz signal. Can anyone tell me what I'm doing wrong?

-Tom

|

|

|

|

|

|