| ID |

Date |

Author |

Subject |

|

151

|

Sat Feb 4 11:59:26 2012 |

Zhongwei Du | what sort of detectors for physical experiment the DRS4 used? |

Hello.

We are designing a waveform sampling board for Si strip array detector ,whose rise time is less than 10 ns, which makes we doubt whether the DRS4 can do more accurate than traditional charge integral circuit for charge measuring.

So we need to know what sort of detectors for physical experiment the DRS4 has been used in?

Can you give me some information? For example, Si strip array detector or CsI scintillator r ball detector ? PMT or APD ? |

|

200

|

Tue Dec 4 09:24:22 2012 |

Zhongwei Du | Question of drs4 using |

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now. |

|

202

|

Tue Dec 4 09:50:11 2012 |

Zhongwei Du | Question of drs4 using |

| Stefan Ritt wrote: |

|

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan

|

"Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. "

In this process , should i config any registers( WSR,WCR,CR ) ? |

|

29

|

Wed Dec 30 14:28:33 2009 |

aliyilmaz | normal_mode_in_drs_exam.cpp |

Dear Mr. S. Ritt

i am Ms. student , am working with your DRS4 board to calculate the time of flight of the cosmic particle which passes trough the hodoscope . i see the signals at scope , which is negative (i don't want to take positive side of the signal).

i am using your drs_exap.cpp file to take the data, i set the analog trigger source , threshold level is negative, like this(b->SetTriggerLevel(-30, true) ); but the exam file also registers the positive side of signal (i think that is spike or internal reflection), is it possible to eliminate this spike? Also i want to register the data just after the threshold value, but that is always triggered, i think that caused from the mode. Is it possible to set the trigger mode to normal in exam file?,and how can i do that?

Best regards.

Sincerely,

Ali YILMAZ (ali.yilmaz@roma1.infn.it)

|

|

276

|

Tue Jul 23 22:31:08 2013 |

alonzi | Evaluation Board Behavior |

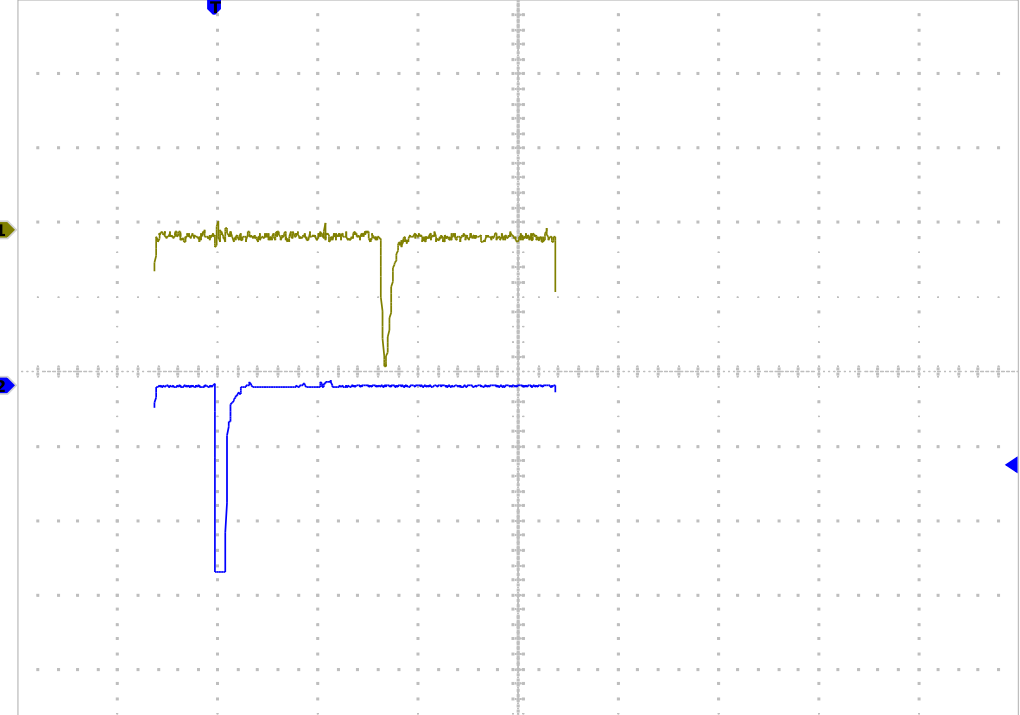

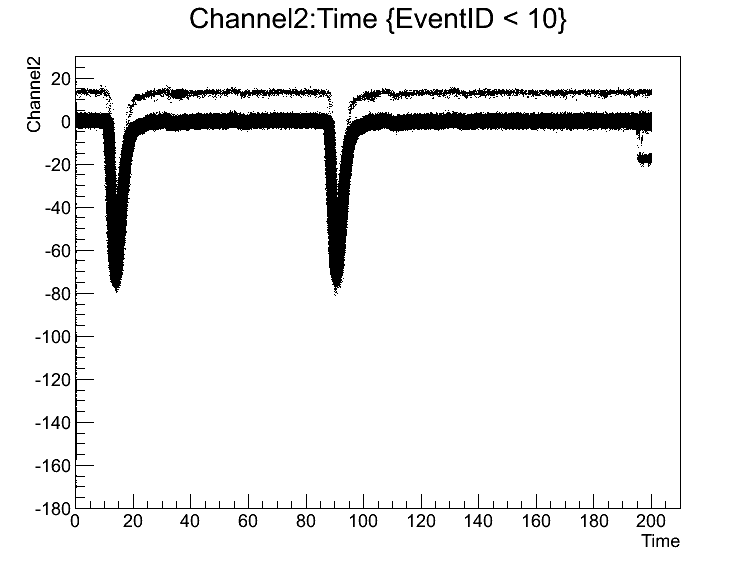

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion. |

| Attachment 1: Screenshot.png

|

|

| Attachment 2: data_problem.png

|

|

|

278

|

Tue Jul 23 22:42:31 2013 |

alonzi | Evaluation Board Behavior |

| Stefan Ritt wrote: |

|

| alonzi wrote: |

|

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion.

|

Actually the first and last sample are even more off the baseline, so I cut them out in software in the DRSOscilloscope. So actually the chip has only 1022 "usable" cells. It might happen in some rare cases that more cells are affected, although I have not yet seen this (maybe I did not look close enough). So I propose that you cut out one more bin at the beginning and the end, so a total of 1020 cells, and you should be fine.

/Stefan

|

Thanks for the quick reply. Our quick fix was to do just that. |

|

533

|

Mon Aug 29 09:36:34 2016 |

benjamin legeyt | increment write config register on the fly? |

Hello,

I have a question about using the write config register to enable/disable sampling on the fly. I am looking to instrument an experiment at EPFL where multiple short events need to be captured during a 20us period followed by an 80us quiet period during which we could read out the chip. Would it be possible to start an acquisition with all channels seeing the same signal and the write config register set to 111111111 and then shift a zero into the write config reg after each event is detected to freeze the channels in time one-by-one? In this way we could measure up to 8 different events during the active period and then read them all out together during the quiet period. I have read the posts about the simultaneous read-write mode and the issue with waveforms stopping at cell 767. not knowing the exact details of what causes this issue I wonder if it would effect this sort of operation? Also, I would like to know if dwrite must be de-asserted while the write config register is being updated or if it could be done while the sampling is active? The latter would obviously be preferable as we would not incur any dead-time during the active period.

Thanks in advance for the information,

Benjamin LeGeyt |

|

535

|

Mon Aug 29 12:18:49 2016 |

benjamin legeyt | increment write config register on the fly? |

If I may trouble you for a little more information, the critical point then is that there should not be any zeroes in the write config register while the sampling is active? In case it was unclear I would only be reading out once sampling was stopped (dwrite = 0).

As for the readout, I know that I would have to read out all 1024 samples each time, and keep track of where each channel stopped in the FPGA. I would never know the exact cell where sampling stopped but I hoped that if I discard some number of cells on each side of the expected stopping point that I would be OK.

Thanks again

| Stefan Ritt wrote: |

|

The issue with "stopping at cell 767" would also affect this mode of operation. Furthermore, the DRS4 chip has only 10 bit register which records in which cell the event has occured, and where the readout must be started. If you record 8 separate events, you don't know where to start the readout.

The DRS5 chip will have all this possibilitied, but unfortunately it won't be ready before 2-3 years from now.

Stefan

| benjamin legeyt wrote: |

|

Hello,

I have a question about using the write config register to enable/disable sampling on the fly. I am looking to instrument an experiment at EPFL where multiple short events need to be captured during a 20us period followed by an 80us quiet period during which we could read out the chip. Would it be possible to start an acquisition with all channels seeing the same signal and the write config register set to 111111111 and then shift a zero into the write config reg after each event is detected to freeze the channels in time one-by-one? In this way we could measure up to 8 different events during the active period and then read them all out together during the quiet period. I have read the posts about the simultaneous read-write mode and the issue with waveforms stopping at cell 767. not knowing the exact details of what causes this issue I wonder if it would effect this sort of operation? Also, I would like to know if dwrite must be de-asserted while the write config register is being updated or if it could be done while the sampling is active? The latter would obviously be preferable as we would not incur any dead-time during the active period.

Thanks in advance for the information,

Benjamin LeGeyt

|

|

|

|

653

|

Thu Jan 25 05:24:05 2018 |

chen wenjun | problem with the drscl(drs507) |

Hi! Stefan:

when I change a new computer(win7,64bit),I meet a problem that the drscl app cannot found the board! It shows"USB successfully scanned,but no boards found",but the drsosc runs well . when I connect to other win7*64bits computer,only one of them runs property! Is there any driver else I need to install?

Thank you!

Chen |

|

654

|

Thu Jan 25 06:10:52 2018 |

chen wenjun | drscl doesn't find eval board but drsosc does (Windows 7) |

Hi! Jim:

It seems that I meet the same question with you ,and I am confused ,have you find out the reason about this problem?Or can you tell me how you deal with it?

Thank you very much!

chen

| Jim Freeman wrote: |

|

I cannot find the EVAL board using drscl version 5.06 while the drsosc works fine. I tried 2 different eval boards and 2 different computers and the same effect. I looked under device manager at the libusb and the drs4 was there, and checked the driver which was found to be up to date.

|

|

|

656

|

Thu Jan 25 08:07:32 2018 |

chen wenjun | problem with the drscl(drs507) |

I have tried about 4 computers,only one worked fine.I truly want to know how others get this fixed,can you get in touch with them?

| Stefan Ritt wrote: |

|

This problem has been reported by several people, like elog:551

So far I could not solve it. On the computers at our lab it works find so I cannot reproduce and fix the problem. One suspicion I have is that the underlying libusb library needs to be updated. You can try to install the newest version from their website at http://libusb.info/, but I haven't tried it myself.

Stefan

| chen wenjun wrote: |

|

Hi! Stefan:

when I change a new computer(win7,64bit),I meet a problem that the drscl app cannot found the board! It shows"USB successfully scanned,but no boards found",but the drsosc runs well . when I connect to other win7*64bits computer,only one of them runs property! Is there any driver else I need to install?

Thank you!

Chen

|

|

|

|

671

|

Wed Mar 14 09:13:39 2018 |

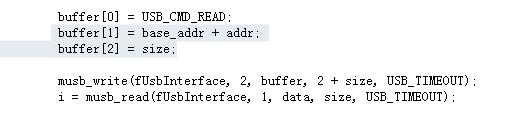

chen wenjun | confusion about the description in drs.cpp |

Hi,Stefan:

recently,whtn I study the drs.cpp code ,I found that the buffer[1] is char but the addr and the base_addr are all unsigned int,isn't there any problem that the addr may be cut off to 8 bits? Also ,I found that the data fpga recieved from the usb is 16 bits,so how can fpga get the true 32bits address from the PC. |

| Attachment 1: 20180314161201.jpg

|

|

|

689

|

Sun May 6 08:13:37 2018 |

chen wenjun | confusion about the description in drs.cpp |

Hi Stefan:

I'm still confused that althought the 8 bits buffer is enough,the FPGA receive the command through the uc_data_i register which is 16 bits wides.As we can see in the firmware, the locbus_addr is 32 bits wides. Does it means the locbus_addr[31:8] are always '0' because the address in buffer is only 8 bits. Does it means the usrbus_status_sel and usrbus_ram_sel are also '0' all the time .

thanks!

chen

| Stefan Ritt wrote: |

|

The FPGA is very small, so it only has an address space of 256 bytes. Look at the definition in DRS.cpp

#define USB_CTRL_OFFSET 0x00 /* all registers 32 bit */

#define USB_STATUS_OFFSET 0x40

#define USB_RAM_OFFSET 0x80

The registers are 32 bits wide, but the addresses only run from 0 to 255, and thus a single byte is enough for addressing them.

| chen wenjun wrote: |

|

Hi,Stefan:

recently,whtn I study the drs.cpp code ,I found that the buffer[1] is char but the addr and the base_addr are all unsigned int,isn't there any problem that the addr may be cut off to 8 bits? Also ,I found that the data fpga recieved from the usb is 16 bits,so how can fpga get the true 32bits address from the PC.

|

|

|

|

639

|

Wed Nov 22 08:31:03 2017 |

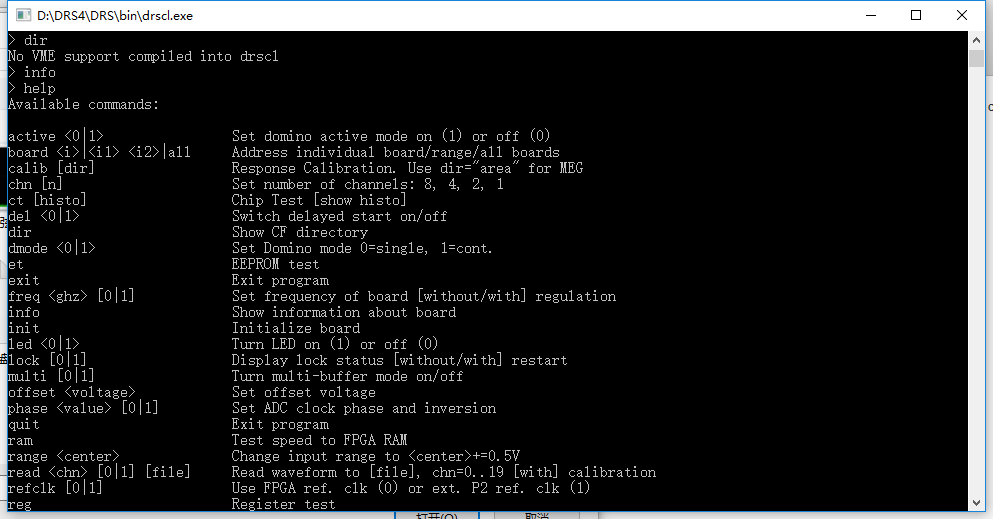

chen wenjun | using of the DRS Command Line Interface |

Hello! I'm using DRS4 evaluation board V5 with the drs command line interface,but the mannal only explained the meaning of the command--"info".And I can't get the hang of the use of other commands through "help",so is there anywhere can I learn more about other commands?Or I can only learn it through the datasheet of DRS4 chip.

Thanks!

|

| Attachment 1: ��ͼƬ_20171122153834.png

|

|

|

641

|

Wed Nov 22 08:58:33 2017 |

chen wenjun | using of the DRS Command Line Interface |

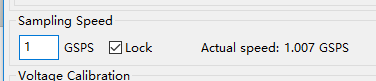

OK!Thank you! One more question,when I use the Oscillocope ,I found that the actual speed is a constant value of 1.007G,how can change this speed.

| Stefan Ritt wrote: |

|

The command line interface is more a debugging tool for experts, and you are not supposed to use it except to test the connection to the evaluation board. The programs for the user are the DRS Oscilloscope and the drs_exam.cpp example program to read out the board with your own program.

Stefan

| chen wenjun wrote: |

|

Hello! I'm using DRS4 evaluation board V5 with the drs command line interface,but the mannal only explained the meaning of the command--"info".And I can't get the hang of the use of other commands through "help",so is there anywhere can I learn more about other commands?Or I can only learn it through the datasheet of DRS4 chip.

Thanks!

|

|

|

| Attachment 1: ��ͼƬ_20171122160245.png

|

|

|

643

|

Wed Nov 22 09:19:11 2017 |

chen wenjun | using of the DRS Command Line Interface |

Thank you very much !! All my fault for I thought it too comlicated. Thank you sincerely!

| Stefan Ritt wrote: |

|

Remove the check mark from the "Lock" box and enter a different value in the sampling speed box and hit return.

| chen wenjun wrote: |

|

OK!Thank you! One more question,when I use the Oscillocope ,I found that the actual speed is a constant value of 1.007G,how can change this speed.

| Stefan Ritt wrote: |

|

The command line interface is more a debugging tool for experts, and you are not supposed to use it except to test the connection to the evaluation board. The programs for the user are the DRS Oscilloscope and the drs_exam.cpp example program to read out the board with your own program.

Stefan

| chen wenjun wrote: |

|

Hello! I'm using DRS4 evaluation board V5 with the drs command line interface,but the mannal only explained the meaning of the command--"info".And I can't get the hang of the use of other commands through "help",so is there anywhere can I learn more about other commands?Or I can only learn it through the datasheet of DRS4 chip.

Thanks!

|

|

|

|

|

|

771

|

Tue Aug 27 08:33:22 2019 |

chinmay basu | DRS4 |

Is DRS4 suitable for use with Silicon surface barrier detectors? |

|

443

|

Fri Aug 7 18:41:37 2015 |

dante | DRS4 |

Hi

I have just installed DRS4, but when I try to view it from the USB it don't work. Why?

[ .../home $] lsusb -d 04b4:1175 -v

Bus 002 Device 008: ID 04b4:1175 Cypress Semiconductor Corp.

Couldn't open device, some information will be missing

Device Descriptor: |

|

186

|

Thu Nov 1 20:08:33 2012 |

hongwei yang | DRS4 firmware |

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point? Or is there any drs4_eval4_app.vhd missing in the source files?

thanks

Hongwei |

|

188

|

Thu Nov 1 20:21:44 2012 |

hongwei yang | DRS4 firmware |

| Stefan Ritt wrote: |

|

| hongwei yang wrote: |

|

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point?

thanks

Hongwei

|

The "and" in the trigger section means now "coincidence". So the V4 board can trigger on a coincidence between two or more channels. If there is no pulse at the same time on the coincidence channels, the board will of course not trigger. The according firmware was introduced in V4, so please look at drs4_eval4_app.vhd (not eval3).

I just realized that the V4 firmware might be missing in the distribution, so I have attached it here. Look for drs_ctl_trigger_config.

Best regards,

Stefan

|

Ah, great, that helps, Thank you!

Hongwei |