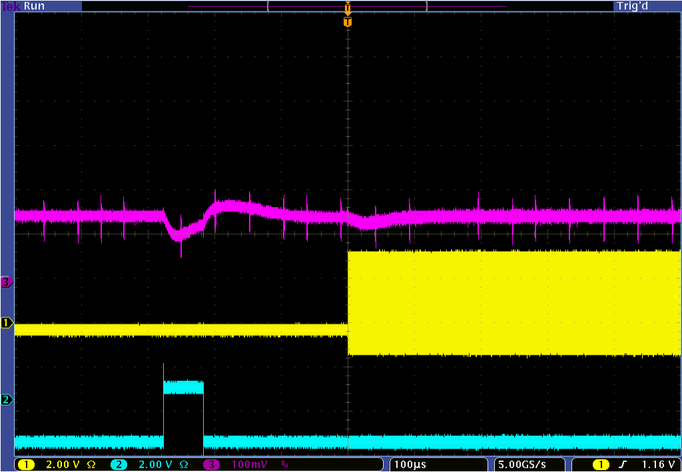

It has turned out that the stability of the AVDD and DVDD power supplies for the DRS4 are very critical. On the evaluation board I use a REG1117-2.5, on our VME board I use a ADP3338-2.5 for the DVDD power supply. When the domino wave is started, the power consumption of the DRS4 chip jumps up by ~40 mA, which has to be compensated by the linear regulator. Following screen shot shows what happens:

The blue trace is the DWRITE signal indicating the sampling phase when high. The yellow is the SRCLK showing when the readout takes place. The pink is now the DVDD power. It can be clearly seen that there is a dip of ~50 mV when the domino wave starts, a positive dip when it stops and another smaller dip when the readout starts. This causes strange effects: If the trigger arrives during the first dip, the actual sampling takes place when the DVDD is ~50 mV smaller, which leads to a baseline shift of a sampled 0V DC input voltage of about the same amount (-50 mV).

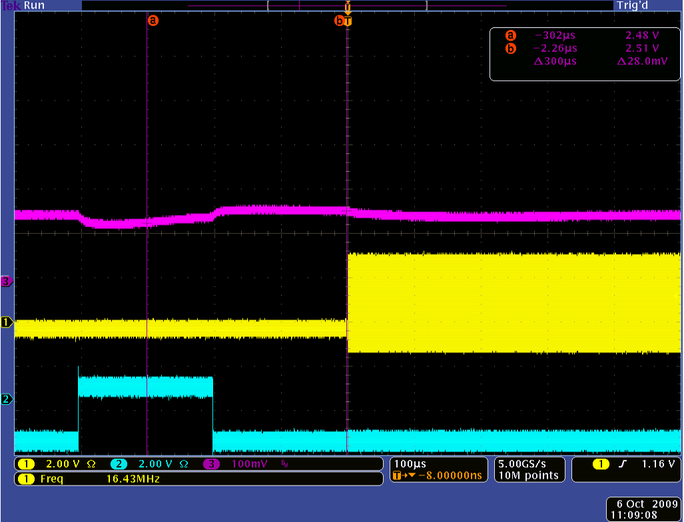

The obvious improvement is to put a huge capacitor on the power supply, but that does not help much:

The dip gets a bit smaller, but it's still there. So a better solution would be to use a faster LDO regulator. Please take care of this if you plan a new design.

Furthermore, I believe that the chip internally has some "warmup" phase, where the die heats up a bit when the additional 40 mA are drawn. So a "good" solution is to wait some time after starting the domino wave until one allows for triggers. Tests showed that a few milliseconds are necessary to keep the baseline shifts below a few millivolts. This of course decreases the dead time of the system significantly, so one has to choose the proper balance between increase dead time and increased base line shift. On some applications where a baseline shift is not an issue, one could opt for the minimum dead time. |