Dear DRS4 team,

On page 3 of the data sheet, Table 1. for readout speed a typical value of 10 MHz is specified, but in the comment column it notes optimal performance achieved at 33 MHz.

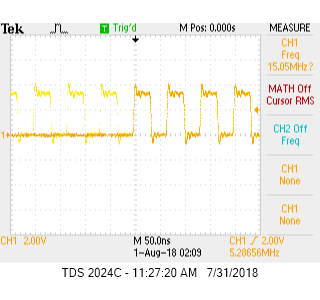

I see the V5.1 eval board runs at 16 MHz. I'd like to understand the rationale for this using speed, instead of 33 MHz. Is there an SNR issue for the ADC at the higher speed, even though this is optimal for the DRS4?

Very best,

Sean |