| ID |

Date |

Author |

Subject |

|

623

|

Wed Jul 12 04:24:39 2017 |

Toshihiro Nonaka | Time resolution between boards |

Hello,

I 'm using four evaluation boards v.3 to construct the multi-board DAQ system. One channel for each board is used as reference clock, then calibrate timing offline, which allow below 10ps resolution between boards.

Is it possible to keep the time resolution between boards below 10ps in daisy-chain mode with v.5 boards?

Thank you in adcance.

Best regards,

Toshihiro Nonaka |

|

622

|

Fri Jul 7 10:31:47 2017 |

Stefan Ritt | Trigger setting (AND AND) OR (AND AND) |

Unfortunately not with the current firmware.

Stefan

| Esperienza Giove wrote: |

|

Hello there,

is it possible to setup trigger in double AND configuration (a pair in and or other pair in and).

eg (CH 1 AND CH 2 ) OR ( CH 3 AND CH4)

Thank you

|

|

|

621

|

Thu Jul 6 15:10:48 2017 |

Esperienza Giove | Trigger setting (AND AND) OR (AND AND) |

Hello there,

is it possible to setup trigger in double AND configuration (a pair in and or other pair in and).

eg (CH 1 AND CH 2 ) OR ( CH 3 AND CH4)

Thank you |

|

620

|

Thu Jun 22 21:36:08 2017 |

Stefan Ritt | AND Trigger problems with 2-3 channels |

Hi,

from our screenshots I see the following:

- you have sometimes a huge oscillation in your preamplifier. Fix this first before doing any waveform recording

- your signals are barely 20 mV, and your trigger threshold is 20 mV. The coincidence only triggers when both signals are below the trigger threshold at the same time, and the overlap must be longer than 4-5 ns. So if your signals are not exactly in time, you won't get a coincidence trigger

Stefan

| Rebecca Schmitz wrote: |

|

Hello,

It seems that a coincidence with two fixed channels suddenly works. I don't know why.

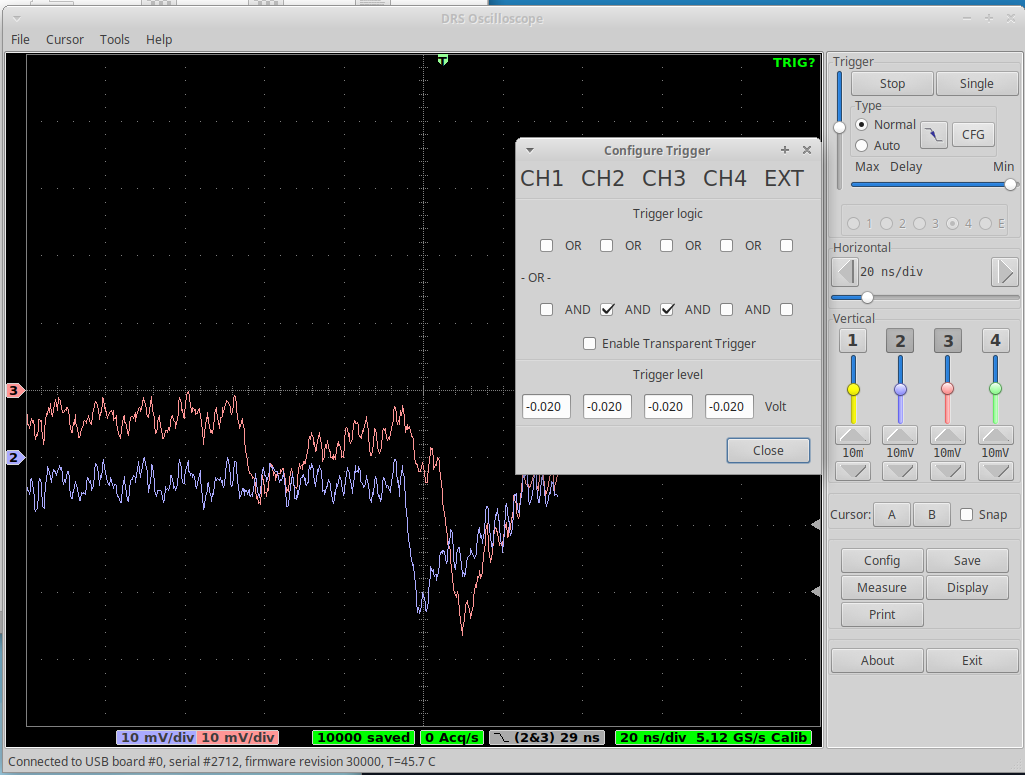

Screenshot 1 shows the trigger settings for the coincidence with two channels.

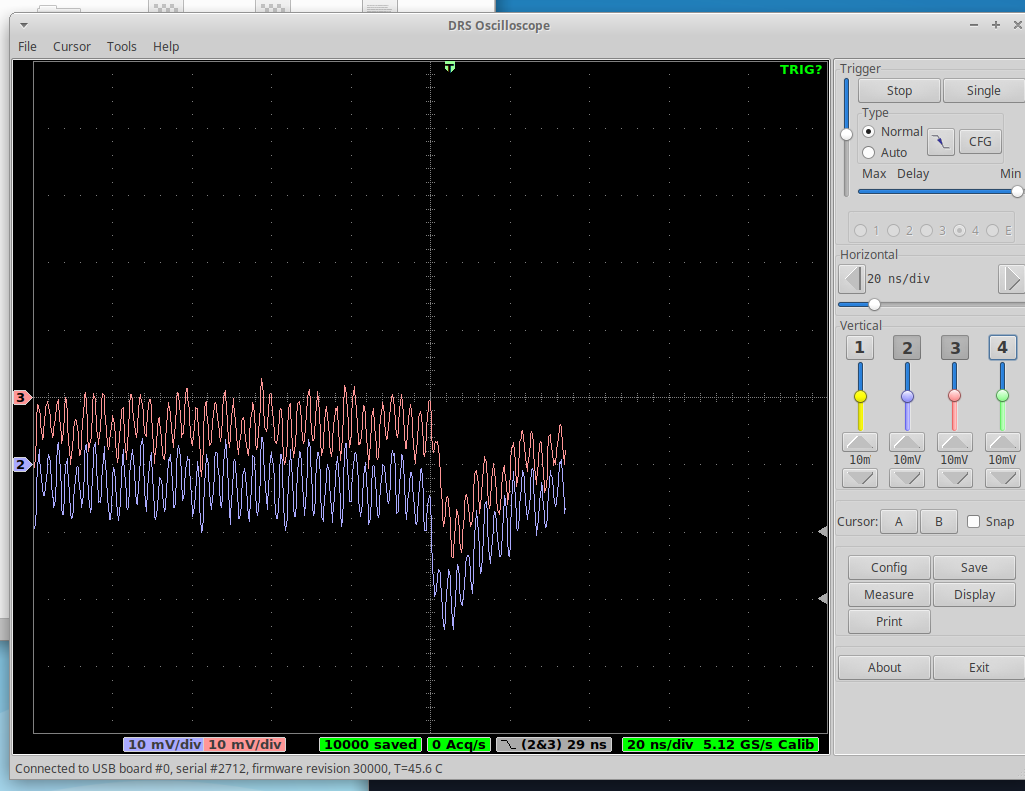

Screenshot 2 shows the oscilloscope surface.

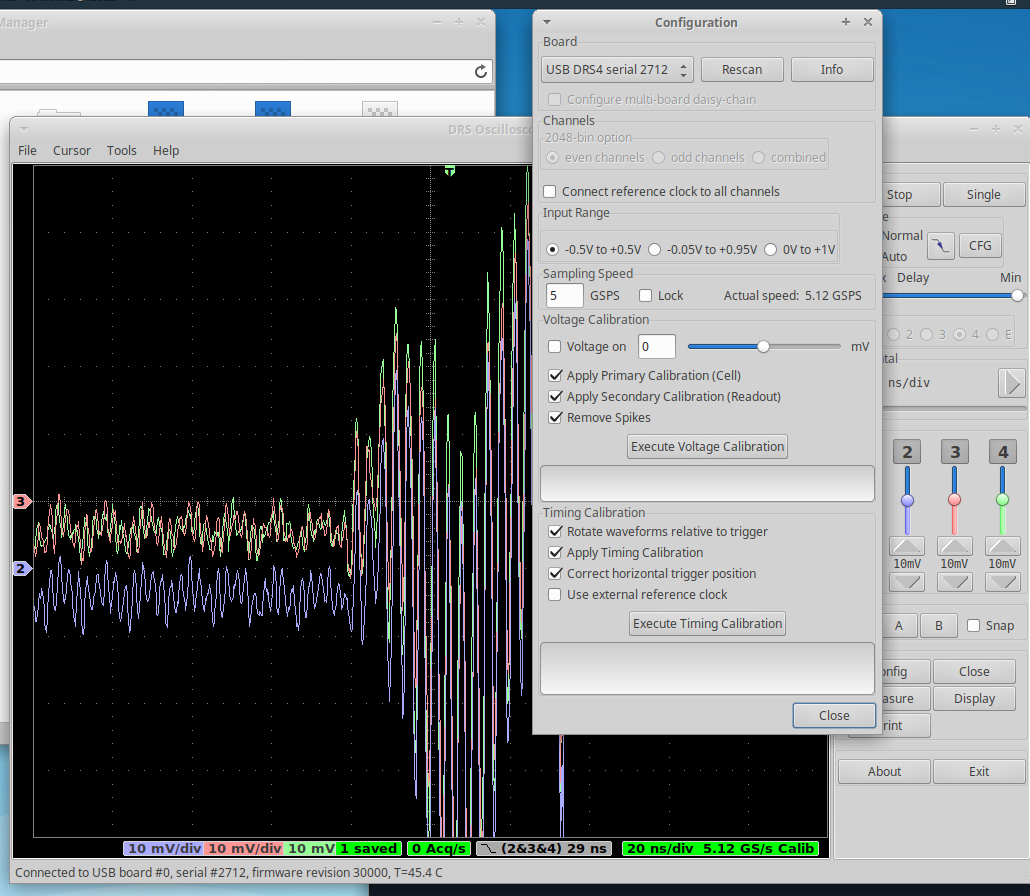

Screenshot 3 shows the configuration. In the background there is a coincidence with three channels.

In contrast to the coincidence with two channels this doesn't look good.

Rebecca

| Stefan Ritt wrote: |

|

Can you post a screenshot where I can see the channel waveforms, the configuration and the trigger settings?

Stefan

| Rebecca Schmitz wrote: |

|

Hello,

I work with the DRS4 Evaluation Board V5 and I have a problem with the software.

I have a problem with the AND trigger setting.

For this I have chosen the AND trigger function. However, when ONE channel senses an impulse, it triggers. I'm not able to see signals in the other channels, which I selected for the coincidence.

What is the cause of this? Maybe the time window?

I would like to measure a coincidence with two or three random channels. Is it possible?

Thanks for the help.

Rebecca

|

|

|

|

|

619

|

Fri Jun 16 17:34:20 2017 |

Laura Gonella | Driver installation on Windows 10 |

Hello,

I am trying to get a DRS4 board to run on Windows 10. I am having problems with the driver installation. I am getting the follwoing message

"There is no driver selected for the device information set or element"

I had specified the path to look for the driver as C:\ProgramFilesx86\DRS\driver\. I also tried the option to look online for the driver. None works. Can anyone help?

Thanks,

Laura |

|

618

|

Fri Jun 9 09:44:33 2017 |

Rebecca Schmitz | AND Trigger problems with 2-3 channels |

Hello,

It seems that a coincidence with two fixed channels suddenly works. I don't know why.

Screenshot 1 shows the trigger settings for the coincidence with two channels.

Screenshot 2 shows the oscilloscope surface.

Screenshot 3 shows the configuration. In the background there is a coincidence with three channels.

In contrast to the coincidence with two channels this doesn't look good.

Rebecca

| Stefan Ritt wrote: |

|

Can you post a screenshot where I can see the channel waveforms, the configuration and the trigger settings?

Stefan

| Rebecca Schmitz wrote: |

|

Hello,

I work with the DRS4 Evaluation Board V5 and I have a problem with the software.

I have a problem with the AND trigger setting.

For this I have chosen the AND trigger function. However, when ONE channel senses an impulse, it triggers. I'm not able to see signals in the other channels, which I selected for the coincidence.

What is the cause of this? Maybe the time window?

I would like to measure a coincidence with two or three random channels. Is it possible?

Thanks for the help.

Rebecca

|

|

|

| Attachment 1: Screenshot1.png

|

|

| Attachment 2: Screenshot2.png

|

|

| Attachment 3: Screenshot3.png

|

|

|

617

|

Thu Jun 8 15:52:20 2017 |

Stefan Ritt | AND Trigger problems with 2-3 channels |

Can you post a screenshot where I can see the channel waveforms, the configuration and the trigger settings?

Stefan

| Rebecca Schmitz wrote: |

|

Hello,

I work with the DRS4 Evaluation Board V5 and I have a problem with the software.

I have a problem with the AND trigger setting.

For this I have chosen the AND trigger function. However, when ONE channel senses an impulse, it triggers. I'm not able to see signals in the other channels, which I selected for the coincidence.

What is the cause of this? Maybe the time window?

I would like to measure a coincidence with two or three random channels. Is it possible?

Thanks for the help.

Rebecca

|

|

|

616

|

Thu Jun 8 14:26:23 2017 |

Rebecca Schmitz | AND Trigger problems with 2-3 channels |

Hello,

I work with the DRS4 Evaluation Board V5 and I have a problem with the software.

I have a problem with the AND trigger setting.

For this I have chosen the AND trigger function. However, when ONE channel senses an impulse, it triggers. I'm not able to see signals in the other channels, which I selected for the coincidence.

What is the cause of this? Maybe the time window?

I would like to measure a coincidence with two or three random channels. Is it possible?

Thanks for the help.

Rebecca |

|

615

|

Tue May 30 21:22:10 2017 |

Esperienza Giove | Setting input range |

Thank you

| Stefan Ritt wrote: |

|

See elog:531

| Esperienza Giove wrote: |

|

Hello,

is it possible to set a completely negative input range like -1 to 0 or -0.95 to 0.05 ?

|

|

|

|

614

|

Tue May 30 21:00:26 2017 |

Stefan Ritt | Setting input range |

See elog:531

| Esperienza Giove wrote: |

|

Hello,

is it possible to set a completely negative input range like -1 to 0 or -0.95 to 0.05 ?

|

|

|

613

|

Tue May 30 20:45:30 2017 |

Esperienza Giove | Setting input range |

Hello,

is it possible to set a completely negative input range like -1 to 0 or -0.95 to 0.05 ? |

|

612

|

Fri May 26 08:48:25 2017 |

Stefan Ritt | Invalid magic number 0000 |

There is no other way to reset the board. As I said, people running this under Windows or MacOS are fine, so maybe this calls for a change of OS.

| Esperienza Giove wrote: |

|

Hello, thanks for your answer. Unluckily if i try to reset in this way it keeps hanging

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

Invalid magic number: 0000

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

I also tried with sudo tee /sys/bus/usb/drivers/usb/unbind and binding again; same thing happens. It seems the board needs to be reset when this happens. Is there a way to do that - to reset the board instead of usb?

Thank you

|

Stefan Ritt wrote:

|

|

Under linux, many people observed that the USB connection is unstable to the evaluation board. This must be related to the linux USB stack, since my code runs fine under MacOSX and Windows, where I use the same USB library (libusb-1.0). So I can't do anything from my side. Baybe the linux system has some tools to reset an USB endpoint. I googled it and found some proposals here:

https://askubuntu.com/questions/645/how-do-you-reset-a-usb-device-from-the-command-line

Regards,

Stefan

| Esperienza Giove wrote: |

|

Hello everybody!

After some times i init my board, or if i stop the program during the acquisition, i get the error message "Invalid magic 0000". The only way i can solve this problem is to physically disconnect and plug in again the USB cable.

What's the point? Is there a bash command / code i could use to reset it?

Thank you very much

|

|

|

|

|

611

|

Thu May 25 20:20:57 2017 |

Esperienza Giove | Invalid magic number 0000 |

Hello, thanks for your answer. Unluckily if i try to reset in this way it keeps hanging

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

Invalid magic number: 0000

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

I also tried with sudo tee /sys/bus/usb/drivers/usb/unbind and binding again; same thing happens. It seems the board needs to be reset when this happens. Is there a way to do that - to reset the board instead of usb?

Thank you

|

Stefan Ritt wrote:

|

|

Under linux, many people observed that the USB connection is unstable to the evaluation board. This must be related to the linux USB stack, since my code runs fine under MacOSX and Windows, where I use the same USB library (libusb-1.0). So I can't do anything from my side. Baybe the linux system has some tools to reset an USB endpoint. I googled it and found some proposals here:

https://askubuntu.com/questions/645/how-do-you-reset-a-usb-device-from-the-command-line

Regards,

Stefan

| Esperienza Giove wrote: |

|

Hello everybody!

After some times i init my board, or if i stop the program during the acquisition, i get the error message "Invalid magic 0000". The only way i can solve this problem is to physically disconnect and plug in again the USB cable.

What's the point? Is there a bash command / code i could use to reset it?

Thank you very much

|

|

|

|

610

|

Thu May 25 20:17:41 2017 |

Esperienza Giove | Invalid magic number 0000 |

Hello, thanks for your answer. Unluckily if i try to reset in this way it keeps hanging

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

Invalid magic number: 0000

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

musb_write: requested 10, wrote 0, errno -7 (Unknown error 18446744073709551609)

musb_read error 0

I also tried with sudo tee /sys/bus/usb/drivers/usb/unbind and binding again; same thing happens. It seems the board needs to be reset when this happens. Is there a way to do that - to reset the board instead of usb?

Thank you

|

Stefan Ritt wrote:

|

|

Under linux, many people observed that the USB connection is unstable to the evaluation board. This must be related to the linux USB stack, since my code runs fine under MacOSX and Windows, where I use the same USB library (libusb-1.0). So I can't do anything from my side. Baybe the linux system has some tools to reset an USB endpoint. I googled it and found some proposals here:

https://askubuntu.com/questions/645/how-do-you-reset-a-usb-device-from-the-command-line

Regards,

Stefan

| Esperienza Giove wrote: |

|

Hello everybody!

After some times i init my board, or if i stop the program during the acquisition, i get the error message "Invalid magic 0000". The only way i can solve this problem is to physically disconnect and plug in again the USB cable.

What's the point? Is there a bash command / code i could use to reset it?

Thank you very much

|

|

|

|

609

|

Tue May 23 10:24:47 2017 |

Stefan Ritt | Invalid magic number 0000 |

Under linux, many people observed that the USB connection is unstable to the evaluation board. This must be related to the linux USB stack, since my code runs fine under MacOSX and Windows, where I use the same USB library (libusb-1.0). So I can't do anything from my side. Baybe the linux system has some tools to reset an USB endpoint. I googled it and found some proposals here:

https://askubuntu.com/questions/645/how-do-you-reset-a-usb-device-from-the-command-line

Regards,

Stefan

| Esperienza Giove wrote: |

|

Hello everybody!

After some times i init my board, or if i stop the program during the acquisition, i get the error message "Invalid magic 0000". The only way i can solve this problem is to physically disconnect and plug in again the USB cable.

What's the point? Is there a bash command / code i could use to reset it?

Thank you very much

|

|

|

608

|

Mon May 22 18:27:56 2017 |

Esperienza Giove | Invalid magic number 0000 |

Hello everybody!

After some times i init my board, or if i stop the program during the acquisition, i get the error message "Invalid magic 0000". The only way i can solve this problem is to physically disconnect and plug in again the USB cable.

What's the point? Is there a bash command / code i could use to reset it?

Thank you very much |

|

607

|

Thu Apr 20 06:30:13 2017 |

Strahinja Lukic | Wave rotation during transfer from the board? |

Thanks.

Strahinja

| Stefan Ritt wrote: |

|

This is correct. Actually the amplitude array is rotated already inside the DRS4 chip. So the readout starts with the stop cell plus one. If you do not do anything, the waveform is already "rotated". If you want the waveform to start with physical cell #0, you have to "unrotate" it.

Stefan

| Strahinja Lukic wrote: |

|

Is this correct, and does this mean that the amplitude array is "rotated" already during the transfer from the board?

|

|

|

|

606

|

Wed Apr 19 12:17:25 2017 |

Stefan Ritt | Wave rotation during transfer from the board? |

This is correct. Actually the amplitude array is rotated already inside the DRS4 chip. So the readout starts with the stop cell plus one. If you do not do anything, the waveform is already "rotated". If you want the waveform to start with physical cell #0, you have to "unrotate" it.

Stefan

| Strahinja Lukic wrote: |

|

Is this correct, and does this mean that the amplitude array is "rotated" already during the transfer from the board?

|

|

|

605

|

Sat Apr 15 03:48:31 2017 |

Strahinja Lukic | Wave rotation during transfer from the board? |

I don't know if this question is already documented elsewhere.

I am developing a DAQ code for the DRS evaluation board, v4 for a test beam experiment. I link parts of the existing DRS code as a library.

To understand the effect of various flags used in calls to the functions DRSBoard::GetTime() and DRSBoard::GetWave(), I performed several tests with the 100 MHz signal connected to the inputs of the chip (DRSBoard::EnableTcal()), and several tests with signals from scintillation counters.

My question is about the flag "adjustToClock" in the call to DRSBoard::GetWave(). From looking at the code, I expected it to cause the waveforms to be "rotated" to start from the trigger cell, in a similar way that the flag "rotated" in the call to DRSBoard::GetTime() does for the time array. However, "adjustToClock" seems to shift the waveforms wrongly. I.e., if I want both the time and the amplitude arrays "rotated" to start from the trigger cell, I should set rotated=true for time and adjustToClock=false for the amplitude. This is also how these functions are called in e.g., Osci::ReadWaveforms().

Is this correct, and does this mean that the amplitude array is "rotated" already during the transfer from the board?

I am using DRS evaluation board serial #2733, firmware revision 30000.

Many thanks,

Strahinja

|

|

604

|

Thu Apr 13 17:10:58 2017 |

Christian Farina | Stand-alone Time Calibration for PSI Board |

Thank you for your help Stefan. I will try to get the TC part isolated.

| Stefan Ritt wrote: |

|

Than you can try to isolate the code. Note that different SCAs might work differently. Like the DRS4 has a channel-to-channel jitter which others might not. But you will see.

Stefan

| Christian Farina wrote: |

|

Hi Stefan,

Thank you for your reply. I have read the paper already. I looked through the code and I understand that the LTC and GTC are performed by the AnalyzeSlope and AnalyzePeriod functions, respectively, correct? It seems to me to be a complicated business to re-write that part from scratch, at least for an inexperienced programmer like me. It made more sense to try to isolate that part from the original DRS.cpp. Ideally, I would like to have a stand-alone program that would work on any SCA without references to the drs hardware specifics.

| Stefan Ritt wrote: |

|

Hard to say. Timing calibration is quite delicate. If you start from scratch, better read this paper: https://arxiv.org/abs/1405.4975

If you try to extract the code from DRS.cpp, better read the paper, too. Probably it will not be possible to develop or extract the code without knowing how it works.

Best,

Stefan

| Christian Farina wrote: |

|

Hello everybody,

I was trying to create a stand-alone program that would perform a time calibration on the board. My goal would be the following.

- acquire about 10k sinus waveforms

- write them to disk (also for later reanalysis)

- run the time calibration on the recorded data

- store the clibration results in a file / database

Being not an expert, my question here is the following. Would it be easier to try to isolate the time calibration part from the DRS.cpp source code or re-write entirely the code from scratch?

Thanks.

|

|

|

|

|