| ID |

Date |

Author |

Subject |

|

360

|

Wed Jul 30 11:38:58 2014 |

Tsutomu Nagayoshi | Sampling speed of DRS4 Board ver4 |

Hello!

I have a question concerning the sampling speed of the DRS4 evaluation board.

It is written in the manual that the sampling speed of DRS4 Evaluation Board is supported above 0.7 GHz.

However I was able to set the sampling speed to be 0.5 GHz with the function DRSBpard::SetFrequency(0.5) and realized that DRSBoard::GetTime function fills time array in every 2 ns.

I am wondering if the data taken with 0.5 GHz sampling is reliable or not.

Best regards,

Tsutomu Nagayoshi

|

|

359

|

Wed Jul 16 12:10:19 2014 |

Stefan Ritt | change cascading from 1024 to 2048 bins for each input channel |

| Yves Bianga wrote: |

|

Hello,

I want to ask whether it is possible to modify a Evaluation Board 5.0 from 1024 to 2048 cells for each of the 4 input channels.

On the rev50 manual at page 31 I found an option to connect the 4 unused channels by setting 8 solder bridges.

The source code for controlling the board seems already prepared for 2048 bins, since version 5.0.2.

So my first question: Are there any implementations in the VHDL Code to control the write shift register in 2048 mode? / Is there a necessity for a newer/other VHDL Code or is it already implemented?

And the second: Are there any other modifications except the eight zero Ohm resistors and maybe changes in the FPGA code?

My board info output:

Mezz. Board index: 0

DRS type: DRS4

Board type: 9

Serial number: 2451

Firmware revision: 21260

Thanks a lot!

Yves Bianga

|

Indeed you only need R99-R106 to be installed. Unfortunately the firm/software cannot know if the resistors are there, that's why we introduced R142/R143, which connect J44 of the FPGA optionally to low. So if J44 is low (R143 installed), this tells the system that we are in 2048 bin mode. Unfortunately you need firmware revision 21305 or later to support this bit, which you apparently do not have. So you can either upgrade the firmware (if you have a download cable) or "fake" the 2048 bin mode in software. Go to line 4345 of DRS.cpp and look for DRSBoard::Is2048ModeCapable(). This function just returns the status of this bit. If you installed R99-R106, you could modify this function to always return "1" instead of "0". Then the DRSOsc program will display 2048 bins for each of the four channels.

Best regards,

Stefan |

|

358

|

Mon Jul 14 19:03:05 2014 |

Yves Bianga | change cascading from 1024 to 2048 bins for each input channel |

Hello,

I want to ask whether it is possible to modify a Evaluation Board 5.0 from 1024 to 2048 cells for each of the 4 input channels.

On the rev50 manual at page 31 I found an option to connect the 4 unused channels by setting 8 solder bridges.

The source code for controlling the board seems already prepared for 2048 bins, since version 5.0.2.

So my first question: Are there any implementations in the VHDL Code to control the write shift register in 2048 mode? / Is there a necessity for a newer/other VHDL Code or is it already implemented?

And the second: Are there any other modifications except the eight zero Ohm resistors and maybe changes in the FPGA code?

My board info output:

Mezz. Board index: 0

DRS type: DRS4

Board type: 9

Serial number: 2451

Firmware revision: 21260

Thanks a lot!

Yves Bianga |

|

357

|

Fri Jun 27 11:23:19 2014 |

ChengMing Du | drsosc binary to cern ROOT file conversion |

| Stefan Ritt wrote: |

|

| Luka Pavelic wrote: |

|

Thank you for your fast and very helpful replay.

I made it work with drsosc version 4 but with version 5 i am getting weird results. Is it possible that they changed binary formatting?

|

Yes, but this is documented in the evaluation board manual. You have to modify the script slightly. I will update it myself in about 2-3 weeks.

Cheers,

Stefan

|

hi Stefan,can you update the code to convert binary to root for newest drsosc?Thanks. |

|

356

|

Mon Jun 16 15:35:59 2014 |

Osip Lishilin | Announcement of new Evaluation Board V5 |

| Stefan Ritt wrote: |

|

| Osip Lishilin wrote: |

|

| Stefan Ritt wrote: |

|

Hardware scalers for all four channels and the trigger working up to 200 MHz. With the trigger scaler one can measure for example coincidence rates between two channels.

|

Does it give the ability to measure triggering rate? I'm talking again about possibility of use DRS4 as pulse counter for PMT's. If yes, do I need new v5 board or it is possible to use v4 board?

|

Yes it is possible to measure the raw trigger rate, with a resolution of 10 Hz. You need a new V5 board for that.

|

I'm not sure if I understand you correctly. The trigger rate could be up to 200 MHz, and it's possible to measure it with 10 Hz resolution. Is it right?

Does it possible to measure independent trigger rate for each channel? |

|

355

|

Thu Jun 12 17:16:13 2014 |

Stefan Ritt | CalibrationWaveform |

| Toshihiro Nonaka wrote: |

|

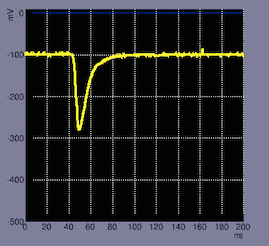

I'm writing the drs_exam.cpp to use multi-boards(v3, firmware:4.0.0), and taking data succeeded. But I have several questions about function written in DRS.cpp.

- I wrote following code in drs_exam.cpp to set input range -0.4~0.6

b1->SetInputRange(0.1);

And the 100mV offset appeared(I attached a picture). I think this is due to the voltage calibration isn't done.(Calibrated to -0.5~0.5mV in DRS Oscilloscope)

If so, could you show me a simple usage of "CalibrationWaveform()" function in DRS.cpp? (or other function?)

2. Although this question might be the almost same with above, is there any way to execute voltage and timing calibration in drs_exam.cpp?

Now I start DAQ by executing drs_exam.cpp after I execute voltage and timing calibration to each board by DRS Oscilloscope program.

3. Which command is right to use external trigger?

b1->SetTriggerSource(4); or b1->SetTriggerSource(1<<4);

Best regards,

Toshihiro Nonaka

|

1. b->CalibrateVolt(NULL);

2. see 1.

3. For the V3 boards use b->SetTriggerSource(4), for V4 and V5 boards, use b->SetTriggerSource(1<<4). I had to change that because from V4 on we can have logical combinations between channels (like channel 1 AND channel 2).

Best regards,

Stefan |

|

354

|

Thu Jun 12 12:46:00 2014 |

Stefan Ritt | DRS eval bord v5 Timing |

> a) Calibration:

> I am using 4 boards daisy chained. To achieve optimal time resolution I did first a voltage calibration and right afterwards a time calibration. For all

> boards after the master I am not sure how to do it.

> After setting the flag "Configure multi-board daisy-chain" in the config menu, all the slave boards set the flag "use external reference clock". By

> hitting the voltage calibration button, the slave boards unset this flag. Is it true, that I have to re-set this before doing the time-calibration right

> afterwards?

Please do NOT do any calibration in multi-board mode. This will not work. Calibrate the boards separately, then activate the multi-board mode. Please note that the timing between the boards is not better

than ~50 ps. This is a limitation of the FPGA clock generators. If you need better timing, you have to feed an external clock into one channel of each board (leaving only 3 channels for DAQ). The upcoming

WaveDREAM board will have 16 channels per board, so building bigger DAQ systems will be much easier (and more precise).

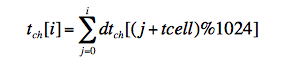

> b) getting the right times in binary format:

> To get the time out of the time width (i.e. the t_ch[i]) you sum up in your documentation from j=0 to j=i (see attachment). In your example code

> read_binary.cpp (line 113) you sum from j=0 to j=i-1. Since you get the the bin with in the binary file, I guess that the example code is correct one?

Yes, I will correct the documentation.

Cheers,

Stefan |

|

353

|

Thu Jun 12 12:40:03 2014 |

Roman Gredig | DRS eval bord v5 Timing |

Dear Stefan

I have two questions concerning the best time resolution with the DRS V5 eval board.

a) Calibration:

I am using 4 boards daisy chained. To achieve optimal time resolution I did first a voltage calibration and right afterwards a time calibration. For all

boards after the master I am not sure how to do it.

After setting the flag "Configure multi-board daisy-chain" in the config menu, all the slave boards set the flag "use external reference clock". By

hitting the voltage calibration button, the slave boards unset this flag. Is it true, that I have to re-set this before doing the time-calibration right

afterwards?

b) getting the right times in binary format:

To get the time out of the time width (i.e. the t_ch[i]) you sum up in your documentation from j=0 to j=i (see attachment). In your example code

read_binary.cpp (line 113) you sum from j=0 to j=i-1. Since you get the the bin with in the binary file, I guess that the example code is correct one?

Thank you very much,

Cheers,

Roman |

| Attachment 1: eqn1.png

|

|

|

352

|

Wed Jun 11 11:13:50 2014 |

Stefan Ritt | Announcement of new Evaluation Board V5 |

| Osip Lishilin wrote: |

|

| Stefan Ritt wrote: |

|

Hardware scalers for all four channels and the trigger working up to 200 MHz. With the trigger scaler one can measure for example coincidence rates between two channels.

|

Does it give the ability to measure triggering rate? I'm talking again about possibility of use DRS4 as pulse counter for PMT's. If yes, do I need new v5 board or it is possible to use v4 board?

|

Yes it is possible to measure the raw trigger rate, with a resolution of 10 Hz. You need a new V5 board for that. |

|

351

|

Mon Jun 9 12:03:26 2014 |

Osip Lishilin | Announcement of new Evaluation Board V5 |

| Stefan Ritt wrote: |

|

Hardware scalers for all four channels and the trigger working up to 200 MHz. With the trigger scaler one can measure for example coincidence rates between two channels.

|

Does it give the ability to measure triggering rate? I'm talking again about possibility of use DRS4 as pulse counter for PMT's. If yes, do I need new v5 board or it is possible to use v4 board? |

|

350

|

Thu May 29 04:22:43 2014 |

Toshihiro Nonaka | CalibrationWaveform |

I'm writing the drs_exam.cpp to use multi-boards(v3, firmware:4.0.0), and taking data succeeded. But I have several questions about function written in DRS.cpp.

- I wrote following code in drs_exam.cpp to set input range -0.4~0.6

b1->SetInputRange(0.1);

And the 100mV offset appeared(I attached a picture). I think this is due to the voltage calibration isn't done.(Calibrated to -0.5~0.5mV in DRS Oscilloscope)

If so, could you show me a simple usage of "CalibrationWaveform()" function in DRS.cpp? (or other function?)

2. Although this question might be the almost same with above, is there any way to execute voltage and timing calibration in drs_exam.cpp?

Now I start DAQ by executing drs_exam.cpp after I execute voltage and timing calibration to each board by DRS Oscilloscope program.

3. Which command is right to use external trigger?

b1->SetTriggerSource(4); or b1->SetTriggerSource(1<<4);

Best regards,

Toshihiro Nonaka |

| Attachment 1: offset.png

|

|

|

349

|

Tue May 27 16:07:17 2014 |

Stefan Ritt | Spikes in DRS4 data on custom baord. |

| Dominik Neise wrote: |

|

We see quite some spikes in our DRS4 sampled data in FACT. We see different types of spikes:

- single cell spikes, usually showing a large amplitude of 200mV

- double cell spikes, usually only in the order of 20mV.

- Even triple and quadro cell spikes are rarely seen.

The double cell spikes often occur as symmetrical double cell spikes mirrored at cell 512. quadro cell spikes seem to be nothing else, than connected symmetrical double cell spikes. For the triple cell spikes we have no idea.

Currently we use simple filters to get rid of these spikes, this workes rather well for the large single cell spikes, but with the occurance of tripples and quadros we started to worry about higher multiples and revived our DRS4 spike investigations.

Now I was told, that you Stefan know already where these spikes come from and even a paper exisits. Unfortunately so far I was unable to find it.

I wonder if it is possible to predict the occurance of these spikes, so one does not have to search for them anymore and can get rid of the filters.

Best regards

Dominik

|

All I know is that the "20mV" spikes are always symmetrical around cell #512, that they are typically 17.4 mV in height, and that they occur always in all 9 channels simultaneously. They cannot occur in all locations, but there only like 32 possible locations where they can occur. With this information it should be easy to fix them by filtering.

200 mV spikes are new to me. I do not see them in our boards, so it must be related to the board readout and not to the chip.

Best regards,

Stefan

|

|

348

|

Tue May 27 13:46:18 2014 |

Dominik Neise | Spikes in DRS4 data on custom baord. |

We see quite some spikes in our DRS4 sampled data in FACT. We see different types of spikes:

- single cell spikes, usually showing a large amplitude of 200mV

- double cell spikes, usually only in the order of 20mV.

- Even triple and quadro cell spikes are rarely seen.

The double cell spikes often occur as symmetrical double cell spikes mirrored at cell 512. quadro cell spikes seem to be nothing else, than connected symmetrical double cell spikes. For the triple cell spikes we have no idea.

Currently we use simple filters to get rid of these spikes, this workes rather well for the large single cell spikes, but with the occurance of tripples and quadros we started to worry about higher multiples and revived our DRS4 spike investigations.

Now I was told, that you Stefan know already where these spikes come from and even a paper exisits. Unfortunately so far I was unable to find it.

I wonder if it is possible to predict the occurance of these spikes, so one does not have to search for them anymore and can get rid of the filters.

Best regards

Dominik |

|

347

|

Mon May 19 08:04:57 2014 |

Stefan Ritt | simultaneous writing and reading with region of interest mode? |

| Benjamin LeGeyt wrote: |

|

Hello!

We're developing electronics based on the DRS4 to read out a breast PET scanner and our event rate will be quite high so we're concerned about dead-time. with that in mind, I have a question regarding the mode of simultaneous writing and reading that is described in the DRS4 data sheet. I think the description there is quite clear but I'd like to ask for a few clarifications.

1) Are the channels required to be read out via the channel multiplexer when doing the simultaneous write/read or is it ok to read out all channels in parallel (even the ones still sampling) and just throw away the ones you don't want?

2) If one wanted to use region of interest mode along with the simultaneous write/read, how would that work? Here is what I would think - please tell me if I'm missing some important detail:

-upon trigger, deassert dwrite.

-strobe RSRLOAD

-increment write config register

-reassert dwrite

-start the readout (reading out stop shift register value on SROUT as data comes out)

3) now to add even more complexity - I would actually like to use simultaneous write/read along with region of interest mode and also with pairs of cascaded channels as we need >500ns latency and 2Gsps is too slow for our signals. the combination of cascading and simultaneous write/read is addressed in the data sheet but I still have one question. In normal circumstances when cascading channels, one would read out the value in the write shift register to know which channel was active when the domino wave stopped. I assume that this is not possible when dwrite is enabled as the write shift register is then advanced by the domino wave, so I see three possibilities:

-accept more dead-time and read out the write-shift-register each time (adds ~240ns to deadtime)

-just read out both channels every time and figure out later where is the data you want

-attempt to keep track of the expected state of write-shift-register in firmware.

is there a better option that I have not thought of?

many thanks!

Benjamin LeGeyt

|

Unfortunately the simultaneous writing/reading does not work as described in the data sheet. Just recently we found out that due to a bug in the chip a part of the waveform is missing if you read and write at the same time. The only clean solution is to use two DRS4 chips in parallel. You read one chip while the other samples, then you switch over between them. In that case all the ROI scheme and channel cascading works normally. The dead time will be addressed by the DRS5 chip, which will be dead time free, but will not be available until in maybe 2-3 years.

/Stefan |

|

346

|

Fri May 16 14:04:47 2014 |

Benjamin LeGeyt | simultaneous writing and reading with region of interest mode? |

Hello!

We're developing electronics based on the DRS4 to read out a breast PET scanner and our event rate will be quite high so we're concerned about dead-time. with that in mind, I have a question regarding the mode of simultaneous writing and reading that is described in the DRS4 data sheet. I think the description there is quite clear but I'd like to ask for a few clarifications.

1) Are the channels required to be read out via the channel multiplexer when doing the simultaneous write/read or is it ok to read out all channels in parallel (even the ones still sampling) and just throw away the ones you don't want?

2) If one wanted to use region of interest mode along with the simultaneous write/read, how would that work? Here is what I would think - please tell me if I'm missing some important detail:

-upon trigger, deassert dwrite.

-strobe RSRLOAD

-increment write config register

-reassert dwrite

-start the readout (reading out stop shift register value on SROUT as data comes out)

3) now to add even more complexity - I would actually like to use simultaneous write/read along with region of interest mode and also with pairs of cascaded channels as we need >500ns latency and 2Gsps is too slow for our signals. the combination of cascading and simultaneous write/read is addressed in the data sheet but I still have one question. In normal circumstances when cascading channels, one would read out the value in the write shift register to know which channel was active when the domino wave stopped. I assume that this is not possible when dwrite is enabled as the write shift register is then advanced by the domino wave, so I see three possibilities:

-accept more dead-time and read out the write-shift-register each time (adds ~240ns to deadtime)

-just read out both channels every time and figure out later where is the data you want

-attempt to keep track of the expected state of write-shift-register in firmware.

is there a better option that I have not thought of?

many thanks!

Benjamin LeGeyt |

|

345

|

Tue May 13 23:08:50 2014 |

Stefan Ritt | drsosc binary to cern ROOT file conversion |

| Luka Pavelic wrote: |

|

Thank you for your fast and very helpful replay.

I made it work with drsosc version 4 but with version 5 i am getting weird results. Is it possible that they changed binary formatting?

|

Yes, but this is documented in the evaluation board manual. You have to modify the script slightly. I will update it myself in about 2-3 weeks.

Cheers,

Stefan |

|

344

|

Tue May 13 22:03:47 2014 |

Luka Pavelic | drsosc binary to cern ROOT file conversion |

Thank you for your fast and very helpful replay.

I made it work with drsosc version 4 but with version 5 i am getting weird results. Is it possible that they changed binary formatting?

|

|

343

|

Tue May 13 19:39:36 2014 |

Stefan Ritt | drsosc binary to cern ROOT file conversion |

| Luka Pavelic wrote: |

|

Hi,

Does anybody have program for conversion from binary or xml to cern ROOT *.root file?

Thank you for any help you can provide,

Luka Pavelic

|

You look here: elog:262

/Stefan |

|

342

|

Tue May 13 19:34:58 2014 |

Luka Pavelic | drsosc binary to cern ROOT file conversion |

Hi,

Does anybody have program for conversion from binary or xml to cern ROOT *.root file?

Thank you for any help you can provide,

Luka Pavelic

|

|

341

|

Thu Apr 24 23:03:25 2014 |

Carlo Stella | drs_exam project fail to compile |

| Stefan Ritt wrote: |

|

| Carlo Stella wrote: |

|

Hi,

when I try to compile drs_exam project my computer give me this output:

1>------ Rebuild All started: Project: drs_exam, Configuration: Debug Win32 ------

1> averager.cpp

1>c:\users\daq\desktop\

original drs\drs5\src\averager.cpp(165): warning C4996: 'fopen': This function or variable may be unsafe. Consider using fopen_s instead. To disable deprecation, use _CRT_SECURE_NO_WARNINGS. See online help for details.

1> c:\program files (x86)\microsoft visual studio 10.0\vc\include\stdio.h(234) : see declaration of 'fopen'

1> DRS.cpp

1>c:\users\daq\desktop\original drs\drs5\src\drs.cpp(4597): warning C4244: '=' : conversion from 'double' to 'float', possible loss of data

1> drs_exam.cpp

1> Generating Code...

1> musbstd.c

1> mxml.c

1> strlcpy.c

1> Generating Code...

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_claim_interface referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_configuration referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_open referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_busses referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_debug referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_devices referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_busses referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_init referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_altinterface referenced in function _musb_set_altinterface

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_close referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_release_interface referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_write referenced in function _musb_write

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_read referenced in function _musb_read

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_reset referenced in function _musb_reset

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_descriptor referenced in function _musb_get_device

1>.\Debug/drs_exam.exe : fatal error LNK1120: 15 unresolved externals

========== Rebuild All: 0 succeeded, 1 failed, 0 skipped ==========

Can anyone help me to solve the problem?

|

Have a look at the web site http://www.psi.ch/drs/software-download . Under the MS Windows section it says that you have to install the libusb-1.0 package first before you can compile the example program. This is also obvious from the missing _usb_* functions in the error listing above.

/Stefan

|

Hi Stefan,

you were right, I forgot to install the libusb driver.

Thanks for your support |