| ID |

Date |

Author |

Subject |

|

832

|

Mon Sep 6 14:42:23 2021 |

Jiaolong | how to acquire the stop channel with 2x4096 cascading | Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong |

|

Draft

|

Fri Nov 5 01:10:25 2021 |

Jiaolong | how to acquire the stop channel with 2x4096 cascading |

| Jiaolong wrote: |

|

Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong

|

|

|

850

|

Fri Nov 5 01:12:10 2021 |

Jiaolong | how to acquire the stop channel with 2x4096 cascading | Thanks for your advice. The problem has been solved by setting the srin again while reading out from srout.

| Stefan Ritt wrote: |

|

The problem must be on your side, since the Write Shift Register readout works in other applications with the DRS4 chip. So I can only speculate what could be wrong:

- Do you really properly set the WSR? When you program it with 00010001b, add 8 more clock cycles and you should see the 00010001b pattern at WSROUT.

- Do all tests with an oscilloscope, to avoid potential problems in your FPGA firmware (like an input configures as an output by mistake).

- DWRITE must be high to see the contents of the WSR at the WSROUT pin, maybe that’s your mistake, see datasheet p 5 of 16.

- To see the contents of the WSR at SROUT, A0-3 must be 1101b, please check with your oscilloscope

- The addresses A0-A3 are simply connected to a multiplexer, so no clock is necessary after the addresses change

Stefan

| Jiaolong wrote: |

|

Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong

|

|

|

|

842

|

Mon Oct 25 18:48:04 2021 |

Javier Caravaca | Trigger multiple boards independently | Hello,

I recently acquired 4 DRS4 boards and I wanted to ask if it was possible to trigger them independently from the same computer.

I know that you can daisy-chain boards and trigger them all at the same time, but in my case, each of my boards record independent events, so I want them to trigger when trigger conditions are met in each board. I currently use the provided DRSOSC software, that can trigger on only the board that is being displayed at that moment. I tried opening several instances of DRSOSC to associate each to each board, but that is not possible since the second instance already does not find the boards. I wonder if there is a way of triggering from each board independently without having to use four computers.

Thank you,

Javier. |

|

847

|

Tue Oct 26 23:18:32 2021 |

Javier Caravaca | Trigger multiple boards independently | Thank you Stefan. Actually I noticed that the source code of drs_exam was available after I started this thread, and that was the solution that occurred to me too. I'll give that a try.

A related question is: if the 4 boards are triggering at max rate (500Hz), would the total data throughtput (of the four boards together) be 2GHz (500Hz x 4)? Or is the limitation on the readout, rather than the triggering?

Best,

Javier.

| Stefan Ritt wrote: |

|

Unfortunately an independent operation from a single computer is not supported by the software. You can try to modify the drs_exam program and extend it. You can poll all boards in sequence and just read out that one which got a trigger, then start the loop again. But I don't know how good you are in programming. I needs a bit of experience to do that.

Stefan

| Javier Caravaca wrote: |

|

Hello,

I recently acquired 4 DRS4 boards and I wanted to ask if it was possible to trigger them independently from the same computer.

I know that you can daisy-chain boards and trigger them all at the same time, but in my case, each of my boards record independent events, so I want them to trigger when trigger conditions are met in each board. I currently use the provided DRSOSC software, that can trigger on only the board that is being displayed at that moment. I tried opening several instances of DRSOSC to associate each to each board, but that is not possible since the second instance already does not find the boards. I wonder if there is a way of triggering from each board independently without having to use four computers.

Thank you,

Javier.

|

|

|

|

898

|

Fri Jun 9 04:11:40 2023 |

Javier Caravaca | Different sampling rates in multi-board configuration | Hello,

Is it possible to have different sampling rates in multi-board configuration? I tried using the scope application but I am unable to change the sampling rate independently.

Best,

Javier. |

|

851

|

Tue Nov 16 01:27:51 2021 |

Jacquelynne Vaughan | V3 board, only one channel works, all components at each channel input working | Hi everyone,

I'm still looking through the forum for an answer to this question, but thought I'd go ahead and post anyway just in case it hasn't been answered yet. If it has I can take this post down.

I have a V3 board, and as far as I can tell only channel 2 gives an output. If I enable other channels using the DRS Oscilloscope software, they do show static but will not show a signal if I connect one to them (e.g. a series of subsequent square waves). A technician and I took the board out and tested all the components leading up to the microcontrollers for each channel, and everything seemed to be working fine. I thought maybe it was configured to only have one channel read an output, but I looked through the Config panel in the software and nothing seemed to indicate that.

I am a novice, and maybe I'm missing something that I didn't see in the manual. I can post screenshots if needed!

Thank you for your help! |

|

537

|

Thu Sep 29 17:26:13 2016 |

Jacob Hwang | Output Timing Drifting | Hello,

I have designed four DRS4 chips (36 channels) on my board running at 1GHz (REFCLK=488.28KHz) and ROI mode. All 4 chips' REFCLK, DWRITE, RSRLOAD, and SRCLK are buffer driven by the same source. SRCLK is set to 40MHz to reduce the readout time.

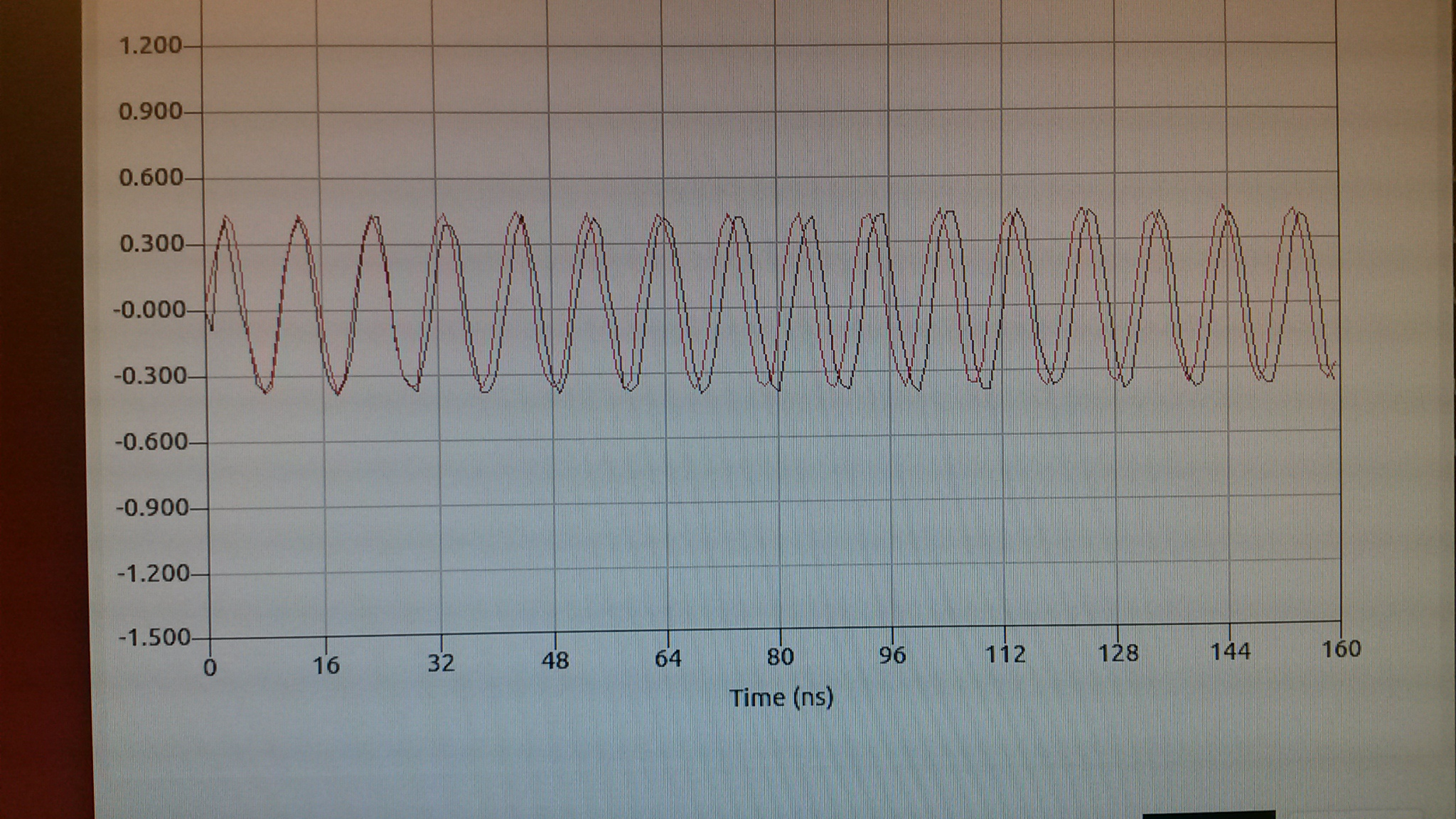

If I injected a sine waveform, buffered and splitted into all 36 channels,I noticed all 9 channels on each DRS4 chip output almost the same as expected. But the output phase from chip to chip is drifting as shown in attached picture which is from two different channels of different chips. From the few boards I have built, I found few chips are drifting more than the others and is different on every board.

The sympton look like the DRS4 internal PLL is drifting, but I checked the DTAP output on every chip and found it's dead-lock steady even I used persistance setting on my oscilloscope. Do you have any suggestion how to attack this problem? Thank you.

Jacob Hwang

|

| Attachment 1: Output_Drifting.jpg

|

|

|

471

|

Tue Jan 12 17:57:03 2016 |

Jack Bargemann | Compiling DRS-exam | I am trying to compile drs-exam, but am getting an error message I do not understand:

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_open referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_close referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_descriptor referenced in function _musb_get_device

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_write referenced in function _musb_write

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_read referenced in function _musb_read

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_configuration referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_claim_interface referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_release_interface referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_altinterface referenced in function _musb_set_altinterface

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_reset referenced in function _musb_reset

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_init referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_debug referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_busses referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_devices referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_busses referenced in function _musb_open

I have tried redownloading a different version of libusb-1.0, but the problem was not solved. What might I be doing wrong? |

|

164

|

Wed Jun 20 10:40:21 2012 |

Ivan Petrov | triger for measuring time between pulses in channels |

| Stefan Ritt wrote: |

|

| Martin Petriska wrote: |

|

| Stefan Ritt wrote: |

|

| Martin Petriska wrote: |

|

I have two BaF2 detectors with PMT connected to Ch1 and Ch2. At this time Im using external triger module to start DRS4. My evalution board is version 3 so I have no possibility to trigger on two or more pulses occurence on different channels. But I have this idea, trigger with analog trigger on channel 1 (start detector) will start measurement on all channels. After that using FPGA inside EVM to look if some value in Ch2 is bigger as treshold value for example 0,5V and if yes then send data by USB to PC, if signal in Ch2 is lower then restart measurement and wait on triger in Ch1. This way I want to eliminate false data transfer throw USB. Is this possible to implement it into DRS4 evaluation board firmware ?

Thanks.

|

It is muuuuch easier to upgrade to a V4 board!

Modification of firmware is not so easy. You have to learn and understand VHDL. Then, you have to add additional registers for this thresholds, which requires modification of the C library as well. The data inside the evaluation boards is not yet calibrated (this is only done on the C library), so you have an uncertainty of 30-40mV in this data.

|

Ok, except this, I would have a question regarding to the new trigering posibility in V4 board. At this time, I am using Ztec ZT4612 which has some pattern triger posibility. Output from this card is used as an external trigger. Regarding this I have found a problem. Pulses from PMT have about 5-8 ns width. But I need to measure time diferences between pulses in range from 0-50ns. Problem is, that coincidence between pulses is working only on short pulse area (5-8ns) when they are overlapped. Additionaly the result histogram of time diferences is proportional to the pulse shapes. I solve this problem enabling 20MHz LPF filter in ZT4612, so the pulses are wider and overlaped on larger area. But, how it is with the V4 board? Will it trigger if I have for example one 5ns pulse on begiinning of CH1 and second pulse for example 50 ns later on Ch2 with the same probability when pulses are in the same time position?

|

No.

|

Hello. I need to digitize pulses from two PMT. After pulse on first PMT I have to save all pulses from second PMT in range 200 ns (and starting pulse from the first, and time range between pulse from 1st PMT and pulses from 2nd PMT). Is it possible with DRS evaluation board? |

|

166

|

Wed Jun 20 14:36:01 2012 |

Ivan Petrov | triger for measuring time between pulses in channels |

| Stefan Ritt wrote: |

|

| Ivan Petrov wrote: |

|

Hello. I need to digitize pulses from two PMT. After pulse on first PMT I have to save all pulses from second PMT in range 200 ns (and starting pulse from the first, and time range between pulse from 1st PMT and pulses from 2nd PMT). Is it possible with DRS evaluation board?

|

If you run at 2 GSPS, you have a time window of 500 ns like on an oscilloscope. If you trigger on 1st PMT, you will get the traces of all 4 inputs for the next 500 ns. So I guess this is what you want.

|

Ok. And, If I understand correctly, the main bottleneck in data readout is USB. I.e., theoretically maximum readout rate is 500 Hz. Is it true? |

|

170

|

Mon Jul 9 14:14:48 2012 |

Ivan Petrov | Problem compiling drs_exam.cpp on windows | Hello again. I have not got evaluation board yet, but already faced some difficulties:) I'm trying to compile drs_exam.cpp on Windows 7 using dev-c++ with imagelib-2 and WxWindows 2.4.2 DevPaks installed, but nothing works. Compile log is attached. Honestly, I'm not very familiar with c++, so any suggestions will be helpful. Thank you. |

| Attachment 1: compile_log.txt

|

Compiler: Default compiler

Building Makefile: "G:\devcpp\Makefile.win"

Executing make...

make.exe -f "G:\devcpp\Makefile.win" all

g++.exe -c AboutDialog.cpp -o AboutDialog.o -I"C:/Dev-Cpp/lib/gcc/mingw32/3.4.2/include" -I"C:/Dev-Cpp/include/c++/3.4.2/backward" -I"C:/Dev-Cpp/include/c++/3.4.2/mingw32" -I"C:/Dev-Cpp/include/c++/3.4.2" -I"C:/Dev-Cpp/include"

In file included from C:/Dev-Cpp/include/wx/wx.h:15,

from DRSOscInc.h:7,

from AboutDialog.cpp:7:

C:/Dev-Cpp/include/wx/defs.h:179: error: redeclaration of C++ built-in type `int'

In file included from C:/Dev-Cpp/include/wx/memory.h:20,

from C:/Dev-Cpp/include/wx/object.h:25,

from C:/Dev-Cpp/include/wx/wx.h:16,

from DRSOscInc.h:7,

from AboutDialog.cpp:7:

C:/Dev-Cpp/include/wx/string.h:160:4: #error "Please define string case-insensitive compare for your OS/compiler"

In file included from DRSOscInc.h:12,

from AboutDialog.cpp:7:

DRSOsc.h:38:26: wx/hyperlink.h: No such file or directory

In file included from DRSOscInc.h:12,

from AboutDialog.cpp:7:

DRSOsc.h:532: error: ISO C++ forbids declaration of `wxHyperlinkCtrl' with no type

DRSOsc.h:532: error: expected `;' before '*' token

make.exe: *** [AboutDialog.o] Error 1

Execution terminated

|

|

172

|

Wed Jul 11 10:04:51 2012 |

Ivan Petrov | Problem compiling drs_exam.cpp on windows |

| Stefan Ritt wrote: |

|

| Ivan Petrov wrote: |

|

Hello again. I have not got evaluation board yet, but already faced some difficulties:) I'm trying to compile drs_exam.cpp on Windows 7 using dev-c++ with imagelib-2 and WxWindows 2.4.2 DevPaks installed, but nothing works. Compile log is attached. Honestly, I'm not very familiar with c++, so any suggestions will be helpful. Thank you.

|

I have no experience with dev-c++, so I cannot be of help here. The supported systems are Linux and Windows with MS Visual C++. But it looks like the problems are related to compiling wxWidgets, which actually you do NOT need for drs_exam.cpp. The wxWidgets library is only needed for the DRSOsc application. If you want to compile it anyhow, first learn how to compile standard WxWidgets applications from

http://www.wxwidgets.org/docs/tutorials/devcpp.htm

Best regards,

Stefan

|

Ok, this was my bad, I added some unnecessary files to project. Drs_exam compiles well with ms vc++. Thanks! |

|

764

|

Thu Jul 18 01:03:44 2019 |

Ismael Garcia | Trace Impedance | |

Hi Steffan,

I'm an engineer at UCLA developing a board with the DRS4 chip. Our team has a question on what might be the required trace impedence for the analog inputs. Can that information be provided?

Best Regards,

Ismael Garcia

|

| Attachment 1: DRS4_Analog_IN.PNG

|

|

|

766

|

Fri Jul 19 01:37:09 2019 |

Ismael Garcia | Trace Impedance | When you're refering to laying a 50 Ohm trace, you're referring to the SMA input and not the interface between the output of the Op-AMP(THS4508) buffer

and the inputs of the DRS4(IN0-IN8). Is there a recommended diffential impedance for IN0-IN8?

Ismael

| Stefan Ritt wrote: |

|

The requiremnet is the same as for any high speed analog board, there is othing special with the DRS4. If you want to terminate your line with 50 Ohms and you want a matched impedance layout, you route all lines with 50 Ohms impedance. Truth is however that nothing is perfect. The SMA connector is not exactly 50 Ohm, the PCB gets a 10-20% variation depending on the manufacturer. So even if you try hard, you will never have a 50 Ohm matched impedance. On the evaluation board we made some compromises as you have seen, but for us the board works satisfactory even with this compromises, and you can test it yourself with real hardware (namely the evaluation board). If you can do a better job, try it. But usually these compromises have only little influence on the signal quality.

Stefan

| Ismael Garcia wrote: |

|

Hi Steffan,

I'm an engineer at UCLA developing a board with the DRS4 chip. Our team has a question on what might be the required trace impedence for the analog inputs. Can that information be provided?

Best Regards,

Ismael Garcia

|

|

|

|

421

|

Tue May 19 14:14:45 2015 |

Ilja Bekman | DRS4 firmware UCF constraints | Hello, I'm using two DRS4 rev.5 boards for 8ch readout and triggering.

I needed to modify the trigger logic and implement some tweaks in the firmware, and noticed that

the firmware source in drs-5.0.2 (and 5.0.3, SVN:5339) while still compiling fine with Xilinx ISE 10, stops

doing so in the ISE 14.7 (also already in 13.2)

While the Synthesis is running through (in the new ISE it complains about using more than 100% of resources.)

The Mapping fails due to constraints (firmware/ucf/drs4_eval5.ucf) complaining about an illegal IOSTANDARD

for P_IO_PMC_USR<55> (LVDS_25).

In the newer version the wild-cards (lines 67..69 ) are not properly dealt with, it seems, and if I move the

property by hand to all the wild-carded NETs it start to recognise the LVDS_25.

But after that Place&Route fails with messages about locked Banks due to incompatible VCCO.

I'm trying to adapt the ucf file and am reading about the changes in the ISE software and constraints files, but

want to ask if some of you guys have seen the same issue and resolved it out "officially". |

|

Draft

|

Wed Oct 7 13:06:34 2015 |

Ilja Bekman | Voltage Calibration with signal on the input | |

|

69

|

Sun May 2 18:36:14 2010 |

Ignacio Di�guez Estremera | DRS4 chip model | Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera. |

|

71

|

Mon May 3 17:06:02 2010 |

Ignacio Di�guez Estremera | DRS4 chip model |

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards. |

|

73

|

Mon May 3 23:21:55 2010 |

Ignacio Di�guez Estremera | DRS4 chip model |

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards.

|

I just checked and realized that we are not allowed to give out the "huge" model since it contains parameters from the chip manufacturer's library which are confidentially.

|

Thank you for the effort anyway.

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-) |

|