| ID |

Date |

Author |

Subject |

|

112

|

Sat Feb 19 17:25:29 2011 |

S S Upadhya | how to synchronize Sampling frequency of two evaluation boards | Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya |

|

113

|

Sat Feb 19 22:46:35 2011 |

Stefan Ritt | how to synchronize Sampling frequency of two evaluation boards |

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board. |

|

114

|

Mon Feb 21 08:10:31 2011 |

Stefan Ritt | how to synchronize Sampling frequency of two evaluation boards |

| Stefan Ritt wrote: |

|

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board.

|

Well, one thing you can do is to generate an external trigger and send it to the external trigger input of both cards. Then you can determine the time in respect to the trigger point in both boards. But since the trigger cell jitters by 2-3 cells in each chip, the accuracy is limited to about 1-2 ns when running at 2 GS/s. |

|

115

|

Mon Feb 21 12:42:33 2011 |

S S Upadhya | how to synchronize Sampling frequency of two evaluation boards |

| Stefan Ritt wrote: |

|

| Stefan Ritt wrote: |

|

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board.

|

Well, one thing you can do is to generate an external trigger and send it to the external trigger input of both cards. Then you can determine the time in respect to the trigger point in both boards. But since the trigger cell jitters by 2-3 cells in each chip, the accuracy is limited to about 1-2 ns when running at 2 GS/s.

|

Dear Stefan,

Thanks for the second suggestion. I wanted to do feasibility study of DRS4 application to our requirement in the experiment

Thank you again sir,

Upadhya |

|

774

|

Mon Oct 14 09:32:33 2019 |

Danyang | how to acquire the stop position with channel cascading | Hi Steffan,

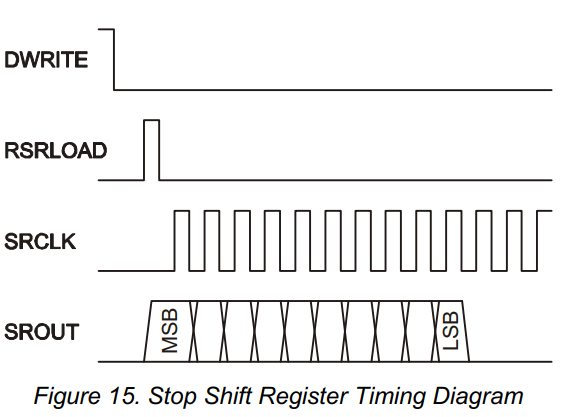

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn) |

| Attachment 1: Capture.PNG

|

|

|

775

|

Mon Oct 14 10:14:46 2019 |

Stefan Ritt | how to acquire the stop position with channel cascading | You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

776

|

Mon Oct 14 11:45:06 2019 |

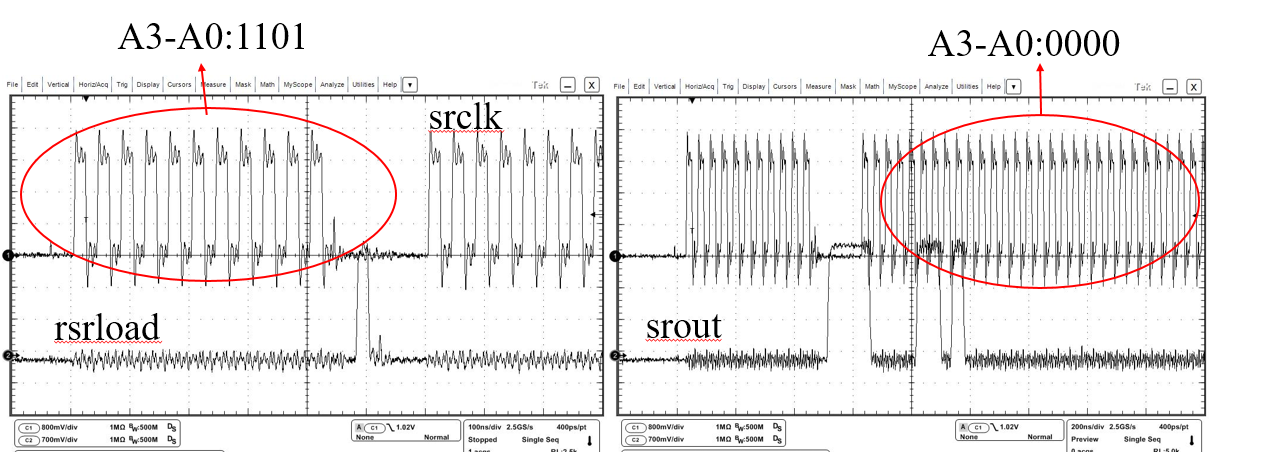

Danyang | how to acquire the stop position with channel cascading | I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

| Attachment 1: Capture.PNG

|

|

|

777

|

Mon Oct 14 12:56:13 2019 |

Stefan Ritt | how to acquire the stop position with channel cascading | Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

778

|

Mon Oct 14 13:44:26 2019 |

Danyang | how to acquire the stop position with channel cascading | Yes, firstly I configured the chip with 4x2048 bins by setting the Write Shift Register to 01010101b, A3-A0 keeps 1101----> secondly I enabled the domino wave, wait some time for stable, A3-A0 keeps 1111 ---->thirdly stops the domino wave when the trigger comes, A3-A0 keeps 1101 (or 1010, 0000)----> forthly send the clock pulse to the srclk pin, A3-A0 keeps 1101, srout pin keeps low----> fifthly enable rsrload, A3-A0 (0000-1000), srout pin reacts nomally. I think the cascading is worked when I checked the waveform on the oscilloscope. Is there any step I missed?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

|

779

|

Mon Oct 14 15:27:09 2019 |

Stefan Ritt | how to acquire the stop position with channel cascading | If you configure the Write Shift Register with 01010101b, then all you have to do after a trigger is to set A3-A0 to 1101. The WSROUT pin shows you then either ther state 01010101b or 10101010b, you the pin should be 1 or 0, and that's all you need. The Write Shift Register is NOT routed to the SROUT pin, you only see it at the WSROUT pin.

Stefan

| Danyang wrote: |

|

Yes, firstly I configured the chip with 4x2048 bins by setting the Write Shift Register to 01010101b, A3-A0 keeps 1101----> secondly I enabled the domino wave, wait some time for stable, A3-A0 keeps 1111 ---->thirdly stops the domino wave when the trigger comes, A3-A0 keeps 1101 (or 1010, 0000)----> forthly send the clock pulse to the srclk pin, A3-A0 keeps 1101, srout pin keeps low----> fifthly enable rsrload, A3-A0 (0000-1000), srout pin reacts nomally. I think the cascading is worked when I checked the waveform on the oscilloscope. Is there any step I missed?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

|

|

780

|

Tue Oct 15 08:14:17 2019 |

Danyang | how to acquire the stop position with channel cascading | Thanks a lot. The problem is solved when A3-A0 is set 1101 and srclk keeps low.

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

If you configure the Write Shift Register with 01010101b, then all you have to do after a trigger is to set A3-A0 to 1101. The WSROUT pin shows you then either ther state 01010101b or 10101010b, you the pin should be 1 or 0, and that's all you need. The Write Shift Register is NOT routed to the SROUT pin, you only see it at the WSROUT pin.

Stefan

| Danyang wrote: |

|

Yes, firstly I configured the chip with 4x2048 bins by setting the Write Shift Register to 01010101b, A3-A0 keeps 1101----> secondly I enabled the domino wave, wait some time for stable, A3-A0 keeps 1111 ---->thirdly stops the domino wave when the trigger comes, A3-A0 keeps 1101 (or 1010, 0000)----> forthly send the clock pulse to the srclk pin, A3-A0 keeps 1101, srout pin keeps low----> fifthly enable rsrload, A3-A0 (0000-1000), srout pin reacts nomally. I think the cascading is worked when I checked the waveform on the oscilloscope. Is there any step I missed?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

|

|

|

832

|

Mon Sep 6 14:42:23 2021 |

Jiaolong | how to acquire the stop channel with 2x4096 cascading | Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong |

|

834

|

Sat Sep 18 15:47:50 2021 |

Stefan Ritt | how to acquire the stop channel with 2x4096 cascading | The problem must be on your side, since the Write Shift Register readout works in other applications with the DRS4 chip. So I can only speculate what could be wrong:

- Do you really properly set the WSR? When you program it with 00010001b, add 8 more clock cycles and you should see the 00010001b pattern at WSROUT.

- Do all tests with an oscilloscope, to avoid potential problems in your FPGA firmware (like an input configures as an output by mistake).

- DWRITE must be high to see the contents of the WSR at the WSROUT pin, maybe that’s your mistake, see datasheet p 5 of 16.

- To see the contents of the WSR at SROUT, A0-3 must be 1101b, please check with your oscilloscope

- The addresses A0-A3 are simply connected to a multiplexer, so no clock is necessary after the addresses change

Stefan

| Jiaolong wrote: |

|

Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong

|

|

|

Draft

|

Fri Nov 5 01:10:25 2021 |

Jiaolong | how to acquire the stop channel with 2x4096 cascading |

| Jiaolong wrote: |

|

Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong

|

|

|

850

|

Fri Nov 5 01:12:10 2021 |

Jiaolong | how to acquire the stop channel with 2x4096 cascading | Thanks for your advice. The problem has been solved by setting the srin again while reading out from srout.

| Stefan Ritt wrote: |

|

The problem must be on your side, since the Write Shift Register readout works in other applications with the DRS4 chip. So I can only speculate what could be wrong:

- Do you really properly set the WSR? When you program it with 00010001b, add 8 more clock cycles and you should see the 00010001b pattern at WSROUT.

- Do all tests with an oscilloscope, to avoid potential problems in your FPGA firmware (like an input configures as an output by mistake).

- DWRITE must be high to see the contents of the WSR at the WSROUT pin, maybe that’s your mistake, see datasheet p 5 of 16.

- To see the contents of the WSR at SROUT, A0-3 must be 1101b, please check with your oscilloscope

- The addresses A0-A3 are simply connected to a multiplexer, so no clock is necessary after the addresses change

Stefan

| Jiaolong wrote: |

|

Hi Steffan,

I have a question about how to acquire the stop channel:

Process: Configure the Write Shift Register with 00010001b to achieve 4-channel cascading, then after a trigger, set A3-A0 to 1101, sclk keeps 0.

Result: the WSROUT pin keeps 0, the SROUT pin has no clock pulse as written in datasheet, but keeps always 1 or 0. It can be seen the stop channel is channel 0 or channel 1, but no situation to represtent channel 3 or channel 4. And if set sclk with 8 pulses, the WSROUT and SROUT both keep 0.

What should I pay attention to? Looking forward to your reply.

Jiaolong

|

|

|

|

299

|

Wed Nov 6 11:53:28 2013 |

Dmitry Hits | flickering screen for drsosc | Hi,

I have install drs software on ASUS EeeBox with Ubuntu 12.04 LTS. When I try to use ./drsosc the oscilloscope window flickers. Can you suggest what might be the problem?

Here is some more info:

******************************************************

System:

Ubuntu 12.04 LTS

Memory: 992.9 MiB

CPU: Intel Atom CPU N270 @ 1.6GHz x 2

32 Bit

Disc: 156.5 GB

***************************************

Software:

Due to version Ubuntu I had to install the wxWidgets from source (wxWidgets with x11)

Thank you,

Dmitry. |

|

300

|

Wed Nov 6 12:25:31 2013 |

Stefan Ritt | flickering screen for drsosc |

| Dmitry Hits wrote: |

|

Hi,

I have install drs software on ASUS EeeBox with Ubuntu 12.04 LTS. When I try to use ./drsosc the oscilloscope window flickers. Can you suggest what might be the problem?

Here is some more info:

******************************************************

System:

Ubuntu 12.04 LTS

Memory: 992.9 MiB

CPU: Intel Atom CPU N270 @ 1.6GHz x 2

32 Bit

Disc: 156.5 GB

***************************************

Software:

Due to version Ubuntu I had to install the wxWidgets from source (wxWidgets with x11)

Thank you,

Dmitry.

|

This problem is new. Even on a slower Raspberry Pi we did not see any flickering. Have you tried a different version of wxWidgets? |

|

304

|

Mon Nov 18 11:20:15 2013 |

Dmitry Hits | flickering screen for drsosc |

| Stefan Ritt wrote: |

|

| Dmitry Hits wrote: |

|

Hi,

I have install drs software on ASUS EeeBox with Ubuntu 12.04 LTS. When I try to use ./drsosc the oscilloscope window flickers. Can you suggest what might be the problem?

Here is some more info:

******************************************************

System:

Ubuntu 12.04 LTS

Memory: 992.9 MiB

CPU: Intel Atom CPU N270 @ 1.6GHz x 2

32 Bit

Disc: 156.5 GB

***************************************

Software:

Due to version Ubuntu I had to install the wxWidgets from source (wxWidgets with x11)

Thank you,

Dmitry.

|

This problem is new. Even on a slower Raspberry Pi we did not see any flickering. Have you tried a different version of wxWidgets?

|

yes the problem was in wxWidgets, I have downgraded the ubuntu version and installed packaged version of wxWidgets. Now it works without problems.

Thank you,

Dmitry. |

|

63

|

Tue Apr 13 10:45:18 2010 |

lorenzo neri | evaluation board used like a counter | Hi all

it is possible to use the evaluation board like a counter?

I'm interested in the arriving time of all self trigger event in to a channel.

the input signal are 2V TTL of 10 ns at 50ohm, and the time acquisition window is 1 second.

can someone help me?

thanks in advance,

Lorenzo |

|

64

|

Tue Apr 13 13:12:43 2010 |

Stefan Ritt | evaluation board used like a counter |

| lorenzo neri wrote: |

|

Hi all

it is possible to use the evaluation board like a counter?

I'm interested in the arriving time of all self trigger event in to a channel.

the input signal are 2V TTL of 10 ns at 50ohm, and the time acquisition window is 1 second.

|

The evaluation board is as good or bad as an digital oscilloscope to work like a counter. At 1 GSPS, you have a window of one microsecond, which is certainly too short for your application. |

|