| ID |

Date |

Author |

Subject |

|

500

|

Mon Apr 4 11:31:34 2016 |

Stefan Ritt | DRS Oscilloscope freezing after a long run |

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

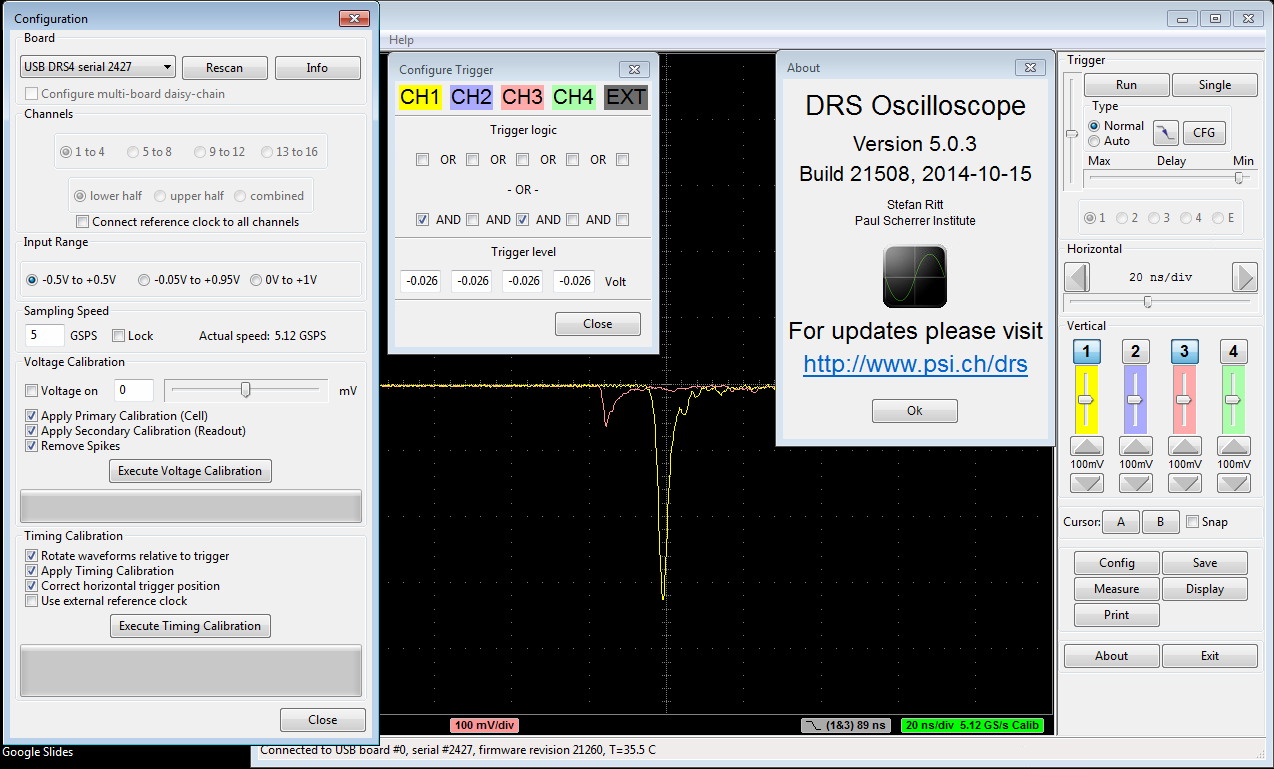

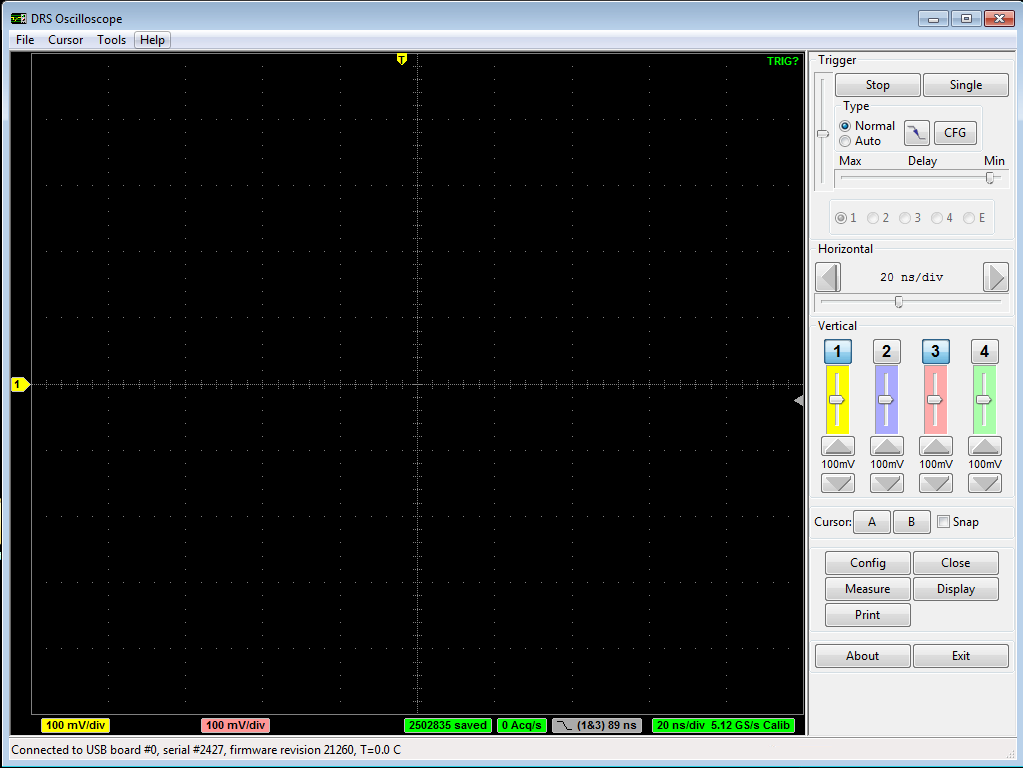

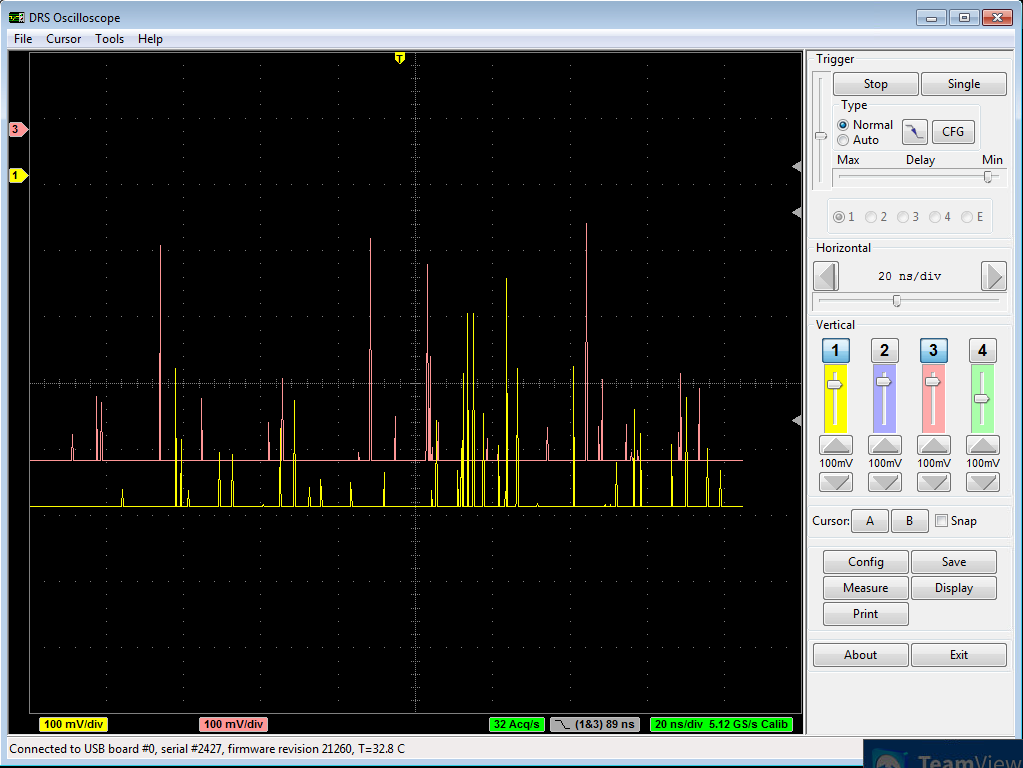

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

|

499

|

Sun Apr 3 22:34:28 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal |

Thanks, great!

| Chris Thompson wrote: |

|

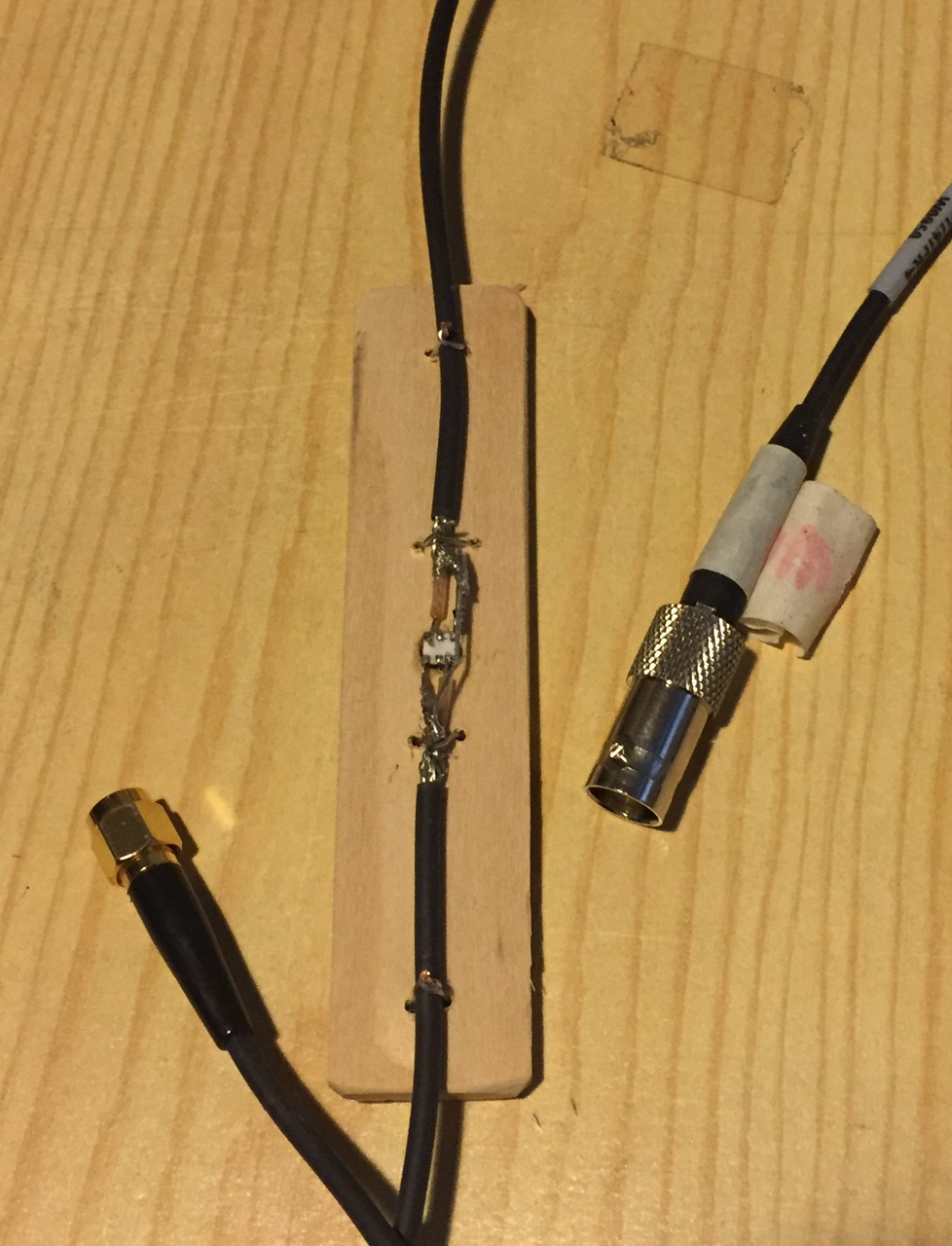

No there are no other components. I put a photo of the inverter with its cables SMA and one end, BNC at the other. You can see it is very small. I glued the inverter to a piece of thin plywood, and fixed the cables to it before attempting to solder them to the pads on the ferite bead support

| Abaz Kryemadhi wrote: |

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

|

|

498

|

Sun Apr 3 22:10:19 2016 |

Chris Thompson | Trigger on the And of a positive and negative signal |

No there are no other components. I put a photo of the inverter with its cables SMA and one end, BNC at the other. You can see it is very small. I glued the inverter to a piece of thin plywood, and fixed the cables to it before attempting to solder them to the pads on the ferite bead support

| Abaz Kryemadhi wrote: |

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

| Attachment 1: Pulse_inverter.jpg

|

|

|

497

|

Sat Apr 2 17:22:34 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal |

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

496

|

Sat Apr 2 11:41:07 2016 |

Stefan Ritt | Question about timimng calibration |

The evaluation board normally has 1024 bins per channel. We offer an option with 2048 bins using channel cascading, to capture longer waveform windows. The binary data format is however defined as having 1024 bins. Therefore, for the 2048 bin boards, the software averages over two adjacent cells and saves effectively 1024 bins. The noise of each bin improves this way by sqrt(2). The time however is not very well defined, since you average the voltage of two bins. Therefore, I simple also average over the time of the two bins. Maybe this is not the best way, so feel free to change this.

Stefan

| Felix Bachmair wrote: |

|

Hi,

I am trying to understand some details about the timing calibration.

We wrote our own code but we more or less use the ideas of the Oscilloscope class.

In the binary file writing of in the function Osci.cpp::SaveWaveforms() (line 924ff)

the following code is executed:

if (m_waveDepth == 2048) {

t = (tcal[j]+tcal[j+1])/2;

j++;

} else

t = tcal[j];

I do not understand the averaging of the to adjacent calibration constants. Could you explain this? Do one have two measurements?

Cheers

Felix

|

|

|

495

|

Sat Apr 2 11:21:10 2016 |

Felix Bachmair | Question about timimng calibration |

Hi,

I am trying to understand some details about the timing calibration.

We wrote our own code but we more or less use the ideas of the Oscilloscope class.

In the binary file writing of in the function Osci.cpp::SaveWaveforms() (line 924ff)

the following code is executed:

if (m_waveDepth == 2048) {

t = (tcal[j]+tcal[j+1])/2;

j++;

} else

t = tcal[j];

I do not understand the averaging of the to adjacent calibration constants. Could you explain this? Do one have two measurements?

Cheers

Felix

|

|

494

|

Fri Apr 1 22:09:07 2016 |

Chris Thompson | Trigger on the And of a positive and negative signal |

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

493

|

Fri Apr 1 01:30:40 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal |

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

492

|

Thu Mar 31 20:48:00 2016 |

Chris Thompson | Trigger on the And of a positive and negative signal |

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

491

|

Thu Mar 31 20:38:05 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal |

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

490

|

Thu Mar 31 20:34:25 2016 |

Stefan Ritt | Trigger on the And of a positive and negative signal |

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

489

|

Thu Mar 31 19:44:38 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal |

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

488

|

Thu Mar 31 19:35:06 2016 |

Stefan Ritt | Trigger on the And of a positive and negative signal |

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

487

|

Thu Mar 31 19:30:26 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal |

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz |

|

486

|

Tue Mar 22 12:54:41 2016 |

Stefan Ritt | |

Yes this is correct. But it is a sample-and-hold circuit. So the sampling cell follows the input for 3.2 ns, then samples and holds the current value at the end of the period.

| Dominik Neise wrote: |

|

Hello Stefan,

I just stumbled again over a phrase in the DRS4 datasheet I never really understood, but didn't find the time to ask.

On page 8 it says: "An internal circuit ensures that the write signal is always 16 cells wide."

So when I look at a single channel, do I understand correctly, that at any given time during sampling, always 16 cells are open, i.e. 16 cells are connected to the analog inputs? So when the domino frequency is e.g. 5GHz then each cell sees the analog input not for 200ps but for 3.2ns correct?

|

|

|

485

|

Mon Mar 21 10:38:27 2016 |

Daniel Dribin | DRS Oscilloscope freezing after a long run |

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

| Attachment 1: drs_settings.png

|

|

| Attachment 2: empty_drs.png

|

|

| Attachment 3: drs_ofset.png

|

|

|

484

|

Fri Mar 11 19:50:18 2016 |

Dominik Neise | |

Hello Stefan,

I just stumbled again over a phrase in the DRS4 datasheet I never really understood, but didn't find the time to ask.

On page 8 it says: "An internal circuit ensures that the write signal is always 16 cells wide."

So when I look at a single channel, do I understand correctly, that at any given time during sampling, always 16 cells are open, i.e. 16 cells are connected to the analog inputs? So when the domino frequency is e.g. 5GHz then each cell sees the analog input not for 200ps but for 3.2ns correct? |

|

483

|

Wed Mar 9 09:57:20 2016 |

Christian D | LabView |

Hi,

I would like to use the DRS4 board with LabView for fast readout.

Do you know anyone who has written a VI for that?

Thanks,

Christian |

|

482

|

Mon Feb 29 14:09:21 2016 |

Stefan Ritt | two DRS4 boards configuration with 2048 samples each |

The multi-board mode has never been tested with 2048 samples, so is very likely not to work. I don't know yet how much work this will be to fix, but I'm on a business trip the next three weeks and probably will only have time to look at it when I return.

Stefan

| Dmitry Hits wrote: |

|

Dear Stefan,

I daisy-chained two boards (master sn#: 2514 - slave sn#: 2513) each with 2048 samples. However, when I use drsosc and put check mark in "configure multi-board daisy-chain" I see only 1024 samples. Namely, the first 1024 samples, the last part is missing. When I remove this check mark, I see all 2048 samples. Is there a simple software fix for this or is it a more involved firmware limitation?

Other parameters: software version: 5.0.4, firmware version 21305, configured for 0.7 GSPS, display at 500 ns/div

Thank you,

Dmitry Hits.

|

|

|

481

|

Mon Feb 29 13:33:06 2016 |

Dmitry Hits | two DRS4 boards configuration with 2048 samples each |

Dear Stefan,

I daisy-chained two boards (master sn#: 2514 - slave sn#: 2513) each with 2048 samples. However, when I use drsosc and put check mark in "configure multi-board daisy-chain" I see only 1024 samples. Namely, the first 1024 samples, the last part is missing. When I remove this check mark, I see all 2048 samples. Is there a simple software fix for this or is it a more involved firmware limitation?

Other parameters: software version: 5.0.4, firmware version 21305, configured for 0.7 GSPS, display at 500 ns/div

Thank you,

Dmitry Hits. |