| ID |

Date |

Author |

Subject |

|

199

|

Mon Dec 3 11:40:35 2012 |

Gyuhee Kim | Another question about using multi boards. |

| Stefan Ritt wrote: |

|

| Gyuhee Kim wrote: |

|

Hi.

I asked about using multi boards some days ago, and I got answer to use external trigger. (Thanks Stefan!)

And here is another question. I made two external triggers and try to acquire coincidence data using two boards. but DRS Oscilloscope program can connect only one board and don`t acquire both of them simultaneously.

So I tried to use two computer for each board separately, but, well, you already know, I failed to acquire because two computers don`t promise to synchronize the two boards acquisition.

Is there any method to solve this problem?

1. I want to acquire coincidence data from the two DRS 4 Evaluation board V4 simultaneosly.

2. I have external trigger to provide the two boards at the same time.

3. How can I get data from the two boards?

Best regards.

Gyuhee.

|

You have to write your own program. DRS Oscilloscope does not (yet) support this. Take drs_exam.cpp as a starting point and try to extend it to two boards. One tricky point is that the external trigger may only fire AFTER the two boards have been read out. So you need some means of re-enabling the external trigger after you read out both boards.

Stefan

|

That`s very bad news for me. I don`t have much time to study & write C programming...

Anyway, Thank you very much Stefan.

Best regards.

Gyuhee. |

|

198

|

Mon Dec 3 09:18:09 2012 |

Stefan Ritt | Another question about using multi boards. |

| Gyuhee Kim wrote: |

|

Hi.

I asked about using multi boards some days ago, and I got answer to use external trigger. (Thanks Stefan!)

And here is another question. I made two external triggers and try to acquire coincidence data using two boards. but DRS Oscilloscope program can connect only one board and don`t acquire both of them simultaneously.

So I tried to use two computer for each board separately, but, well, you already know, I failed to acquire because two computers don`t promise to synchronize the two boards acquisition.

Is there any method to solve this problem?

1. I want to acquire coincidence data from the two DRS 4 Evaluation board V4 simultaneosly.

2. I have external trigger to provide the two boards at the same time.

3. How can I get data from the two boards?

Best regards.

Gyuhee.

|

You have to write your own program. DRS Oscilloscope does not (yet) support this. Take drs_exam.cpp as a starting point and try to extend it to two boards. One tricky point is that the external trigger may only fire AFTER the two boards have been read out. So you need some means of re-enabling the external trigger after you read out both boards.

Stefan |

|

197

|

Mon Dec 3 08:32:28 2012 |

Gyuhee Kim | Another question about using multi boards. | Hi.

I asked about using multi boards some days ago, and I got answer to use external trigger. (Thanks Stefan!)

And here is another question. I made two external triggers and try to acquire coincidence data using two boards. but DRS Oscilloscope program can connect only one board and don`t acquire both of them simultaneously.

So I tried to use two computer for each board separately, but, well, you already know, I failed to acquire because two computers don`t promise to synchronize the two boards acquisition.

Is there any method to solve this problem?

1. I want to acquire coincidence data from the two DRS 4 Evaluation board V4 simultaneosly.

2. I have external trigger to provide the two boards at the same time.

3. How can I get data from the two boards?

Best regards.

Gyuhee. |

|

196

|

Wed Nov 28 16:54:46 2012 |

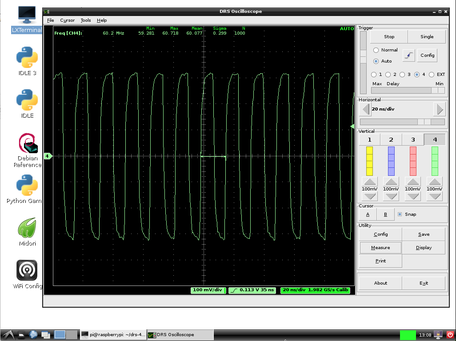

Stefan Ritt | DRS Oscilloscope for Raspberry Pi and Mac OSX 10.8 | I made a pre-compiled package for Mac OSX 10.8 (Mountain Lion), so one should be able to install the DRS Oscilloscope software with one mouse click on a recent Mac.

The Makefile in the tar ball now also supports OSX 10.8, so one could even compile it from the sources on a Mac, after libusb-1.0 and wxWidgets have been installed. That might then also work on older versions of OSX.

In addition, the software has been adaptes so that it compiles nicely on a Raspberry Pi (http://www.raspberrypi.org), a screenshot has been attached. Together with a Raspberry Pi and an old screen, the evaluation board is one of the cheapest available oscilloscopes.

|

| Attachment 1: screenshot_pi.png

|

|

|

195

|

Wed Nov 21 08:48:00 2012 |

Gyuhee Kim | Question for using Multi board |

| Stefan Ritt wrote: |

|

| Gyuhee Kim wrote: |

|

Hi.

I have 2 DRS4 evaluation V4 boards, and I want to use these 2 board to multi board DAQ system for 4 ch vs 4 ch DAQ.

But there is no option for multi board use. I just only find the multi board trigger mode check button on DRS4 Oscilloscope program, but I couldn`t check.

Is there any method to use multi board?

Best regards.

Gyuhee.

|

This mode is not yet implemented in firmware. Maybe I find some time towards the end of this year to add this. At the moment, you have to build and external trigger to synchronize the two boards. There are also 16-channel boards on the market where you would not need a multi-board mode. Just Google for "DT5742".

/Stefan

|

Thanks Stefan.

I will build external trigger system. |

|

194

|

Wed Nov 21 08:38:26 2012 |

Stefan Ritt | Question for using Multi board |

| Gyuhee Kim wrote: |

|

Hi.

I have 2 DRS4 evaluation V4 boards, and I want to use these 2 board to multi board DAQ system for 4 ch vs 4 ch DAQ.

But there is no option for multi board use. I just only find the multi board trigger mode check button on DRS4 Oscilloscope program, but I couldn`t check.

Is there any method to use multi board?

Best regards.

Gyuhee.

|

This mode is not yet implemented in firmware. Maybe I find some time towards the end of this year to add this. At the moment, you have to build and external trigger to synchronize the two boards. There are also 16-channel boards on the market where you would not need a multi-board mode. Just Google for "DT5742".

/Stefan |

|

193

|

Wed Nov 21 08:34:52 2012 |

Gyuhee Kim | Question for using Multi board | Hi.

I have 2 DRS4 evaluation V4 boards, and I want to use these 2 board to multi board DAQ system for 4 ch vs 4 ch DAQ.

But there is no option for multi board use. I just only find the multi board trigger mode check button on DRS4 Oscilloscope program, but I couldn`t check.

Is there any method to use multi board?

Best regards.

Gyuhee. |

|

192

|

Tue Nov 13 11:26:32 2012 |

Stefan Ritt | GetWave |

| Martin Petriska wrote: |

|

I have some question according to GetWave function. In drs_exam.cpp simple GetWave(0,0,wave_array[]) etc...is used. Is there primary (cell) calibration, secondary calibration (Readout) and remove Spikes used, as in DRS Oscilloscope application?

|

Yes, yes, no. To get spike removals, you need the function RemoveSpikes from Osci.cpp in the DRSOsc project. |

|

191

|

Thu Nov 1 20:46:53 2012 |

hongwei yang | DRS4 firmware |

| Stefan Ritt wrote: |

|

| hongwei yang wrote: |

|

| hongwei yang wrote: |

|

| Stefan Ritt wrote: |

|

| hongwei yang wrote: |

|

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point?

thanks

Hongwei

|

The "and" in the trigger section means now "coincidence". So the V4 board can trigger on a coincidence between two or more channels. If there is no pulse at the same time on the coincidence channels, the board will of course not trigger. The according firmware was introduced in V4, so please look at drs4_eval4_app.vhd (not eval3).

I just realized that the V4 firmware might be missing in the distribution, so I have attached it here. Look for drs_ctl_trigger_config.

Best regards,

Stefan

|

Ah, great, that helps, Thank you!

Hongwei

|

By the way, will there be a drs4_eval4.vhd as well?

|

Here it is.

|

Thanks. have a good day |

|

190

|

Thu Nov 1 20:32:03 2012 |

Stefan Ritt | DRS4 firmware |

| hongwei yang wrote: |

|

| hongwei yang wrote: |

|

| Stefan Ritt wrote: |

|

| hongwei yang wrote: |

|

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point?

thanks

Hongwei

|

The "and" in the trigger section means now "coincidence". So the V4 board can trigger on a coincidence between two or more channels. If there is no pulse at the same time on the coincidence channels, the board will of course not trigger. The according firmware was introduced in V4, so please look at drs4_eval4_app.vhd (not eval3).

I just realized that the V4 firmware might be missing in the distribution, so I have attached it here. Look for drs_ctl_trigger_config.

Best regards,

Stefan

|

Ah, great, that helps, Thank you!

Hongwei

|

By the way, will there be a drs4_eval4.vhd as well?

|

Here it is. |

| Attachment 1: drs4_eval4.vhd

|

--#############################################################

-- Author : Stefan Ritt

-- Contents : DRS4 Evaluation Board FPGA top level entity

-- $Id: drs4_eval4.vhd 13988 2009-08-03 15:28:19Z ritt $

--#############################################################

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use work.drs4_pack.all;

entity drs4_eval4 is

port (

-- Quartz

P_I_CLK33 : in std_logic;

P_I_CLK66 : in std_logic;

-- Test points

P_IO_J45 : inout std_logic;

P_IO_J46 : inout std_logic;

P_I_J47 : in std_logic;

P_IO_J48 : inout std_logic;

P_IO_J49 : inout std_logic;

-- analog triggers

P_I_ATRG1 : in std_logic;

P_I_ATRG2 : in std_logic;

P_I_ATRG3 : in std_logic;

P_I_ATRG4 : in std_logic;

-- external trigger

P_IO_ETRG_IN : inout std_logic;

P_O_ETRG_IND : out std_logic;

P_IO_ETRG_OUT : inout std_logic;

P_O_ETRG_OUTD : out std_logic;

-- external (MMCX clock) clock

P_IO_ECLK_IN : inout std_logic;

P_O_ECLK_IND : out std_logic;

P_IO_ECLK_OUT : inout std_logic;

P_O_ECLK_OUTD : out std_logic;

-- LEDs

P_O_LED0 : out std_logic;

P_O_LED1 : out std_logic;

-- Lines to/from Cy7C68013A microcontroller

P_IO_UC_SLOE : inout std_logic;

P_IO_UC_SLRD : inout std_logic;

P_IO_UC_SLWR : inout std_logic;

P_IO_UC_SLCS : inout std_logic;

P_IO_UC_PKTEND : inout std_logic;

P_IO_UC_FIFOADR0 : inout std_logic;

P_IO_UC_FIFOADR1 : inout std_logic;

P_IO_UC_FLAGA : inout std_logic;

P_IO_UC_FLAGB : inout std_logic;

P_IO_UC_FLAGC : inout std_logic;

P_I_UC_PA0 : in std_logic;

P_IO_UC_FD : inout std_logic_vector(15 downto 0);

-- PMC connector

P_IO_PMC_USR : inout std_logic_vector(63 downto 0)

);

end drs4_eval4;

architecture arch of drs4_eval4 is

component usr_clocks

port (

P_I_CLK33 : in std_logic;

P_I_CLK66 : in std_logic;

O_CLK33 : out std_logic;

O_CLK33_NODLL : out std_logic;

O_CLK66 : out std_logic;

O_CLK132 : out std_logic;

O_CLK264 : out std_logic;

I_PS_VALUE : in std_logic_vector(7 downto 0);

O_CLK_PS : out std_logic;

O_LOCKED : out std_logic;

O_DEBUG1 : out std_logic;

O_DEBUG2 : out std_logic

);

end component;

component usb2_racc is

port (

-- Clock signals

-- ------------------------

I_RESET : in std_logic;

I_CLK33 : in std_logic;

-- Lines to/from Cy7C68013A microcontroller

-- -----------------------------------

P_IO_UC_SLOE : inout std_logic;

P_IO_UC_SLRD : inout std_logic;

P_IO_UC_SLWR : inout std_logic;

P_IO_UC_SLCS : inout std_logic;

P_IO_UC_PKTEND : inout std_logic;

P_IO_UC_FIFOADR0 : inout std_logic;

P_IO_UC_FIFOADR1 : inout std_logic;

P_IO_UC_FLAGA : inout std_logic;

P_IO_UC_FLAGB : inout std_logic;

P_IO_UC_FLAGC : inout std_logic;

P_IO_UC_FD : inout std_logic_vector(15 downto 0);

-- Simple bus interface to on-chip RAM

-- --------------------------------------------------

O_LOCBUS_ADDR : out std_logic_vector(31 downto 0);

I_LOCBUS_D_RD : in std_logic_vector(31 downto 0);

O_LOCBUS_D_WR : out std_logic_vector(31 downto 0);

O_LOCBUS_WE : out std_logic;

-- Status & control registers

-----------------------------

O_CONTROL_REG_ARR : out type_control_reg_arr;

I_STATUS_REG_ARR : in type_status_reg_arr;

O_CONTROL_TRIG_ARR : out type_control_trig_arr;

O_CONTROL0_BIT_TRIG_ARR : out std_logic_vector(31 downto 0);

-- Debug signals

-- -------------

O_DEBUG : out std_logic

);

end component;

component usb_dpram is

port (

I_RESET : in std_logic;

I_CLK_A : in std_logic;

I_ADDR_A : in std_logic_vector(31 downto 0);

I_WE_A : in std_logic;

O_D_RD_A : out std_logic_vector(31 downto 0);

I_D_WR_A : in std_logic_vector(31 downto 0);

I_CLK_B : in std_logic;

I_ADDR_B : in std_logic_vector(31 downto 0);

I_WE_B : in std_logic;

O_D_RD_B : out std_logic_vector(31 downto 0);

I_D_WR_B : in std_logic_vector(31 downto 0)

);

end component;

component drs4_eval4_app is

port (

I_CLK33 : in std_logic; -- 33 MHz, sychronised to clk33_nodll

I_CLK66 : in std_logic; -- 66 MHz, same phase as clk33

I_CLK132 : in std_logic; -- 132 MHz, random phase in respect to clk33

I_CLK264 : in std_logic; -- 264 MHz, random phase in respect to clk33

O_CLK_PS_VALUE : out std_logic_vector(7 downto 0); -- value for phase shift

I_CLK_PS : in std_logic; -- phase shifted in respect to clk33

I_RESET : in std_logic; -- active high power-up reset

-- analog triggers

I_ANA_TRG : in std_logic_vector(3 downto 0);

-- external trigger

IO_ETRG_IN : inout std_logic;

O_ETRG_IND : out std_logic;

IO_ETRG_OUT : inout std_logic;

O_ETRG_OUTD : out std_logic;

-- external (MMCX clock) clock

IO_ECLK_OUT : inout std_logic;

IO_ECLK_IN : inout std_logic;

-- PMC

P_IO_PMC_USR : inout std_logic_vector(63 downto 0);

-- Simple bus interface to DPRAM

O_DPRAM_CLK : out std_logic;

O_DPRAM_ADDR : out std_logic_vector(31 downto 0);

O_DPRAM_D_WR : out std_logic_vector(31 downto 0);

O_DPRAM_WE : out std_logic;

I_DPRAM_D_RD : in std_logic_vector(31 downto 0);

-- Control & status registers from system FPGA interface

I_CONTROL_REG_ARR : in type_control_reg_arr;

O_STATUS_REG_ARR : out type_status_reg_arr;

I_CONTROL_TRIG_ARR : in type_control_trig_arr;

I_CONTROL0_BIT_TRIG_ARR : in std_logic_vector(31 downto 0);

-- LEDs signals

O_LED_RED : out std_logic;

O_LED_YELLOW : out std_logic;

-- Debug signals

O_DEBUG1 : out std_logic;

O_DEBUG2 : out std_logic

);

end component;

signal VCC: std_logic;

signal GND: std_logic;

-- reset signal

-- -------------

signal global_reset : std_logic; -- active high power-up reset

-- clocks & related signals

-- ------------------------

signal clk33_nodll : std_logic; -- external 33 MHz clock (global clock net)

signal clk33 : std_logic; -- 33 MHz DLL output

signal clk66 : std_logic;

signal clk132 : std_logic;

signal clk264 : std_logic;

signal clk_ps_value : std_logic_vector(7 downto 0);

signal clk_ps : std_logic; -- special phase shifted clock

signal usr_clks_dlls_locked : std_logic; -- high if clock DLLs for clkxx have locked

-- user application signals for Locbus interface

-- ---------------------------------------------

signal locbus_addr : std_logic_vector(31 downto 0);

signal locbus_d_rd : std_logic_vector(31 downto 0);

signal locbus_d_wr : std_logic_vector(31 downto 0);

signal locbus_we : std_logic;

-- user application signals for DPRAM interface

-- --------------------------------------------

signal dpram_clk : std_logic;

signal dpram_addr : std_logic_vector(31 downto 0);

signal dpram_we : std_logic;

signal dpram_d_wr : std_logic_vector(31 downto 0);

signal dpram_d_rd : std_logic_vector(31 downto 0);

-- register signals for data exchange with microcontroller

-- -------------------------------------------------------

signal control_reg_arr : type_control_reg_arr;

signal status_reg_arr : type_status_reg_arr;

signal control_trig_arr: type_control_trig_arr;

signal control0_bit_trig_arr : std_logic_vector(31 downto 0);

-- LEDs

-- ----

signal o_led_red : std_logic;

signal o_led_yellow : std_logic;

-- Trigger

-- -------

signal io_etrg_in : std_logic;

signal o_etrg_ind : std_logic;

signal io_etrg_out : std_logic;

signal o_etrg_outd : std_logic;

signal i_ana_trg : std_logic_vector(3 downto 0);

signal io_eclk_out : std_logic;

signal io_eclk_in : std_logic;

-- Debugging signals

-- -----------------

signal o_racc_debug : std_logic;

signal o_debug1 : std_logic;

signal o_debug2 : std_logic;

begin

VCC <= '1';

GND <= '0';

-- map LEDs

P_O_LED0 <= o_led_yellow;

P_O_LED1 <= o_led_red;

-- debug outputs

P_IO_J45 <= GND;

P_IO_J46 <= GND;

P_IO_J48 <= o_debug1;

P_IO_J49 <= o_debug2;

-- triggers

i_ana_trg(0) <= P_I_ATRG1;

i_ana_trg(1) <= P_I_ATRG2;

i_ana_trg(2) <= P_I_ATRG3;

i_ana_trg(3) <= P_I_ATRG4;

io_etrg_in <= P_IO_ETRG_IN;

P_O_ETRG_IND <= o_etrg_ind;

P_IO_ETRG_OUT <= io_etrg_out;

P_O_ETRG_OUTD <= o_etrg_outd;

-- external clock

P_IO_ECLK_OUT <= io_eclk_out;

P_O_ECLK_OUTD <= '1';

io_eclk_in <= P_IO_ECLK_IN;

P_O_ECLK_IND <= '0';

clocks : usr_clocks port map (

P_I_CLK33 => P_I_CLK33,

P_I_CLK66 => P_I_CLK66,

O_CLK33 => clk33,

O_CLK33_NODLL => clk33_nodll,

O_CLK66 => clk66,

O_CLK132 => clk132,

... 121 more lines ...

|

|

189

|

Thu Nov 1 20:25:53 2012 |

hongwei yang | DRS4 firmware |

| hongwei yang wrote: |

|

| Stefan Ritt wrote: |

|

| hongwei yang wrote: |

|

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point?

thanks

Hongwei

|

The "and" in the trigger section means now "coincidence". So the V4 board can trigger on a coincidence between two or more channels. If there is no pulse at the same time on the coincidence channels, the board will of course not trigger. The according firmware was introduced in V4, so please look at drs4_eval4_app.vhd (not eval3).

I just realized that the V4 firmware might be missing in the distribution, so I have attached it here. Look for drs_ctl_trigger_config.

Best regards,

Stefan

|

Ah, great, that helps, Thank you!

Hongwei

|

By the way, will there be a drs4_eval4.vhd as well? |

|

188

|

Thu Nov 1 20:21:44 2012 |

hongwei yang | DRS4 firmware |

| Stefan Ritt wrote: |

|

| hongwei yang wrote: |

|

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point?

thanks

Hongwei

|

The "and" in the trigger section means now "coincidence". So the V4 board can trigger on a coincidence between two or more channels. If there is no pulse at the same time on the coincidence channels, the board will of course not trigger. The according firmware was introduced in V4, so please look at drs4_eval4_app.vhd (not eval3).

I just realized that the V4 firmware might be missing in the distribution, so I have attached it here. Look for drs_ctl_trigger_config.

Best regards,

Stefan

|

Ah, great, that helps, Thank you!

Hongwei |

|

187

|

Thu Nov 1 20:17:42 2012 |

Stefan Ritt | DRS4 firmware |

| hongwei yang wrote: |

|

Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point?

thanks

Hongwei

|

The "and" in the trigger section means now "coincidence". So the V4 board can trigger on a coincidence between two or more channels. If there is no pulse at the same time on the coincidence channels, the board will of course not trigger. The according firmware was introduced in V4, so please look at drs4_eval4_app.vhd (not eval3).

I just realized that the V4 firmware might be missing in the distribution, so I have attached it here. Look for drs_ctl_trigger_config.

Best regards,

Stefan |

| Attachment 1: drs4_eval4_app.vhd

|

--*************************************************************

-- Author : Boris Keil, Stefan Ritt

-- Contents : Main file for DRS4 control and readout

-- $Id: drs4_eval4_app.vhd 15159 2010-04-29 10:12:25Z ritt $

-- $Revision: 15159 $

--*************************************************************

library ieee;

use ieee.std_logic_1164.all;

-- use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

-- synopsys translate_off

library UNISIM;

use UNISIM.Vcomponents.ALL;

-- synopsys translate_on

use work.drs4_pack.all;

entity drs4_eval4_app is

port (

-- clocks

I_CLK33 : in std_logic;

I_CLK66 : in std_logic;

I_CLK132 : in std_logic;

I_CLK264 : in std_logic;

O_CLK_PS_VALUE : out std_logic_vector(7 downto 0);

I_CLK_PS : in std_logic;

I_RESET : in std_logic; -- active high power-up reset

-- analog triggers

I_ANA_TRG : in std_logic_vector(3 downto 0);

-- external trigger

IO_ETRG_IN : inout std_logic;

O_ETRG_IND : out std_logic;

IO_ETRG_OUT : inout std_logic;

O_ETRG_OUTD : out std_logic;

-- external (MMCX clock) clock

IO_ECLK_OUT : inout std_logic;

IO_ECLK_IN : inout std_logic;

-- PMC

P_IO_PMC_USR : inout std_logic_vector(63 downto 0);

-- Simple bus interface to DPRAM

O_DPRAM_CLK : out std_logic;

O_DPRAM_ADDR : out std_logic_vector(31 downto 0);

O_DPRAM_D_WR : out std_logic_vector(31 downto 0);

O_DPRAM_WE : out std_logic;

I_DPRAM_D_RD : in std_logic_vector(31 downto 0);

-- Control & status registers from system FPGA interface

I_CONTROL_REG_ARR : in type_control_reg_arr;

O_STATUS_REG_ARR : out type_status_reg_arr;

I_CONTROL_TRIG_ARR : in type_control_trig_arr;

I_CONTROL0_BIT_TRIG_ARR : in std_logic_vector(31 downto 0);

-- LEDs signals

O_LED_RED : out std_logic;

O_LED_YELLOW : out std_logic;

-- Debug signals

O_DEBUG1 : out std_logic;

O_DEBUG2 : out std_logic

);

end drs4_eval4_app;

--*************************************************************

architecture arch of drs4_eval4_app is

attribute BOX_TYPE : string;

component USR_LIB_VEC_FDC

generic (

width : integer := 1

);

port (

I_CLK : in std_logic_vector (width-1 downto 0);

I_CLR : in std_logic_vector (width-1 downto 0);

I : in std_logic_vector (width-1 downto 0);

O : out std_logic_vector (width-1 downto 0)

);

end component;

component USR_LIB_VEC_IOFD_CPE_NALL

generic (

width : integer := 1;

init_val_to_pad : string := "0";

init_val_from_pad : string := "0"

);

port (

O_C : in std_logic_vector (width-1 downto 0);

O_CE : in std_logic_vector (width-1 downto 0);

O_CLR : in std_logic_vector (width-1 downto 0);

O_PRE : in std_logic_vector (width-1 downto 0);

O : out std_logic_vector (width-1 downto 0);

I_C : in std_logic_vector (width-1 downto 0);

I_CE : in std_logic_vector (width-1 downto 0);

I_CLR : in std_logic_vector (width-1 downto 0);

I_PRE : in std_logic_vector (width-1 downto 0);

I : in std_logic_vector (width-1 downto 0);

IO : inout std_logic_vector (width-1 downto 0);

T : in std_logic_vector (width-1 downto 0)

);

end component;

component OFDDRTCPE

port (

O : out STD_ULOGIC;

C0 : in STD_ULOGIC;

C1 : in STD_ULOGIC;

CE : in STD_ULOGIC;

CLR : in STD_ULOGIC;

D0 : in STD_ULOGIC;

D1 : in STD_ULOGIC;

PRE : in STD_ULOGIC;

T : in STD_ULOGIC

);

end component;

attribute BOX_TYPE of OFDDRTCPE : component is "PRIMITIVE";

component IOBUFDS

port (

O : out STD_ULOGIC;

IO : inout STD_ULOGIC;

IOB : inout STD_ULOGIC;

I : in STD_ULOGIC;

T : in STD_ULOGIC

);

end component;

component LUT1

generic (

INIT : bit_vector

);

port(

O : out STD_ULOGIC;

I0 : in STD_ULOGIC

);

end component;

signal GND : std_logic;

signal VCC : std_logic;

-- ADC

signal i_drs_adc : std_logic_vector(13 downto 0);

signal o_drs_adc_clk : std_logic;

signal adc_clk_sr : std_logic_vector(15 downto 0);

-- Serial interface for DAC, EEPROM and Temp. Sensor

signal o_drs_serial_data : std_logic;

signal o_drs_serial_clk : std_logic;

signal i_drs_serial_data : std_logic;

signal i_drs_eeprom_data : std_logic;

signal o_drs_dac_cs_n : std_logic;

signal o_drs_eeprom_cs_n : std_logic;

signal o_drs_tempsens_cs_n : std_logic;

-- Status LED

signal drs_led_yellow : std_logic;

signal drs_led_trigger : std_logic;

signal drs_led_counter : std_logic_vector(20 downto 0);

type type_drs_led_state is (led_idle, led_on, led_off);

signal drs_led_state : type_drs_led_state;

-- DRS Start/enable

signal o_drs_enable : std_logic;

signal o_drs_write : std_logic;

-- Internal DRS shift registers

signal o_drs_srin : std_logic;

signal o_drs_srclk : std_logic;

signal o_drs_rsrload : std_logic;

signal i_drs_srout : std_logic;

signal i_drs_wsrout : std_logic;

subtype type_sr_count is integer range 0 to 1024;

signal drs_sr_count : type_sr_count;

signal drs_sr_reg : std_logic_vector(7 downto 0);

-- DRS address

signal o_drs_addr : std_logic_vector(3 downto 0);

-- PLL refence clock signal

signal drs_refclk : std_logic;

signal o_drs_refclk : std_logic;

signal drs_refclk_counter : std_logic_vector(16 downto 0);

signal i_drs_plllck : std_logic;

signal i_drs_dtap : std_logic;

-- 132/264 MHz calibration signal output

signal o_drs_tcalib_sig : std_logic;

-- internal amplitude calibration via input multiplexers

signal o_drs_aswitches : std_logic;

-- power signal for chip test board

signal o_drs_on : std_logic;

-- Control registers

signal drs_ctl_start_trig : std_logic;

signal drs_ctl_reinit_trig : std_logic; -- 1 sets drs_reinit_reqest to '1'

signal drs_ctl_soft_trig : std_logic;

signal drs_ctl_eeprom_write_trig: std_logic;

signal drs_ctl_eeprom_read_trig: std_logic;

signal drs_ctl_autostart : std_logic;

signal drs_ctl_dmode : std_logic;

signal drs_ctl_dactive : std_logic;

signal drs_ctl_adc_active : std_logic;

signal drs_ctl_acalib : std_logic;

signal drs_ctl_led_red : std_logic;

signal drs_ctl_tcal_en : std_logic;

signal drs_ctl_tcal_source : std_logic;

signal drs_ctl_refclk_source : std_logic;

type type_drs_dac_val_arr is array (7 downto 0) of std_logic_vector(15 downto 0);

signal drs_ctl_dac_arr : type_drs_dac_val_arr;

signal drs_ctl_first_chn : std_logic_vector(3 downto 0);

signal drs_ctl_last_chn : std_logic_vector(3 downto 0);

signal drs_ctl_config : std_logic_vector(7 downto 0);

signal drs_ctl_chn_config : std_logic_vector(7 downto 0);

signal drs_ctl_sampling_freq : std_logic_vector(15 downto 0);

signal drs_ctl_transp_mode : std_logic;

signal drs_ctl_standby_mode : std_logic;

signal drs_ctl_enable_trigger : std_logic;

signal drs_ctl_trigger_config : std_logic_vector(15 downto 0);

signal drs_ctl_neg_trigger : std_logic;

signal drs_ctl_readout_mode : std_logic;

signal drs_ctl_delay_sel : std_logic_vector(7 downto 0);

-- Status registers

signal drs_stat_busy : std_logic;

signal drs_eeprom_busy : std_logic;

signal drs_stat_stop_cell : std_logic_vector(9 downto 0);

signal drs_stat_stop_wsr : std_logic_vector(7 downto 0);

signal drs_temperature : std_logic_vector(15 downto 0);

signal drs_trigger_bus : std_logic_vector(15 downto 0);

signal drs_serial_number : std_logic_vector(15 downto 0);

signal svn_revision : std_logic_vector(15 downto 0);

-- Misc. internal signals

signal drs_reinit_request : std_logic;

signal drs_old_readout_mode : std_logic;

-- Trigger signals

signal drs_trigger : std_logic;

signal drs_soft_trig : std_logic;

signal drs_trigger_syn : std_logic;

signal drs_write_set : std_logic;

signal drs_trig_ff : std_logic;

signal drs_write_ff : std_logic;

signal drs_hard_inp : std_logic_vector(4 downto 0);

signal drs_hard_or : std_logic;

signal drs_hard_and : std_logic;

signal drs_hard_trig : std_logic;

signal drs_arm_trig : std_logic;

signal drs_trg_delay : std_logic_vector(2047 downto 0);

-- Tell P&R to not optimize away the drs_trg_delay array

attribute keep : string;

attribute keep of drs_trg_delay : signal is "true";

-- Serial bus internal signals

type type_serial_bus_state is (idle, wait_serdes, eeprom_read, eeprom_write, done);

signal serial_bus_state : type_serial_bus_state;

subtype type_serial_count is integer range 0 to 200;

signal serial_count : type_serial_count;

signal serial_ret_addr : type_serial_count;

signal serial_start_flag1 : std_logic;

signal serial_start_flag2 : std_logic;

type type_serdes_state is (idle, busy, busy_temp);

signal serdes_state : type_serdes_state;

subtype type_serdes_clk is integer range 0 to 10;

signal serdes_clk : type_serdes_clk;

signal serdes_speed : type_serdes_clk;

subtype type_serdes_count is integer range 0 to 100;

signal serdes_count : type_serdes_count;

subtype type_serdes_bit_count_m1 is integer range 0 to 32;

signal serdes_bit_count_m1 : type_serdes_bit_count_m1;

signal serdes_bit_no : type_serdes_bit_count_m1;

signal serdes_trig : std_logic;

signal serdes_trig_temp : std_logic;

signal serdes_wdata : std_logic_vector(31 downto 0);

signal serdes_rdata : std_logic_vector(31 downto 0);

type type_drs_dac_reg is array (7 downto 0) of std_logic_vector(15 downto 0);

signal drs_dac_reg : type_drs_dac_reg;

signal drs_dac_newval_flag : std_logic_vector(7 downto 0);

subtype type_dac_bit_count is integer range 0 to 31;

signal temp : std_logic_vector(15 downto 0);

signal temp_timer : std_logic_vector(25 downto 0); -- once per second

signal temp_cmd : std_logic_vector(7 downto 0);

subtype type_eeprom_count is integer range 0 to 100;

signal drs_eeprom_write_trig : std_logic;

signal drs_eeprom_read_trig : std_logic;

signal drs_eeprom_sector : std_logic_vector(15 downto 0);

signal drs_eeprom_page : std_logic_vector(7 downto 0);

signal drs_eeprom_byte : std_logic_vector(7 downto 0);

signal drs_eeprom_cmd : std_logic_vector(59 downto 0);

-- PMC IO pin control signals

signal pmc_clk_i : std_logic_vector(P_IO_PMC_USR'range); -- input FF clock

signal pmc_ce_i : std_logic_vector(P_IO_PMC_USR'range); -- input FF clock enable

signal pmc_clr_i : std_logic_vector(P_IO_PMC_USR'range); -- input FF async clear

... 1459 more lines ...

|

|

186

|

Thu Nov 1 20:08:33 2012 |

hongwei yang | DRS4 firmware | Hi,

We are using drs4 board, but oscilloscope app will somehow stop to work if we config trigger into "or and", When I look into the drs4 firmware file drs4_eval3_app.vhd, I couldn't find the trigger_config value assignment which is mentioned at(#7 offset 0x1E from 31 downto 16) in manual_version 4.

could you help me find this trigger_config access point? Or is there any drs4_eval4_app.vhd missing in the source files?

thanks

Hongwei |

|

185

|

Mon Oct 29 18:30:28 2012 |

Martin Petriska | GetWave | I have some question according to GetWave function. In drs_exam.cpp simple GetWave(0,0,wave_array[]) etc...is used. Is there primary (cell) calibration, secondary calibration (Readout) and remove Spikes used, as in DRS Oscilloscope application? |

|

184

|

Fri Oct 12 14:09:37 2012 |

Stefan Ritt | DRS abbreviation |

| Moritz von Witzleben wrote: |

|

Hello,

what is the abbreviation of DRS?

Thanks and kind Regards,

Moritz

|

Domino Ring Sampler. |

|

183

|

Fri Oct 12 14:06:04 2012 |

Moritz von Witzleben | DRS abbreviation | Hello,

what is the abbreviation of DRS?

Thanks and kind Regards,

Moritz |

|

182

|

Thu Oct 4 21:07:27 2012 |

Zach Miller | DRS5 |

| Stefan Ritt wrote: |

|

| Zach Miller wrote: |

|

Hi,

Our group had previously heard that a "DRS-5.0" might be on the horizon and that it may have ethernet capabilities as well as 16-input channels (we heard this when ordering the DRS-4). Is this still in the works and accurate information? If so, is there a rough estimate to the "release date?"

Thanks for your time,

Zach Miller

|

You mix up two things: The DRS5 chip is a new device with improved samling speed (10 GSPS) and lower dead time. This chip might come in 2-3 years. The 16-input board you mentioned is a DAQ board based on the DRS4 chip. This board well be operational beginning of 2013 as a prototype. It is not clear however at this point in which way this board will be made available for public. Maybe we will license this to industry. The design is however pretty much defined: 16 channels with gain 0.1-100, 1 GHz Bandwidth, Gigabit Ethernet output, and multi-board capabilities. Trigger on each channel with logical combinations. 80 MSPS continuous sampling (in addition to the DRS4 sampling). Each channel can be biased 0-210 V for SiPMT or APD power. A 19" 3 HE crate will host 16 boards with 256 channels.

/Stefan

|

Thanks, Stefan. That was the information we were looking for.

Cheers.

-Zach |

|

181

|

Thu Oct 4 20:59:18 2012 |

Stefan Ritt | DRS5 |

| Zach Miller wrote: |

|

Hi,

Our group had previously heard that a "DRS-5.0" might be on the horizon and that it may have ethernet capabilities as well as 16-input channels (we heard this when ordering the DRS-4). Is this still in the works and accurate information? If so, is there a rough estimate to the "release date?"

Thanks for your time,

Zach Miller

|

You mix up two things: The DRS5 chip is a new device with improved samling speed (10 GSPS) and lower dead time. This chip might come in 2-3 years. The 16-input board you mentioned is a DAQ board based on the DRS4 chip. This board well be operational beginning of 2013 as a prototype. It is not clear however at this point in which way this board will be made available for public. Maybe we will license this to industry. The design is however pretty much defined: 16 channels with gain 0.1-100, 1 GHz Bandwidth, Gigabit Ethernet output, and multi-board capabilities. Trigger on each channel with logical combinations. 80 MSPS continuous sampling (in addition to the DRS4 sampling). Each channel can be biased 0-210 V for SiPMT or APD power. A 19" 3 HE crate will host 16 boards with 256 channels.

/Stefan |

|

180

|

Thu Oct 4 20:50:36 2012 |

Zach Miller | DRS5 | Hi,

Our group had previously heard that a "DRS-5.0" might be on the horizon and that it may have ethernet capabilities as well as 16-input channels (we heard this when ordering the DRS-4). Is this still in the works and accurate information? If so, is there a rough estimate to the "release date?"

Thanks for your time,

Zach Miller |

|