| ID |

Date |

Author |

Subject |

|

436

|

Thu Jul 2 13:20:51 2015 |

Felix Bachmair | Creation of Object files | HI,

We are using the DRS4 Board in the EUDAQ framework [1]. We wrote a a Producer based on the software of the evaluation board, which is using the DRS class/header/src files.

In order to make it work we needed to compile it with a shared object file. [2]

Would it be possbile to include a shared object in the 'official' release?

Cheers

Felix

[1]https://telescopes.desy.de/EUDAQ

[2]https://github.com/veloxid/DRS4-v5-shared |

|

437

|

Fri Jul 3 17:13:27 2015 |

Stefan Ritt | Creation of Object files | Hi Felix,

the distribution does not contain any binaries, since there are too many Linux distributions around, so everybody compiles from the sources under Linux. Do you want me to just add libDRS.so to the official Makefile? Actually you are the first one asking for this. Would it be beneficial to have this in the distribution, or can you just maintain your own Makefile in the github repository?

Stefan

| Felix Bachmair wrote: |

|

HI,

We are using the DRS4 Board in the EUDAQ framework [1]. We wrote a a Producer based on the software of the evaluation board, which is using the DRS class/header/src files.

In order to make it work we needed to compile it with a shared object file. [2]

Would it be possbile to include a shared object in the 'official' release?

Cheers

Felix

[1]https://telescopes.desy.de/EUDAQ

[2]https://github.com/veloxid/DRS4-v5-shared

|

|

|

438

|

Mon Jul 6 11:30:56 2015 |

Felix Bachmair | Creation of Object files | Hi Stefan,

That's fine for me. I thought it might be interesting for others as well..

Cheers

Felix

| Stefan Ritt wrote: |

|

Hi Felix,

the distribution does not contain any binaries, since there are too many Linux distributions around, so everybody compiles from the sources under Linux. Do you want me to just add libDRS.so to the official Makefile? Actually you are the first one asking for this. Would it be beneficial to have this in the distribution, or can you just maintain your own Makefile in the github repository?

Stefan

| Felix Bachmair wrote: |

|

HI,

We are using the DRS4 Board in the EUDAQ framework [1]. We wrote a a Producer based on the software of the evaluation board, which is using the DRS class/header/src files.

In order to make it work we needed to compile it with a shared object file. [2]

Would it be possbile to include a shared object in the 'official' release?

Cheers

Felix

[1]https://telescopes.desy.de/EUDAQ

[2]https://github.com/veloxid/DRS4-v5-shared

|

|

|

|

439

|

Mon Jul 6 19:25:27 2015 |

Stefan Ritt | Creation of Object files | Anyhow it would be nice if you just post your Makefile here, which runs with the standard distribution, so people can use it if needed.

Stefan

| Felix Bachmair wrote: |

|

Hi Stefan,

That's fine for me. I thought it might be interesting for others as well..

Cheers

Felix

| Stefan Ritt wrote: |

|

Hi Felix,

the distribution does not contain any binaries, since there are too many Linux distributions around, so everybody compiles from the sources under Linux. Do you want me to just add libDRS.so to the official Makefile? Actually you are the first one asking for this. Would it be beneficial to have this in the distribution, or can you just maintain your own Makefile in the github repository?

Stefan

| Felix Bachmair wrote: |

|

HI,

We are using the DRS4 Board in the EUDAQ framework [1]. We wrote a a Producer based on the software of the evaluation board, which is using the DRS class/header/src files.

In order to make it work we needed to compile it with a shared object file. [2]

Would it be possbile to include a shared object in the 'official' release?

Cheers

Felix

[1]https://telescopes.desy.de/EUDAQ

[2]https://github.com/veloxid/DRS4-v5-shared

|

|

|

|

|

440

|

Tue Jul 7 09:29:21 2015 |

Felix Bachmair | Creation of Object files | Yes of course no problem.

You can download via github https://github.com/veloxid/DRS4-v5-shared and I also put it in the attachment.

It's tested with Ubuntu, Fedora and RHEL.

For mac OSX one needs to create a dylib out of the so file.

Cheers

Felix

| Stefan Ritt wrote: |

|

Anyhow it would be nice if you just post your Makefile here, which runs with the standard distribution, so people can use it if needed.

Stefan

| Felix Bachmair wrote: |

|

Hi Stefan,

That's fine for me. I thought it might be interesting for others as well..

Cheers

Felix

| Stefan Ritt wrote: |

|

Hi Felix,

the distribution does not contain any binaries, since there are too many Linux distributions around, so everybody compiles from the sources under Linux. Do you want me to just add libDRS.so to the official Makefile? Actually you are the first one asking for this. Would it be beneficial to have this in the distribution, or can you just maintain your own Makefile in the github repository?

Stefan

| Felix Bachmair wrote: |

|

HI,

We are using the DRS4 Board in the EUDAQ framework [1]. We wrote a a Producer based on the software of the evaluation board, which is using the DRS class/header/src files.

In order to make it work we needed to compile it with a shared object file. [2]

Would it be possbile to include a shared object in the 'official' release?

Cheers

Felix

[1]https://telescopes.desy.de/EUDAQ

[2]https://github.com/veloxid/DRS4-v5-shared

|

|

|

|

|

| Attachment 1: Makefile

|

########################################################

#

# Makefile for drsosc, drscl and drs_exam

# executables under linux

#

# Requires wxWidgets 2.8.9 or newer

#

########################################################

# check if wxWidgets is installed

HAVE_WX = $(shell which wx-config)

ifeq ($(HAVE_WX),)

$(error Error: wxWidgets required to compile "drsosc")

endif

# check for OS

OS = $(shell uname)

ifeq ($(OS),Darwin)

DOS = OS_DARWIN

else

DOS = OS_LINUX

endif

CFLAGS = -g -O2 -Wall -Wuninitialized -fno-strict-aliasing -Iinclude -I/usr/local/include -D$(DOS) -DHAVE_USB -DHAVE_LIBUSB10 -DUSE_DRS_MUTEX

LIBS = -lpthread -lutil -lusb-1.0

ifeq ($(OS),Darwin)

CFLAGS += -stdlib=libstdc++

endif

# wxWidgets libs and flags

WXLIBS = $(shell wx-config --libs)

WXFLAGS = $(shell wx-config --cxxflags)

CPP_OBJ = DRS.o averager.o ConfigDialog.o DOFrame.o DOScreen.o DRSOsc.o MeasureDialog.o Measurement.o Osci.o InfoDialog.o DisplayDialog.o AboutDialog.o EPThread.o TriggerDialog.o rb.o

OBJECTS = musbstd.o mxml.o strlcpy.o

SHARED_OBJECTS= libDRS.so

ifeq ($(OS),Darwin)

all: drsosc drscl drs_exam drs_exam_multi DRSOsc.app

else

all: drsosc drscl drs_exam drs_exam_multi

endif

DRSOsc.app: drsosc

-mkdir DRSOsc.app

-mkdir DRSOsc.app/Contents

-mkdir DRSOsc.app/Contents/MacOS

-mkdir DRSOsc.app/Contents/Resources

-mkdir DRSOsc.app/Contents/Resources/English.lproj

echo 'APPL????' > DRSOsc.app/Contents/PkgInfo

cp Info.plist DRSOsc.app/Contents/Info.plist

cp DRSOsc.icns DRSOsc.app/Contents/Resources

cp drsosc DRSOsc.app/Contents/MacOS/DRSOsc

drsosc: $(OBJECTS) $(CPP_OBJ) main.o

$(CXX) $(CFLAGS) $(OBJECTS) $(CPP_OBJ) main.o -o drsosc $(LIBS) $(WXLIBS)

drscl: $(OBJECTS) DRS.o averager.o drscl.o

$(CXX) $(CFLAGS) $(OBJECTS) DRS.o averager.o drscl.o -o drscl $(LIBS) $(WXLIBS)

drs_exam: $(OBJECTS) drs_exam.o $(SHARED_OBJECTS)

# $(CXX) $(CFLAGS) -L . $(OBJECTS) -lDRS drs_exam.o -o drs_exam $(LIBS) $(WXLIBS)

$(CXX) $(CFLAGS) $(OBJECTS) -L. drs_exam.o -lDRS -o drs_exam $(LIBS) $(WXLIBS)

drs_exam_multi: $(OBJECTS) DRS.o averager.o drs_exam_multi.o

#old $(CXX) $(CFLAGS) $(OBJECTS) DRS.o averager.o drs_exam_multi.o -o drs_exam_multi $(LIBS) $(WXLIBS)

$(CXX) $(CFLAGS) $(OBJECTS) -L. DRS.o averager.o drs_exam_multi.o -o drs_exam_multi -lDRS $(LIBS) $(WXLIBS)

main.o: src/main.cpp include/mxml.h include/DRS.h

$(CXX) $(CFLAGS) $(WXFLAGS) -c $<

drscl.o: src/drscl.cpp include/mxml.h include/DRS.h

$(CXX) $(CFLAGS) -c $<

drs_exam.o: src/drs_exam.cpp include/mxml.h include/DRS.h

$(CXX) $(CFLAGS) -c $<

drs_exam_multi.o: src/drs_exam_multi.cpp include/mxml.h include/DRS.h

$(CXX) $(CFLAGS) -c $<

$(CPP_OBJ): %.o: src/%.cpp include/%.h include/mxml.h include/DRS.h

$(CXX) $(CFLAGS) $(WXFLAGS) -c $<

$(OBJECTS): %.o: src/%.c include/mxml.h include/DRS.h

$(CC) $(CFLAGS) -c $<

$(SHARED_OBJECTS): %.so: DRS.o mxml.o averager.o musbstd.o

# Make Shared objectss

# g++ -Wall -shared -fPIC -o libDRS.so src/DRS.cpp src/averager.cpp src/mxml.c -I include/

# < $<

# @ $@

# %.so

#g++ -Wall -shared -fPIC -o libDRS.so src/DRS.cpp src/averager.cpp src/mxml.c -I include/")

$(CXX) $(CFLAGS) $(WXFLAGS) -Wall -shared -fPIC -o $@ -I include/ src/DRS.cpp src/averager.cpp src/mxml.c src/musbstd.c $(LIBS) $(WXLIBS)

clean:

rm -f *.o *.so drscl drsosc

|

|

4

|

Wed Feb 11 12:21:07 2009 |

Stefan Ritt | Corrected datasheet Rev. 0.8 | Please note the new datasheet Rev. 0.8 available from the DRS web site. It fixes the label of pin #76, which was AGND but is actualy AVDD. The input IN8+ is located at pin #20 and not at pin #19 as described in the old table 2. |

|

781

|

Wed Oct 23 17:56:26 2019 |

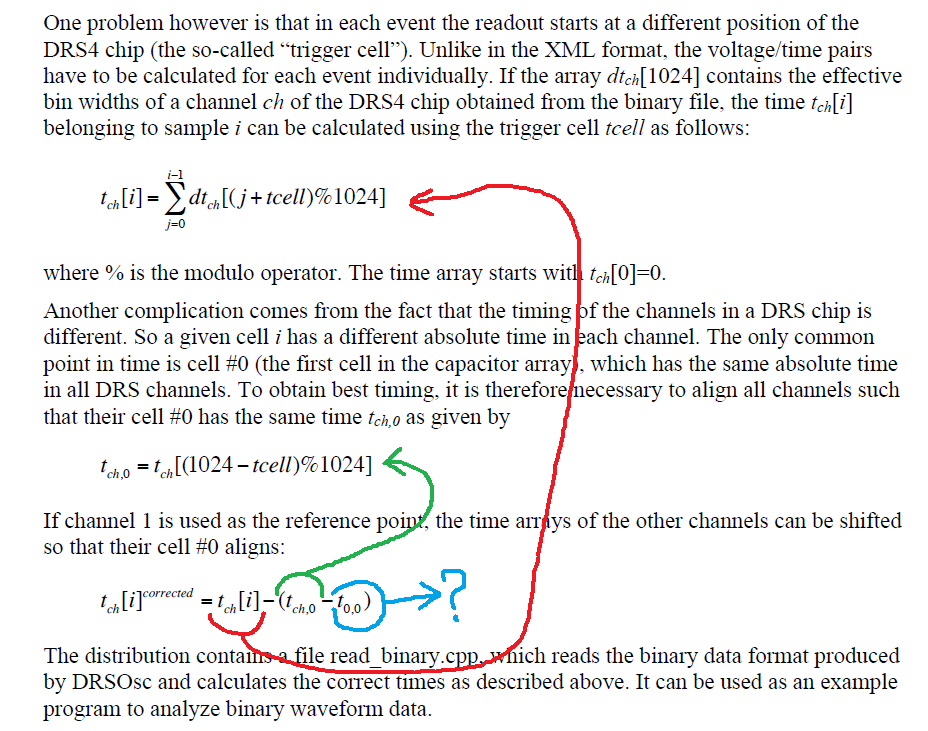

John Jendzurski | Computing corrected time from binary data...what is t_0,0? | In the equations for computing the corrected time for channels other than channel 1, does anyone know what the term t0,0 refers to? This is the last term in the last equation on page 24 of DRS4 Evaluation Board User’s Manual, Board Revision 5 as of January 2014, Last revised: April 27, 2016.

Screenshot from User's Manual is attached below.

Thank you! |

| Attachment 1: Screenshot.png

|

|

|

782

|

Fri Oct 25 16:39:07 2019 |

Stefan Ritt | Computing corrected time from binary data...what is t_0,0? | t0,0 refers to the time of cell #0 of channel #0. So basically you keep channel 0 fixed, calculate the difference of each channel's cell #0 in respect to channel 0, and align all channels except channel 0 so that their cell #0 has the same value. There is an inconsistency between the channel numbering. The formula uses 0...3 and the manual says "channel 1" but it means actually the first channel, which uses index "0".

Stefan

| John Jendzurski wrote: |

|

In the equations for computing the corrected time for channels other than channel 1, does anyone know what the term t0,0 refers to? This is the last term in the last equation on page 24 of DRS4 Evaluation Board User’s Manual, Board Revision 5 as of January 2014, Last revised: April 27, 2016.

Screenshot from User's Manual is attached below.

Thank you!

|

|

|

471

|

Tue Jan 12 17:57:03 2016 |

Jack Bargemann | Compiling DRS-exam | I am trying to compile drs-exam, but am getting an error message I do not understand:

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_open referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_close referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_descriptor referenced in function _musb_get_device

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_write referenced in function _musb_write

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_read referenced in function _musb_read

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_configuration referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_claim_interface referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_release_interface referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_altinterface referenced in function _musb_set_altinterface

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_reset referenced in function _musb_reset

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_init referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_debug referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_busses referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_devices referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_busses referenced in function _musb_open

I have tried redownloading a different version of libusb-1.0, but the problem was not solved. What might I be doing wrong? |

|

472

|

Tue Jan 12 21:02:31 2016 |

Stefan Ritt | Compiling DRS-exam | I guess you are compiling under MS Windows ??? You probably don't link correctly to the USB lib. Try to compile the examples coming with libusb-1.0 to make you everything is right there.

| Jack Bargemann wrote: |

|

I am trying to compile drs-exam, but am getting an error message I do not understand:

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_open referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_close referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_descriptor referenced in function _musb_get_device

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_write referenced in function _musb_write

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_bulk_read referenced in function _musb_read

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_configuration referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_claim_interface referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_release_interface referenced in function _musb_close

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_altinterface referenced in function _musb_set_altinterface

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_reset referenced in function _musb_reset

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_init referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_set_debug referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_busses referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_find_devices referenced in function _musb_open

1>musbstd.obj : error LNK2019: unresolved external symbol _usb_get_busses referenced in function _musb_open

I have tried redownloading a different version of libusb-1.0, but the problem was not solved. What might I be doing wrong?

|

|

|

386

|

Wed Oct 15 10:14:32 2014 |

Simon Weingarten | Clock settings in daisy chain DAQ | Hi,

I'm currently working on a little DAQ system with four DRS evaluation boards. Do i need to apply any specific settings when using the clock in/out connectors for synchronization? I do not see anything like that in the drs_exam_multi example.

Any help would be greatly appreciated!

Best,

Simon |

|

387

|

Wed Oct 15 10:52:58 2014 |

Stefan Ritt | Clock settings in daisy chain DAQ |

| Simon Weingarten wrote: |

|

Hi,

I'm currently working on a little DAQ system with four DRS evaluation boards. Do i need to apply any specific settings when using the clock in/out connectors for synchronization? I do not see anything like that in the drs_exam_multi example.

Any help would be greatly appreciated!

Best,

Simon

|

Right, I did not yet put any code there. What you need on all slave boards is

b->SetRefclk(true);

b->SetFrequency(...);

Set SetFrequency() is needed to restart the boards with the external clock.

This works of course only if you have the clock signals connected as written in the manual. If not, the boards won't work after you switch the reference clock.

Best regards,

Stefan |

|

388

|

Wed Oct 15 11:34:43 2014 |

Simon Weingarten | Clock settings in daisy chain DAQ |

| Stefan Ritt wrote: |

|

| Simon Weingarten wrote: |

|

Hi,

I'm currently working on a little DAQ system with four DRS evaluation boards. Do i need to apply any specific settings when using the clock in/out connectors for synchronization? I do not see anything like that in the drs_exam_multi example.

Any help would be greatly appreciated!

Best,

Simon

|

Right, I did not yet put any code there. What you need on all slave boards is

b->SetRefclk(true);

b->SetFrequency(...);

Set SetFrequency() is needed to restart the boards with the external clock.

This works of course only if you have the clock signals connected as written in the manual. If not, the boards won't work after you switch the reference clock.

Best regards,

Stefan

|

Thank you so much for the fast reply! I'll give it a try.

Best regards,

Simon |

|

389

|

Wed Oct 15 12:15:58 2014 |

Stefan Ritt | Clock settings in daisy chain DAQ | Here is the full version of the program with clock daisy-chaining. Before switching to the external clock, it checks if the clock really is there (by reading an internal scaler), and only then enables it. Note that the code also works without clock daisy-chaining. But without clock daisy-chaining your have some 400 ps time resolution between boards, and with clock daisy-chaining you get some 60 ps. |

| Attachment 1: drs_exam_multi.cpp

|

/********************************************************************\

Name: drs_exam_multi.cpp

Created by: Stefan Ritt

Contents: Simple example application to read out a several

DRS4 evaluation board in daisy-chain mode

$Id: drs_exam_multi.cpp 21509 2014-10-15 10:11:36Z ritt $

\********************************************************************/

#include <math.h>

#ifdef _MSC_VER

#include <windows.h>

#elif defined(OS_LINUX)

#define O_BINARY 0

#include <unistd.h>

#include <ctype.h>

#include <sys/ioctl.h>

#include <errno.h>

#define DIR_SEPARATOR '/'

#endif

#include <stdio.h>

#include <string.h>

#include <stdlib.h>

#include "strlcpy.h"

#include "DRS.h"

/*------------------------------------------------------------------*/

int main()

{

int i, j, k;

DRS *drs;

DRSBoard *b, *mb;

float time_array[8][1024];

float wave_array[8][1024];

FILE *f;

/* do initial scan, sort boards accordning to their serial numbers */

drs = new DRS();

drs->SortBoards();

/* show any found board(s) */

for (i=0 ; i<drs->GetNumberOfBoards() ; i++) {

b = drs->GetBoard(i);

printf("Found DRS4 evaluation board, serial #%d, firmware revision %d\n",

b->GetBoardSerialNumber(), b->GetFirmwareVersion());

if (b->GetBoardType() < 8) {

printf("Found pre-V4 board, aborting\n");

return 0;

}

}

/* exit if no board found */

if (drs->GetNumberOfBoards() == 0) {

printf("No DRS4 evaluation board found\n");

return 0;

}

/* exit if only one board found */

if (drs->GetNumberOfBoards() == 1) {

printf("Only one DRS4 evaluation board found, please use drs_exam program\n");

return 0;

}

/* use first board with highest serial number as the master board */

mb = drs->GetBoard(0);

/* common configuration for all boards */

for (i=0 ; i<drs->GetNumberOfBoards() ; i++) {

b = drs->GetBoard(i);

/* initialize board */

b->Init();

/* select external reference clock for slave modules */

/* NOTE: this only works if the clock chain is connected */

if (i > 0) {

if (b->GetFirmwareVersion() >= 21260) { // this only works with recent firmware versions

if (b->GetScaler(5) > 300000) // check if external clock is connected

b->SetRefclk(true); // switch to external reference clock

}

}

/* set sampling frequency */

b->SetFrequency(5, true);

/* set input range to -0.5V ... +0.5V */

b->SetInputRange(0);

/* enable hardware trigger */

b->EnableTrigger(1, 0);

if (i == 0) {

/* master board: enable hardware trigger on CH1 at 50 mV positive edge */

b->SetTranspMode(1);

b->SetTriggerSource(1<<0); // set CH1 as source

b->SetTriggerLevel(0.05); // 50 mV

b->SetTriggerPolarity(false); // positive edge

b->SetTriggerDelayNs(0); // zero ns trigger delay

} else {

/* slave boards: enable hardware trigger on Trigger IN */

b->SetTriggerSource(1<<4); // set Trigger IN as source

b->SetTriggerPolarity(false); // positive edge

}

}

/* open file to save waveforms */

f = fopen("data.txt", "w");

if (f == NULL) {

perror("ERROR: Cannot open file \"data.txt\"");

return 1;

}

/* repeat ten times */

for (i=0 ; i<10 ; i++) {

/* start boards (activate domino wave), master is last */

for (j=drs->GetNumberOfBoards()-1 ; j>=0 ; j--)

drs->GetBoard(j)->StartDomino();

/* wait for trigger on master board */

printf("Waiting for trigger...");

fflush(stdout);

while (mb->IsBusy());

fprintf(f, "Event #%d =====================================================\n", j);

for (j=0 ; j<drs->GetNumberOfBoards() ; j++) {

b = drs->GetBoard(j);

if (b->IsBusy()) {

i--; /* skip that event, must be some fake trigger */

break;

}

/* read all waveforms from all boards */

b->TransferWaves(0, 8);

for (k=0 ; k<4 ; k++) {

/* read time (X) array in ns */

b->GetTime(0, k*2, b->GetTriggerCell(0), time_array[k]);

/* decode waveform (Y) arrays in mV */

b->GetWave(0, k*2, wave_array[k]);

}

/* Save waveform: X=time_array[i], Channel_n=wave_array[n][i] */

fprintf(f, "Board #%d ---------------------------------------------------\n t1[ns] u1[mV] t2[ns] u2[mV] t3[ns] u3[mV] t4[ns] u4[mV]\n", b->GetBoardSerialNumber());

for (k=0 ; k<1024 ; k++)

fprintf(f, "%7.3f %7.1f %7.3f %7.1f %7.3f %7.1f %7.3f %7.1f\n",

time_array[0][k], wave_array[0][k],

time_array[1][k], wave_array[1][k],

time_array[2][k], wave_array[2][k],

time_array[3][k], wave_array[3][k]);

}

/* print some progress indication */

printf("\rEvent #%d read successfully\n", i);

}

fclose(f);

printf("Program finished.\n");

/* delete DRS object -> close USB connection */

delete drs;

}

|

|

403

|

Fri Apr 17 10:07:38 2015 |

Simon Weingarten | Clock settings in daisy chain DAQ | Hi Stefan,

do you know how these numbers (400ps and 60ps) scale with the sampling rate? The manual says they are for 5GS/s, do they change with slower sampling?

Thanks and best regards,

Simon

| Stefan Ritt wrote: |

|

Here is the full version of the program with clock daisy-chaining. Before switching to the external clock, it checks if the clock really is there (by reading an internal scaler), and only then enables it. Note that the code also works without clock daisy-chaining. But without clock daisy-chaining your have some 400 ps time resolution between boards, and with clock daisy-chaining you get some 60 ps.

|

|

|

404

|

Mon Apr 20 13:08:24 2015 |

Stefan Ritt | Clock settings in daisy chain DAQ | The resolution coming from the sampling rate goes into these numbers, but just marginally. At 5 GSPS, you get a few ps reolution, while at 1 GSPS, you get like 15 ps. If you convolve 15 ps with 400 ps, you get 400.3 ps, which is not significantly worse than 400 ps.

| Simon Weingarten wrote: |

|

Hi Stefan,

do you know how these numbers (400ps and 60ps) scale with the sampling rate? The manual says they are for 5GS/s, do they change with slower sampling?

Thanks and best regards,

Simon

| Stefan Ritt wrote: |

|

Here is the full version of the program with clock daisy-chaining. Before switching to the external clock, it checks if the clock really is there (by reading an internal scaler), and only then enables it. Note that the code also works without clock daisy-chaining. But without clock daisy-chaining your have some 400 ps time resolution between boards, and with clock daisy-chaining you get some 60 ps.

|

|

|

|

918

|

Thu May 8 23:23:19 2025 |

Jonathan Bradshaw | Clarification of full channel readout | Hi all

We're working on a new product using the DRS4 IC, and want to do a full readout from cell 0 (not just Region of Interest). I have a couple of questions I hope you can help me with:

- We plan to do a full readout sequence, starting at cell 0. Part of that sequence includes pulsing RSRLOAD and reading out the stop position as shown in v0.9 datasheet Figure 15. What should the DRS4 address bits A3..0 be set to for reading out the stop position? (I’m assuming it’s 1011 ‘Address Read Shift Register’)

- What is the output delay from the falling edge of SRCLK to valid data at SROUT?

- For channel readout, we pulse SRCLK to advance the read shift register. The diagram shown in v0.9 datasheet Figure 12 appears to show that the analog output is updated on the rising edge of SRCLK. Is this correct or have I misread the diagram? (Other shift register transfers are clocked on the falling edge

- The DRS4 v0.9 datasheet Figure 7 shows that the Configuration register is clocked on the falling edge of SRCLK. Just below that is the text “The new register content becomes immediately active at the eighth rising edge of the SRCLK signal.” Should that perhaps read ‘… the eighth falling edge of the SRCLK signal’?

|

| Attachment 1: Screenshot_2025-05-09_093332.png

|

|

|

921

|

Fri May 9 08:26:17 2025 |

Stefan Ritt | Clarification of full channel readout | The full readout mode is not really recommended since you have to pull out the stop position separately. Just do the ROI readout using the RSRLOAD signal, and then do 1024 samples, which also gives you the full waveform, but also the stop position in a single readout cyclce. The "full readout mode" is more there for "historical reasons", but nobody really uses it any more.

If you are interested in all details of the control signals, I propose you have a look at the VHDL code which comes with the software distribution. It's contained in the "firmware" subdirectoy and called drs4_eval5_app.vhd

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're working on a new product using the DRS4 IC, and want to do a full readout from cell 0 (not just Region of Interest). I have a couple of questions I hope you can help me with:

- We plan to do a full readout sequence, starting at cell 0. Part of that sequence includes pulsing RSRLOAD and reading out the stop position as shown in v0.9 datasheet Figure 15. What should the DRS4 address bits A3..0 be set to for reading out the stop position? (I’m assuming it’s 1011 ‘Address Read Shift Register’)

- What is the output delay from the falling edge of SRCLK to valid data at SROUT?

- For channel readout, we pulse SRCLK to advance the read shift register. The diagram shown in v0.9 datasheet Figure 12 appears to show that the analog output is updated on the rising edge of SRCLK. Is this correct or have I misread the diagram? (Other shift register transfers are clocked on the falling edge

- The DRS4 v0.9 datasheet Figure 7 shows that the Configuration register is clocked on the falling edge of SRCLK. Just below that is the text “The new register content becomes immediately active at the eighth rising edge of the SRCLK signal.” Should that perhaps read ‘… the eighth falling edge of the SRCLK signal’?

|

|

|

222

|

Wed Feb 27 13:47:32 2013 |

Georg Winner | Chip Test - Cell Error | When starting Chip Test in DRS Command Line Interface, I receive the following message:

Cell error on channel 1, cell 5: -154.4 mV instead 0 mV

Chip Error!

What does this mean? The maximal peak-to-peak Amplitude given to channel was for a short time 10V.

The graphical interface shows no artefacts when using channel 1.

|

|

227

|

Wed Mar 6 13:08:03 2013 |

Stefan Ritt | Chip Test - Cell Error |

| Georg Winner wrote: |

|

When starting Chip Test in DRS Command Line Interface, I receive the following message:

Cell error on channel 1, cell 5: -154.4 mV instead 0 mV

Chip Error!

What does this mean? The maximal peak-to-peak Amplitude given to channel was for a short time 10V.

The graphical interface shows no artefacts when using channel 1.

|

The "Chip Test" command is made for a special test board we use for chip testing. This command will not work with the evaluation board, since only four of the 8 DRS channels are connected there. So just ignore it and verify the board functionality by looking at the graphical interface.

/Stefan |

|