| ID |

Date |

Author |

Subject |

|

937

|

Tue Apr 28 08:15:35 2026 |

Stefan Ritt | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | The DRS4 gets into the "1.8A" state if DSPEED approaches like 0.7V. Then both inverters of the Domino chain are kind of open and a large current flows. In that state, the only way out is a power cycle.

It's however not clear to me how you get there. If DENABLE is low, this should be prevented. Most FPGAs however pull up their pins on power-on, and ony when configured, the pins go low according to the programming. Maybe it's the time during the FPGA boot which is your problem. Some FPGAs can be configured not to do this. I woulld recommend putting VDD analog, VDD digital, DSPEED, DENABLE, FPGA config ready, all on an oscilloscope and watch what happens during power on. The 1.8A state should be prevented by all means since it could damage the chip.

Stefan |

|

936

|

Tue Apr 28 04:40:38 2026 |

QICHAOWU | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Dear Dr. Stefan Ritt,

I am writing to express my sincere gratitude for your continued and prompt responses to our previous inquiries regarding the waveform truncation issue with the DRS4. Your advice and insights have been invaluable throughout this debugging process.

We have now preliminarily identified and resolved the problem. The key observation came when we powered the DRS4 from an independent supply: shortly after power‑up, with both DENABLE and DWRITE pulled low to GND, the VDD rail still drew an abnormally high current (approximately 1.8 A). This indicated that the DRS4 had been unintentionally activated into an abnormal state. While we confirmed with both an oscilloscope and a multimeter that the DENABLE and DWRITE pins remained at a valid low level, we suspected that the chip’s initialization was corrupted, preventing the internal registers from being loaded with their default values.

To address this, we manually reloaded the default register values via the FPGA. After this modification, the waveform truncation phenomenon completely disappeared.

Thus, we conclude that the root cause of the waveform truncation was improper initialization of the DRS4. Going forward, we will continue to improve the hardware conditions to ensure correct initialization of the chip.

Thank you once again, Dr. Ritt, for your active and generous support. We hope that the problem we encountered and the solution we found will be helpful to other DRS4 users and contribute to the healthy development of the DRS4 community.

| Stefan Ritt wrote: |

|

Not much I can say here. I know that the DRS4 works reliably, since we have an experiment here with 500 chips running since 5 years and we did not observer what you described. Therefore, it must be some subtle detail of your FPGA code or the voltage levels on your board. As I said, what I would do is to get the evaluation abord and copare signals 1:1.

Stefan

| QICHAOWU wrote: |

|

Dear Dr.Stefan

Thank you for your detailed response. Following your suggestion, I used an oscilloscope to observe the RSLOAD and SRCLK signals, and they conform to the readout timing described in the datasheet.

I can now confirm that the DRS4 occasionally fails to correctly update the stop position to cell 1023, or the stored waveform from cell 0 to the stop position is corrupted. As a result, part of the waveform comes from the most recent acquisition while the other part comes from an earlier one, causing the truncation I observed. This issue occurs with a certain probability—more than half of the acquisitions still yield complete, continuous waveforms.

Interestingly, when I use the same FPGA code and host software on the DRS4 evaluation board, no truncation occurs at all. I am currently comparing the behavior of the two setups from both hardware and software perspectives. Could you kindly provide some suggestions on further tests I could perform?

Thank you very much for your help.

Best regards,

Qichao Wu

| Stefan Ritt wrote: |

|

Actually looking at your waveforms again, I think I understand maybe your problem. You stop the DRS4 randomly, but your ROI readout mode does not really work. Seems like you always read from the first cell, or just from a wrong cell. Since your sine wave period is not a multiple of the readout window, you see a phase jump between the beginning of your sampling window and the end of your sampling window. The little spikes before and after the jump are normal, since the first and last samples of the DRS4 readout might have some offset. Check that your FPGA really uses RSLOAD to start the readout, and not the "full readout".

The evaluation board might really help you, since you can compare 1:1 all control signals with yours.

Stefan

| QICHAOWU wrote: |

|

Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

|

|

|

|

|

935

|

Fri Apr 17 12:39:11 2026 |

Stefan Ritt | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Not much I can say here. I know that the DRS4 works reliably, since we have an experiment here with 500 chips running since 5 years and we did not observer what you described. Therefore, it must be some subtle detail of your FPGA code or the voltage levels on your board. As I said, what I would do is to get the evaluation abord and copare signals 1:1.

Stefan

| QICHAOWU wrote: |

|

Dear Dr.Stefan

Thank you for your detailed response. Following your suggestion, I used an oscilloscope to observe the RSLOAD and SRCLK signals, and they conform to the readout timing described in the datasheet.

I can now confirm that the DRS4 occasionally fails to correctly update the stop position to cell 1023, or the stored waveform from cell 0 to the stop position is corrupted. As a result, part of the waveform comes from the most recent acquisition while the other part comes from an earlier one, causing the truncation I observed. This issue occurs with a certain probability—more than half of the acquisitions still yield complete, continuous waveforms.

Interestingly, when I use the same FPGA code and host software on the DRS4 evaluation board, no truncation occurs at all. I am currently comparing the behavior of the two setups from both hardware and software perspectives. Could you kindly provide some suggestions on further tests I could perform?

Thank you very much for your help.

Best regards,

Qichao Wu

| Stefan Ritt wrote: |

|

Actually looking at your waveforms again, I think I understand maybe your problem. You stop the DRS4 randomly, but your ROI readout mode does not really work. Seems like you always read from the first cell, or just from a wrong cell. Since your sine wave period is not a multiple of the readout window, you see a phase jump between the beginning of your sampling window and the end of your sampling window. The little spikes before and after the jump are normal, since the first and last samples of the DRS4 readout might have some offset. Check that your FPGA really uses RSLOAD to start the readout, and not the "full readout".

The evaluation board might really help you, since you can compare 1:1 all control signals with yours.

Stefan

| QICHAOWU wrote: |

|

Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

|

|

|

|

934

|

Fri Apr 17 10:54:20 2026 |

QICHAOWU | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Dear Dr.Stefan

Thank you for your detailed response. Following your suggestion, I used an oscilloscope to observe the RSLOAD and SRCLK signals, and they conform to the readout timing described in the datasheet.

I can now confirm that the DRS4 occasionally fails to correctly update the stop position to cell 1023, or the stored waveform from cell 0 to the stop position is corrupted. As a result, part of the waveform comes from the most recent acquisition while the other part comes from an earlier one, causing the truncation I observed. This issue occurs with a certain probability—more than half of the acquisitions still yield complete, continuous waveforms.

Interestingly, when I use the same FPGA code and host software on the DRS4 evaluation board, no truncation occurs at all. I am currently comparing the behavior of the two setups from both hardware and software perspectives. Could you kindly provide some suggestions on further tests I could perform?

Thank you very much for your help.

Best regards,

Qichao Wu

| Stefan Ritt wrote: |

|

Actually looking at your waveforms again, I think I understand maybe your problem. You stop the DRS4 randomly, but your ROI readout mode does not really work. Seems like you always read from the first cell, or just from a wrong cell. Since your sine wave period is not a multiple of the readout window, you see a phase jump between the beginning of your sampling window and the end of your sampling window. The little spikes before and after the jump are normal, since the first and last samples of the DRS4 readout might have some offset. Check that your FPGA really uses RSLOAD to start the readout, and not the "full readout".

The evaluation board might really help you, since you can compare 1:1 all control signals with yours.

Stefan

| QICHAOWU wrote: |

|

Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

|

|

|

933

|

Fri Mar 27 09:56:06 2026 |

Stefan Ritt | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Actually looking at your waveforms again, I think I understand maybe your problem. You stop the DRS4 randomly, but your ROI readout mode does not really work. Seems like you always read from the first cell, or just from a wrong cell. Since your sine wave period is not a multiple of the readout window, you see a phase jump between the beginning of your sampling window and the end of your sampling window. The little spikes before and after the jump are normal, since the first and last samples of the DRS4 readout might have some offset. Check that your FPGA really uses RSLOAD to start the readout, and not the "full readout".

The evaluation board might really help you, since you can compare 1:1 all control signals with yours.

Stefan

| QICHAOWU wrote: |

|

Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

|

|

932

|

Thu Mar 5 15:39:30 2026 |

QICHAOWU | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Thank you for your prompt reply. We have developed our own DRS4-based hardware and successfully read out all 1024 bins using ROI mode. However, we are encountering the waveform truncation issue mentioned earlier. If possible, we would also like to purchase an evaluation board for reference.

| Stefan Ritt wrote: |

|

Does this happen with your own hardware or with the DRS4 evaluation board? If it's your own hardware, do you read out all 1024 bins in the ROI mode or only a partial waveforem?

| QICHAOWU wrote: |

|

Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

|

|

|

931

|

Thu Mar 5 14:52:07 2026 |

Stefan Ritt | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Does this happen with your own hardware or with the DRS4 evaluation board? If it's your own hardware, do you read out all 1024 bins in the ROI mode or only a partial waveforem?

| QICHAOWU wrote: |

|

Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

|

|

930

|

Thu Mar 5 14:37:48 2026 |

QICHAOWU | Waveform Truncation Near the Cell0-Cell1023 Boundary in DRS4 ROI Readout Mode | Dear Dr. Stefan Ritt

I am writing to seek your advice regarding an issue I encountered while using the DRS4 chip in ROI (Region of Interest) readout mode to sample waveforms. My name is Qichao Wu, and I have been working with the DRS4 for waveform sampling.

In my setup, I input two identical sine waves (with a period of 250 ns and the same phase) into two different channels of the same DRS4 chip. Ideally, the waveforms acquired from both channels should completely overlap, as shown in Figure 1. However, I occasionally observe that the waveform from one of the channels is truncated. The truncated portion appears to originate from a different segment of the input signal, resulting in only partial overlap between the two channels. This phenomenon is illustrated in Figure 1. Additionally, there are instances where both channels exhibit truncation simultaneously, as depicted in Figure 2.

I have confirmed this issue by observing the truncated waveforms directly on an oscilloscope when the DRS4 is operated in ROI mode. Notably, the truncation points always occur near cell 0 and cell 1023 of the DRS4 switch array.

Could you kindly provide guidance on how to resolve or mitigate this issue? Any suggestions or insights you could offer would be greatly appreciated.

I look forward to your positive response and thank you in advance for your time and assistance.

Best regards,

Qichao Wu

|

| Attachment 1: figure1.png

|

|

| Attachment 2: figure2.png

|

|

| Attachment 3: figure3.png

|

|

|

929

|

Tue Aug 19 23:10:30 2025 |

Jonathan Bradshaw | Unexpected behaviour following RSRLOAD | Turns out it was a damaged DRS4 IC.

I ported the drs4_eval5_app code onto our board and observed much the same misbehaviour. So I bit the bullet and replaced the DRS4 IC, and things are going better.

| Jonathan Bradshaw wrote: |

|

Some images

Notes:

- top of the puicture shows the logic channels

- Red: SRCLK

- Blue: SRIN

- Green: SROUT

- Orange: normally WSROUT, but swapped to RSRLOAD for last picture

| Jonathan Bradshaw wrote: |

|

Hello

I'm working to bring up a new capture board using a DRS4 and I'm having a minor problem and a major problem.

Minor problem: if I send a reset signal into the DRS4, the PLL doesn't work right. If I leave NRSESET pin with a wek pullup (and never 'manually' reset the DRS4) it runs OK. Is there some minimum time I need to observe between sending a NRESET pulse and setting DENABLE high to start the PLL?

Major problem: I can't get the stop position.

What am I doing?

- Set DENABLE high

- Wait until DRS capture is requested (seconds to minutes)

- Configure Write Shift Register with 0b01010101

- Configure Write Control Register with 0b11111111

- Fill the Read Shift Register with 1024x '0's

- Set DWRITE high

- Await trigger (some milliseconds). During this phase address = 0b1011

- Set DWRITE low

- Wait ~ 40 ns

- Set address = 0b1101

- Wait ~ 150 us

- Pulse RSRLOAD high for 30 ns

- Wait 30 ns

- Sample SROUT to get top bit of Write Shift Register

- Set address = 0b0000

- Wait ~ 350 ns

- Begin clocking out analog samples

What's going wrong?

- When I look at the first 10 bits out of SROUT, I should see stop positions. However, these bits are almost always zero (I get 7 bits which are always 0 followed by 3 bits which are sometimes ones)

- When I probe the WSROUT pin (and remembering that DWRITE is low at this point), I expected to see a single one bit coming out of the read shift register as I apply 1024 pulses to SRCLK. Instead, I am seeing two set bits coming out of the read shift register

- When I plot the captured analog waveform it's a mess - it seems like 2 analog output buffers are enabling at once and fighting over the output voltage

Do you have any suggestions or warnings about proper deployment of the RSRLOAD pin?

I left this a bit late in my day for posting, so I'll need to follow up with some 'scope captures tomorrow.

|

|

|

|

928

|

Tue Aug 19 02:40:58 2025 |

Jonathan Bradshaw | Unexpected behaviour following RSRLOAD | Some images

Notes:

- top of the puicture shows the logic channels

- Red: SRCLK

- Blue: SRIN

- Green: SROUT

- Orange: normally WSROUT, but swapped to RSRLOAD for last picture

| Jonathan Bradshaw wrote: |

|

Hello

I'm working to bring up a new capture board using a DRS4 and I'm having a minor problem and a major problem.

Minor problem: if I send a reset signal into the DRS4, the PLL doesn't work right. If I leave NRSESET pin with a wek pullup (and never 'manually' reset the DRS4) it runs OK. Is there some minimum time I need to observe between sending a NRESET pulse and setting DENABLE high to start the PLL?

Major problem: I can't get the stop position.

What am I doing?

- Set DENABLE high

- Wait until DRS capture is requested (seconds to minutes)

- Configure Write Shift Register with 0b01010101

- Configure Write Control Register with 0b11111111

- Fill the Read Shift Register with 1024x '0's

- Set DWRITE high

- Await trigger (some milliseconds). During this phase address = 0b1011

- Set DWRITE low

- Wait ~ 40 ns

- Set address = 0b1101

- Wait ~ 150 us

- Pulse RSRLOAD high for 30 ns

- Wait 30 ns

- Sample SROUT to get top bit of Write Shift Register

- Set address = 0b0000

- Wait ~ 350 ns

- Begin clocking out analog samples

What's going wrong?

- When I look at the first 10 bits out of SROUT, I should see stop positions. However, these bits are almost always zero (I get 7 bits which are always 0 followed by 3 bits which are sometimes ones)

- When I probe the WSROUT pin (and remembering that DWRITE is low at this point), I expected to see a single one bit coming out of the read shift register as I apply 1024 pulses to SRCLK. Instead, I am seeing two set bits coming out of the read shift register

- When I plot the captured analog waveform it's a mess - it seems like 2 analog output buffers are enabling at once and fighting over the output voltage

Do you have any suggestions or warnings about proper deployment of the RSRLOAD pin?

I left this a bit late in my day for posting, so I'll need to follow up with some 'scope captures tomorrow.

|

|

| Attachment 1: Overview.png

|

|

| Attachment 2: config.png

|

|

| Attachment 3: config2.png

|

|

| Attachment 4: readout_overview.png

|

|

| Attachment 5: readout_problem.png

|

|

| Attachment 6: RSRLOAD.png

|

|

|

927

|

Mon Aug 18 06:52:51 2025 |

Jonathan Bradshaw | Unexpected behaviour following RSRLOAD | Hello

I'm working to bring up a new capture board using a DRS4 and I'm having a minor problem and a major problem.

Minor problem: if I send a reset signal into the DRS4, the PLL doesn't work right. If I leave NRSESET pin with a wek pullup (and never 'manually' reset the DRS4) it runs OK. Is there some minimum time I need to observe between sending a NRESET pulse and setting DENABLE high to start the PLL?

Major problem: I can't get the stop position.

What am I doing?

- Set DENABLE high

- Wait until DRS capture is requested (seconds to minutes)

- Configure Write Shift Register with 0b01010101

- Configure Write Control Register with 0b11111111

- Fill the Read Shift Register with 1024x '0's

- Set DWRITE high

- Await trigger (some milliseconds). During this phase address = 0b1011

- Set DWRITE low

- Wait ~ 40 ns

- Set address = 0b1101

- Wait ~ 150 us

- Pulse RSRLOAD high for 30 ns

- Wait 30 ns

- Sample SROUT to get top bit of Write Shift Register

- Set address = 0b0000

- Wait ~ 350 ns

- Begin clocking out analog samples

What's going wrong?

- When I look at the first 10 bits out of SROUT, I should see stop positions. However, these bits are almost always zero (I get 7 bits which are always 0 followed by 3 bits which are sometimes ones)

- When I probe the WSROUT pin (and remembering that DWRITE is low at this point), I expected to see a single one bit coming out of the read shift register as I apply 1024 pulses to SRCLK. Instead, I am seeing two set bits coming out of the read shift register

- When I plot the captured analog waveform it's a mess - it seems like 2 analog output buffers are enabling at once and fighting over the output voltage

Do you have any suggestions or warnings about proper deployment of the RSRLOAD pin?

I left this a bit late in my day for posting, so I'll need to follow up with some 'scope captures tomorrow. |

|

926

|

Mon Jul 7 16:53:26 2025 |

Stefan Ritt | Wrong Firmware Version: board has 13279, required is 15147. Board may not work properly | You have to use the software belonging to that board. You cannot use the newest software with an old board. Look here:

https://www.psi.ch/en/ltp-muon-physics/software-download

So you need teh software version 2.0.

/Stefan

|

|

925

|

Sat Jul 5 04:36:13 2025 |

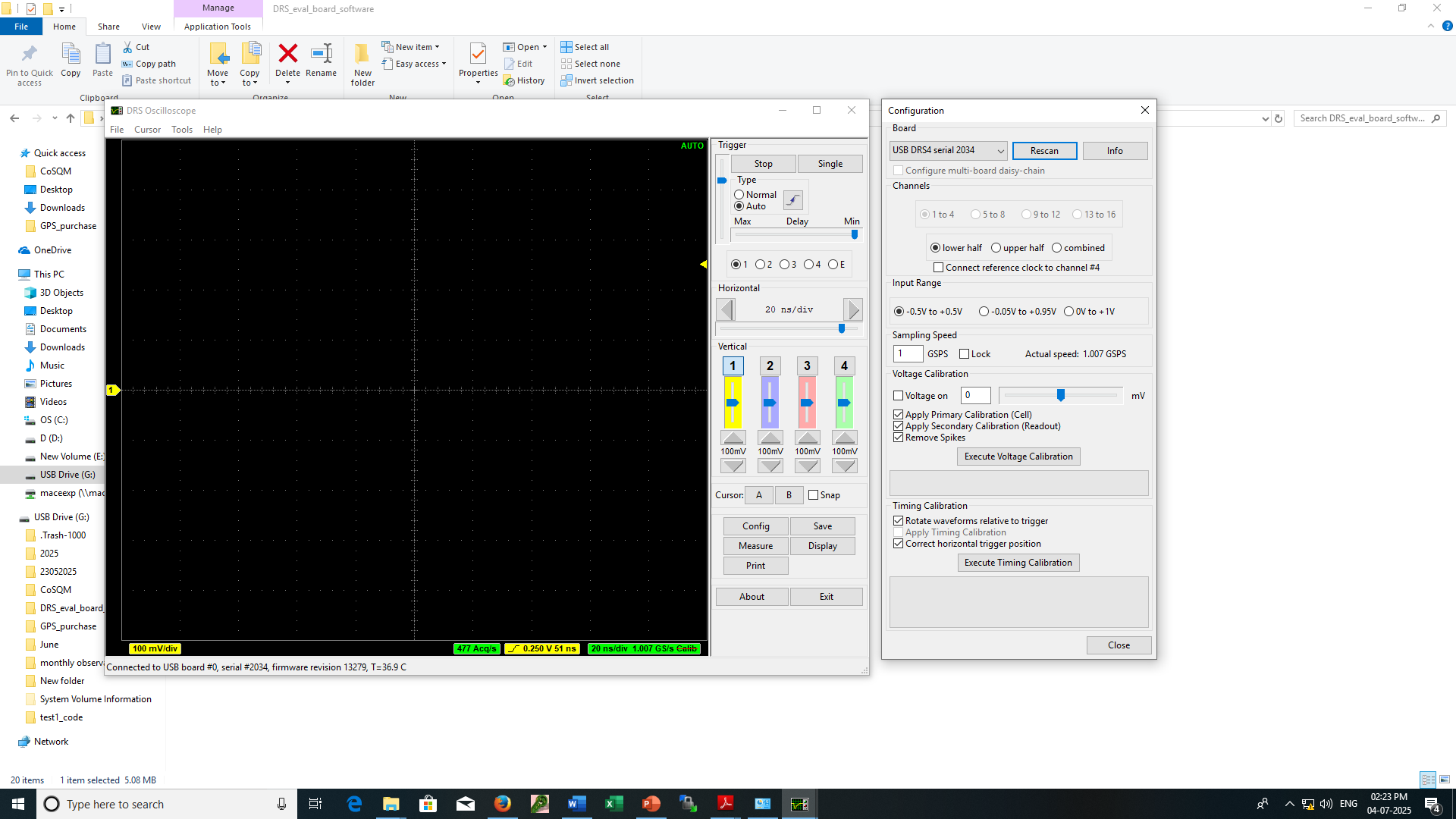

Sandeep Godiyal | Wrong Firmware Version: board has 13279, required is 15147. Board may not work properly | I am using DRS4 Evaluation Board Rev.: 2.0.. Command Line interface: "drscl" detecting the board with message: Found DRS4 board 0 on USB, serial #2034, firmware revision 13279, also info command also working.

In "drsosc" interface: Getting this message: Wrong Firmware Version: board has 13279, required is 15147. Board may not work properly. In "config" I checked it is detecting the board.

Software version, I am using is: "drs505.exe"

How can I resolve these issues, please guide! |

| Attachment 1: drseval1.png

|

|

|

924

|

Thu May 15 00:01:20 2025 |

Jonathan Bradshaw | Handling of Write Shift Register and Write Config Register | All right, thank you for the clarification.

| Stefan Ritt wrote: |

|

Yes this is correct. Anyhow, even if it would be working, you would not be happy with it. After having designed ~10 boards with the DRS4 chip, I learned the hard way that any digital activity on the board during the sampling phase is strictly forbidden. You see crosstalk up to 100's of mV in some cases (with a preamplifier on the board, 10-20mV without preamp). So rule #1 is to keep the board as "quite" as possible when sampling the input. If you would readout the odd channels of the DRS4 during sampling of the even channels, you would probably get so much crosstalk that the samples are almost unusable. Even if you would do this with two DRS4 chips next to each other, you have to make sure to put proper grounding between the two chips, and operate them completely independent (like each one has it's onw contol lines going to the FPGA). Designing such boards is not so easy and takes lots of experience from the layouter.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi Stefan

Just so I'm 100% clear; is there no reliable way to perform 2 segmented captures with a single DRS4 IC?

While not a showstopper, this is a bit disappointing.

| Stefan Ritt wrote: |

|

This is correct. Setting A0-A3 to 0b1101 multiplexes the Shift Write Register to SROUT, so you will either a "0" or a "1" depending on which of the two channels was written last.

Your segmented capture does unfortunately not work. Due to a bug in the silicon, the first (e.g. even) written channel gets half overwritten when you start sampling the second (odd) channel. I should remove that from the documentation.

Furthermore, reading the chip while writing on the "other side" introduces quite some additional noise. The recommended way to do simultaneous reading and writing is therefore to use two separate DRS4 chips and split the input signals to both chips, then read from one chip while writing to the other chip. This keeps the crosstalk at a minimum and both chips run at full performance.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)?

|

|

|

|

|

|

923

|

Tue May 13 08:51:34 2025 |

Stefan Ritt | Handling of Write Shift Register and Write Config Register | Yes this is correct. Anyhow, even if it would be working, you would not be happy with it. After having designed ~10 boards with the DRS4 chip, I learned the hard way that any digital activity on the board during the sampling phase is strictly forbidden. You see crosstalk up to 100's of mV in some cases (with a preamplifier on the board, 10-20mV without preamp). So rule #1 is to keep the board as "quite" as possible when sampling the input. If you would readout the odd channels of the DRS4 during sampling of the even channels, you would probably get so much crosstalk that the samples are almost unusable. Even if you would do this with two DRS4 chips next to each other, you have to make sure to put proper grounding between the two chips, and operate them completely independent (like each one has it's onw contol lines going to the FPGA). Designing such boards is not so easy and takes lots of experience from the layouter.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi Stefan

Just so I'm 100% clear; is there no reliable way to perform 2 segmented captures with a single DRS4 IC?

While not a showstopper, this is a bit disappointing.

| Stefan Ritt wrote: |

|

This is correct. Setting A0-A3 to 0b1101 multiplexes the Shift Write Register to SROUT, so you will either a "0" or a "1" depending on which of the two channels was written last.

Your segmented capture does unfortunately not work. Due to a bug in the silicon, the first (e.g. even) written channel gets half overwritten when you start sampling the second (odd) channel. I should remove that from the documentation.

Furthermore, reading the chip while writing on the "other side" introduces quite some additional noise. The recommended way to do simultaneous reading and writing is therefore to use two separate DRS4 chips and split the input signals to both chips, then read from one chip while writing to the other chip. This keeps the crosstalk at a minimum and both chips run at full performance.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)?

|

|

|

|

|

922

|

Tue May 13 04:10:30 2025 |

Jonathan Bradshaw | Handling of Write Shift Register and Write Config Register | Hi Stefan

Just so I'm 100% clear; is there no reliable way to perform 2 segmented captures with a single DRS4 IC?

While not a showstopper, this is a bit disappointing.

| Stefan Ritt wrote: |

|

This is correct. Setting A0-A3 to 0b1101 multiplexes the Shift Write Register to SROUT, so you will either a "0" or a "1" depending on which of the two channels was written last.

Your segmented capture does unfortunately not work. Due to a bug in the silicon, the first (e.g. even) written channel gets half overwritten when you start sampling the second (odd) channel. I should remove that from the documentation.

Furthermore, reading the chip while writing on the "other side" introduces quite some additional noise. The recommended way to do simultaneous reading and writing is therefore to use two separate DRS4 chips and split the input signals to both chips, then read from one chip while writing to the other chip. This keeps the crosstalk at a minimum and both chips run at full performance.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)?

|

|

|

|

921

|

Fri May 9 08:26:17 2025 |

Stefan Ritt | Clarification of full channel readout | The full readout mode is not really recommended since you have to pull out the stop position separately. Just do the ROI readout using the RSRLOAD signal, and then do 1024 samples, which also gives you the full waveform, but also the stop position in a single readout cyclce. The "full readout mode" is more there for "historical reasons", but nobody really uses it any more.

If you are interested in all details of the control signals, I propose you have a look at the VHDL code which comes with the software distribution. It's contained in the "firmware" subdirectoy and called drs4_eval5_app.vhd

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're working on a new product using the DRS4 IC, and want to do a full readout from cell 0 (not just Region of Interest). I have a couple of questions I hope you can help me with:

- We plan to do a full readout sequence, starting at cell 0. Part of that sequence includes pulsing RSRLOAD and reading out the stop position as shown in v0.9 datasheet Figure 15. What should the DRS4 address bits A3..0 be set to for reading out the stop position? (I’m assuming it’s 1011 ‘Address Read Shift Register’)

- What is the output delay from the falling edge of SRCLK to valid data at SROUT?

- For channel readout, we pulse SRCLK to advance the read shift register. The diagram shown in v0.9 datasheet Figure 12 appears to show that the analog output is updated on the rising edge of SRCLK. Is this correct or have I misread the diagram? (Other shift register transfers are clocked on the falling edge

- The DRS4 v0.9 datasheet Figure 7 shows that the Configuration register is clocked on the falling edge of SRCLK. Just below that is the text “The new register content becomes immediately active at the eighth rising edge of the SRCLK signal.” Should that perhaps read ‘… the eighth falling edge of the SRCLK signal’?

|

|

|

920

|

Fri May 9 08:17:50 2025 |

Stefan Ritt | Handling of Write Shift Register and Write Config Register | This is correct. Setting A0-A3 to 0b1101 multiplexes the Shift Write Register to SROUT, so you will either a "0" or a "1" depending on which of the two channels was written last.

Your segmented capture does unfortunately not work. Due to a bug in the silicon, the first (e.g. even) written channel gets half overwritten when you start sampling the second (odd) channel. I should remove that from the documentation.

Furthermore, reading the chip while writing on the "other side" introduces quite some additional noise. The recommended way to do simultaneous reading and writing is therefore to use two separate DRS4 chips and split the input signals to both chips, then read from one chip while writing to the other chip. This keeps the crosstalk at a minimum and both chips run at full performance.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)?

|

|

|

919

|

Thu May 8 23:41:03 2025 |

Jonathan Bradshaw | Handling of Write Shift Register and Write Config Register | Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)? |

|

918

|

Thu May 8 23:23:19 2025 |

Jonathan Bradshaw | Clarification of full channel readout | Hi all

We're working on a new product using the DRS4 IC, and want to do a full readout from cell 0 (not just Region of Interest). I have a couple of questions I hope you can help me with:

- We plan to do a full readout sequence, starting at cell 0. Part of that sequence includes pulsing RSRLOAD and reading out the stop position as shown in v0.9 datasheet Figure 15. What should the DRS4 address bits A3..0 be set to for reading out the stop position? (I’m assuming it’s 1011 ‘Address Read Shift Register’)

- What is the output delay from the falling edge of SRCLK to valid data at SROUT?

- For channel readout, we pulse SRCLK to advance the read shift register. The diagram shown in v0.9 datasheet Figure 12 appears to show that the analog output is updated on the rising edge of SRCLK. Is this correct or have I misread the diagram? (Other shift register transfers are clocked on the falling edge

- The DRS4 v0.9 datasheet Figure 7 shows that the Configuration register is clocked on the falling edge of SRCLK. Just below that is the text “The new register content becomes immediately active at the eighth rising edge of the SRCLK signal.” Should that perhaps read ‘… the eighth falling edge of the SRCLK signal’?

|

| Attachment 1: Screenshot_2025-05-09_093332.png

|

|

|