| ID |

Date |

Author |

Subject |

|

622

|

Fri Jul 7 10:31:47 2017 |

Stefan Ritt | Trigger setting (AND AND) OR (AND AND) | Unfortunately not with the current firmware.

Stefan

| Esperienza Giove wrote: |

|

Hello there,

is it possible to setup trigger in double AND configuration (a pair in and or other pair in and).

eg (CH 1 AND CH 2 ) OR ( CH 3 AND CH4)

Thank you

|

|

|

487

|

Thu Mar 31 19:30:26 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal | I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz |

|

488

|

Thu Mar 31 19:35:06 2016 |

Stefan Ritt | Trigger on the And of a positive and negative signal | No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

489

|

Thu Mar 31 19:44:38 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal | Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

490

|

Thu Mar 31 20:34:25 2016 |

Stefan Ritt | Trigger on the And of a positive and negative signal | Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

491

|

Thu Mar 31 20:38:05 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal | Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

492

|

Thu Mar 31 20:48:00 2016 |

Chris Thompson | Trigger on the And of a positive and negative signal | I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

493

|

Fri Apr 1 01:30:40 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal | Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

494

|

Fri Apr 1 22:09:07 2016 |

Chris Thompson | Trigger on the And of a positive and negative signal | The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

497

|

Sat Apr 2 17:22:34 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal | Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

498

|

Sun Apr 3 22:10:19 2016 |

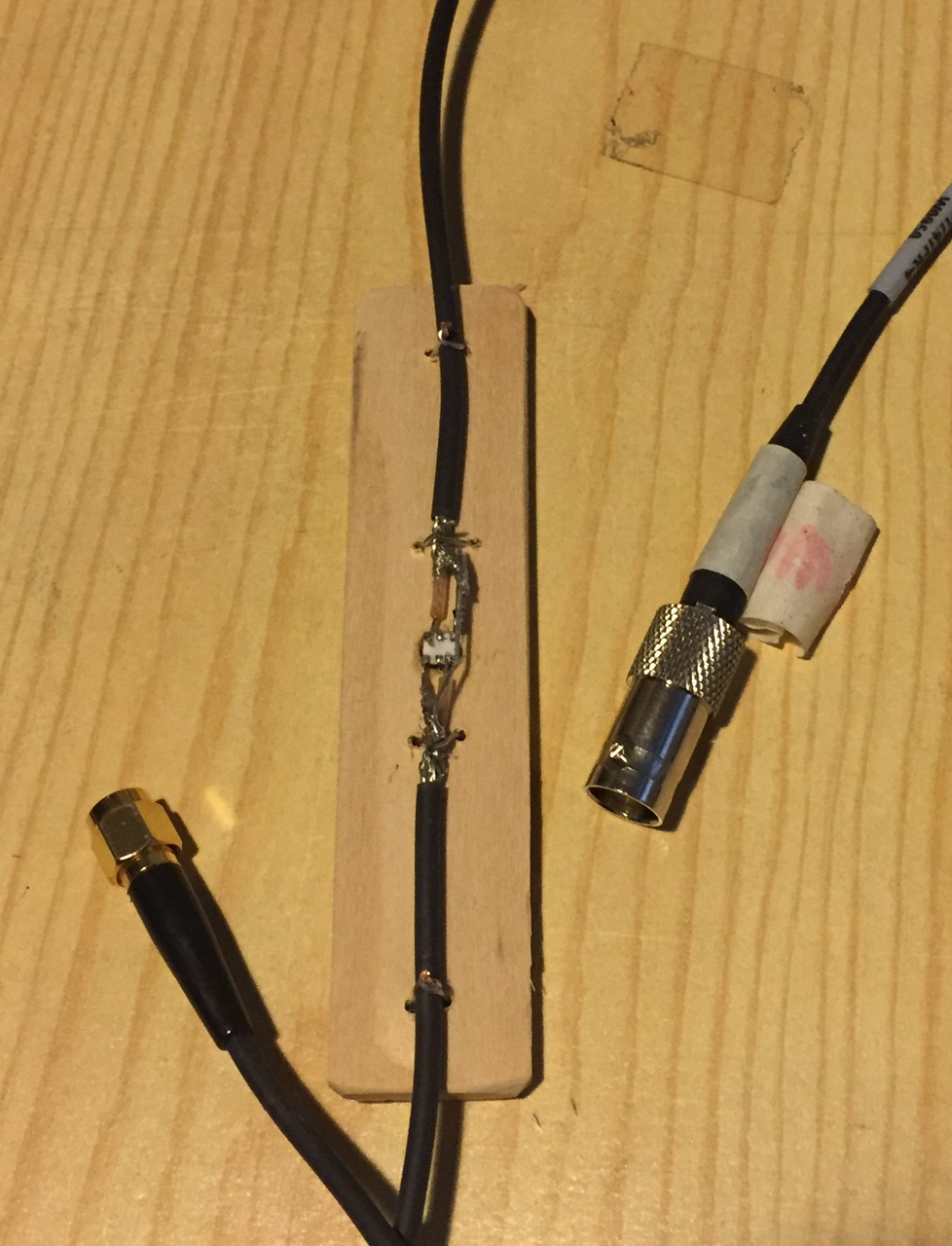

Chris Thompson | Trigger on the And of a positive and negative signal | No there are no other components. I put a photo of the inverter with its cables SMA and one end, BNC at the other. You can see it is very small. I glued the inverter to a piece of thin plywood, and fixed the cables to it before attempting to solder them to the pads on the ferite bead support

| Abaz Kryemadhi wrote: |

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

| Attachment 1: Pulse_inverter.jpg

|

|

|

499

|

Sun Apr 3 22:34:28 2016 |

Abaz Kryemadhi | Trigger on the And of a positive and negative signal | Thanks, great!

| Chris Thompson wrote: |

|

No there are no other components. I put a photo of the inverter with its cables SMA and one end, BNC at the other. You can see it is very small. I glued the inverter to a piece of thin plywood, and fixed the cables to it before attempting to solder them to the pads on the ferite bead support

| Abaz Kryemadhi wrote: |

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

|

|

23

|

Mon Dec 14 10:14:16 2009 |

Jinhong Wang | Trigger of DRS4 | Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn) |

|

24

|

Tue Dec 15 14:38:09 2009 |

Stefan Ritt | Trigger of DRS4 |

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest. |

|

25

|

Mon Dec 21 10:17:05 2009 |

Jinhong Wang | Trigger of DRS4 |

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn) |

|

26

|

Mon Dec 21 16:52:08 2009 |

Stefan Ritt | Trigger of DRS4 |

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

The amplitude of the analog signal is not degraded by the transparent mode, since the signal is buffered on the chip, and the output of this buffer is send off the chip. The waveform digitizing of course requires quite some current to charge up all capacitors, so there is maximum current of ~1mA for 5 GSPS. If you only have a weak signal source, your bandwidth might be limited by that. On the evaluation board for example we use passive transformers to produce the differential input signal from a single-ended signal. Although the transformers are rated 1 GHz Bandwidth, we only achieve 200 MHz with the passive transformers. By using active high speed differential drivers, you can get about 700 MHz right now.

If you have two channels with 500 ns and 510 ns trigger latency, there is no difference in the "domino stop position" since there is only one domino circuit per chip which can be stopped. So the stop position is the same for all eight channels on a chip. |

|

27

|

Tue Dec 22 01:30:55 2009 |

Jinhong Wang | Trigger of DRS4 |

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

The amplitude of the analog signal is not degraded by the transparent mode, since the signal is buffered on the chip, and the output of this buffer is send off the chip. The waveform digitizing of course requires quite some current to charge up all capacitors, so there is maximum current of ~1mA for 5 GSPS. If you only have a weak signal source, your bandwidth might be limited by that. On the evaluation board for example we use passive transformers to produce the differential input signal from a single-ended signal. Although the transformers are rated 1 GHz Bandwidth, we only achieve 200 MHz with the passive transformers. By using active high speed differential drivers, you can get about 700 MHz right now.

If you have two channels with 500 ns and 510 ns trigger latency, there is no difference in the "domino stop position" since there is only one domino circuit per chip which can be stopped. So the stop position is the same for all eight channels on a chip.

|

So you mean there is an analog buffer per channel? The analog signal is buffered there, before entering the sampling cells? Then, when will the buffer content be released and cleared? How shall I handle "Dwite" and "Denable" during a complete operation when an analog signal arrives in the transparent mode? I cannot find more information beyond the datasheet, a detailed description of the transparent mode (and the analog buffer, if possible) will be really helpful for me.

Best,

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn) |

|

28

|

Tue Dec 22 09:07:27 2009 |

Stefan Ritt | Trigger of DRS4 |

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

The amplitude of the analog signal is not degraded by the transparent mode, since the signal is buffered on the chip, and the output of this buffer is send off the chip. The waveform digitizing of course requires quite some current to charge up all capacitors, so there is maximum current of ~1mA for 5 GSPS. If you only have a weak signal source, your bandwidth might be limited by that. On the evaluation board for example we use passive transformers to produce the differential input signal from a single-ended signal. Although the transformers are rated 1 GHz Bandwidth, we only achieve 200 MHz with the passive transformers. By using active high speed differential drivers, you can get about 700 MHz right now.

If you have two channels with 500 ns and 510 ns trigger latency, there is no difference in the "domino stop position" since there is only one domino circuit per chip which can be stopped. So the stop position is the same for all eight channels on a chip.

|

So you mean there is an analog buffer per channel? The analog signal is buffered there, before entering the sampling cells? Then, when will the buffer content be released and cleared? How shall I handle "Dwite" and "Denable" during a complete operation when an analog signal arrives in the transparent mode? I cannot find more information beyond the datasheet, a detailed description of the transparent mode (and the analog buffer, if possible) will be really helpful for me.

Best,

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

There is one analog buffer per channel at the output, as indicated on the FUNCTIONAL BLOCK DIAGRAM of the datasheet. The section ANALOG INPUTS clearly states that the input signal has to load directly the sampling capacitors.

All other people using the chip so far correctly understood these things so far, so I believe more information beyond the datasheet is not necessary. I believe you have a principal problem of understanding, which can hardly be clarified by email. Best would be if you directly call me, I can then explain things to you. |

|

842

|

Mon Oct 25 18:48:04 2021 |

Javier Caravaca | Trigger multiple boards independently | Hello,

I recently acquired 4 DRS4 boards and I wanted to ask if it was possible to trigger them independently from the same computer.

I know that you can daisy-chain boards and trigger them all at the same time, but in my case, each of my boards record independent events, so I want them to trigger when trigger conditions are met in each board. I currently use the provided DRSOSC software, that can trigger on only the board that is being displayed at that moment. I tried opening several instances of DRSOSC to associate each to each board, but that is not possible since the second instance already does not find the boards. I wonder if there is a way of triggering from each board independently without having to use four computers.

Thank you,

Javier. |

|

845

|

Tue Oct 26 12:02:56 2021 |

Stefan Ritt | Trigger multiple boards independently | Unfortunately an independent operation from a single computer is not supported by the software. You can try to modify the drs_exam program and extend it. You can poll all boards in sequence and just read out that one which got a trigger, then start the loop again. But I don't know how good you are in programming. I needs a bit of experience to do that.

Stefan

| Javier Caravaca wrote: |

|

Hello,

I recently acquired 4 DRS4 boards and I wanted to ask if it was possible to trigger them independently from the same computer.

I know that you can daisy-chain boards and trigger them all at the same time, but in my case, each of my boards record independent events, so I want them to trigger when trigger conditions are met in each board. I currently use the provided DRSOSC software, that can trigger on only the board that is being displayed at that moment. I tried opening several instances of DRSOSC to associate each to each board, but that is not possible since the second instance already does not find the boards. I wonder if there is a way of triggering from each board independently without having to use four computers.

Thank you,

Javier.

|

|

|