| ID |

Date |

Author |

Subject |

|

603

|

Thu Apr 13 17:02:01 2017 |

Stefan Ritt | Stand-alone Time Calibration for PSI Board | Than you can try to isolate the code. Note that different SCAs might work differently. Like the DRS4 has a channel-to-channel jitter which others might not. But you will see.

Stefan

| Christian Farina wrote: |

|

Hi Stefan,

Thank you for your reply. I have read the paper already. I looked through the code and I understand that the LTC and GTC are performed by the AnalyzeSlope and AnalyzePeriod functions, respectively, correct? It seems to me to be a complicated business to re-write that part from scratch, at least for an inexperienced programmer like me. It made more sense to try to isolate that part from the original DRS.cpp. Ideally, I would like to have a stand-alone program that would work on any SCA without references to the drs hardware specifics.

| Stefan Ritt wrote: |

|

Hard to say. Timing calibration is quite delicate. If you start from scratch, better read this paper: https://arxiv.org/abs/1405.4975

If you try to extract the code from DRS.cpp, better read the paper, too. Probably it will not be possible to develop or extract the code without knowing how it works.

Best,

Stefan

| Christian Farina wrote: |

|

Hello everybody,

I was trying to create a stand-alone program that would perform a time calibration on the board. My goal would be the following.

- acquire about 10k sinus waveforms

- write them to disk (also for later reanalysis)

- run the time calibration on the recorded data

- store the clibration results in a file / database

Being not an expert, my question here is the following. Would it be easier to try to isolate the time calibration part from the DRS.cpp source code or re-write entirely the code from scratch?

Thanks.

|

|

|

|

|

602

|

Thu Apr 13 16:54:32 2017 |

Christian Farina | Stand-alone Time Calibration for PSI Board | Hi Stefan,

Thank you for your reply. I have read the paper already. I looked through the code and I understand that the LTC and GTC are performed by the AnalyzeSlope and AnalyzePeriod functions, respectively, correct? It seems to me to be a complicated business to re-write that part from scratch, at least for an inexperienced programmer like me. It made more sense to try to isolate that part from the original DRS.cpp. Ideally, I would like to have a stand-alone program that would work on any SCA without references to the drs hardware specifics.

| Stefan Ritt wrote: |

|

Hard to say. Timing calibration is quite delicate. If you start from scratch, better read this paper: https://arxiv.org/abs/1405.4975

If you try to extract the code from DRS.cpp, better read the paper, too. Probably it will not be possible to develop or extract the code without knowing how it works.

Best,

Stefan

| Christian Farina wrote: |

|

Hello everybody,

I was trying to create a stand-alone program that would perform a time calibration on the board. My goal would be the following.

- acquire about 10k sinus waveforms

- write them to disk (also for later reanalysis)

- run the time calibration on the recorded data

- store the clibration results in a file / database

Being not an expert, my question here is the following. Would it be easier to try to isolate the time calibration part from the DRS.cpp source code or re-write entirely the code from scratch?

Thanks.

|

|

|

|

601

|

Thu Apr 13 16:50:18 2017 |

Stefan Ritt | Stand-alone Time Calibration for PSI Board | Hard to say. Timing calibration is quite delicate. If you start from scratch, better read this paper: https://arxiv.org/abs/1405.4975

If you try to extract the code from DRS.cpp, better read the paper, too. Probably it will not be possible to develop or extract the code without knowing how it works.

Best,

Stefan

| Christian Farina wrote: |

|

Hello everybody,

I was trying to create a stand-alone program that would perform a time calibration on the board. My goal would be the following.

- acquire about 10k sinus waveforms

- write them to disk (also for later reanalysis)

- run the time calibration on the recorded data

- store the clibration results in a file / database

Being not an expert, my question here is the following. Would it be easier to try to isolate the time calibration part from the DRS.cpp source code or re-write entirely the code from scratch?

Thanks.

|

|

|

600

|

Thu Apr 13 16:42:21 2017 |

Christian Farina | Stand-alone Time Calibration for PSI Board | Hello everybody,

I was trying to create a stand-alone program that would perform a time calibration on the board. My goal would be the following.

- acquire about 10k sinus waveforms

- write them to disk (also for later reanalysis)

- run the time calibration on the recorded data

- store the clibration results in a file / database

Being not an expert, my question here is the following. Would it be easier to try to isolate the time calibration part from the DRS.cpp source code or re-write entirely the code from scratch?

Thanks. |

|

599

|

Tue Apr 11 09:41:44 2017 |

Stefan Ritt | drs4 registers behaviour | What I do is the following: Have the RESET input unconnected. When you power up, this makes an internal reset during the power up, and that's all you need. Then configure your registers using the sequences described in the manual. Then do not touch the RESET any more.

Stefan

| Giovanni Bruni wrote: |

|

Thank you Stefan for replying!

I have still the RESET issue in mind: how would you suggest to reset properly the DRS? Is there a particular procedure to follow instead of just sending a negative pulse to the RESET pin? Is it preferable to turn the DRS off and then restart?

Thanks!

Giovanni

| Stefan Ritt wrote: |

|

1. WRITE SHIFT register and CONFIG registers are initialized to "1" on power up, but if you want to change that, use A0-A3 etc. as you indicated.

2. If you address the READ SHIFT register by applyin "1011" to A0-A3, the input of the register is connected to SRIN. So in fig. 11, you apply 1023x"0" plus 1x"1", which effectively clears the register and keeps one "1" at the last position, so on the next rising clock this gets shifted into position #0. If you do the readout, and NOT addresing the READ SHIFT register, then the input of that register is connected to it's output internally. Therefore the single "1" keep rotating on every 1024 clock cycles.

| Giovanni Bruni wrote: |

|

Hej Stefan! Thank you for your answer!

Just to be sure to have understood properly:

1. Using the RESET line should be avoided. And in any case, the CONFIG register and the WRITE SHIFT register need to be initialized "by hand" using the A0-A3, SRCLK and SRIN pins. Is it correct?

2. Doing the procedure shown in Figure 11 will always inject a "1" in cell #0 of the READ SHIFT register, regardless if (before starting the procedure) there was a "1" in any other cell, right?

Thank you!

Giovanni

| Stefan Ritt wrote: |

|

Using the RESET line to reset registers is not a good idea since it can have some bad side-effects. The READ SHIFT register is NOT affected by RESET, so you have to inititialize these registers differently. To set a "1"-value at a defined position, you have to follow figure 11 in the data sheet. Once you executed that, your "1" is always at the same posiiton (namely cell #0), so after 1024 clock cycles you arrive at the same state, and do not have to re-do fig. 11 again.

Stefan

| Giovanni Bruni wrote: |

|

Hej everyone!

I have some questions regarding what happens to some DRS registers in some scenarios:

1. How are the registers affected by a RESET? According to the data sheet all the CONFIG REGISTER bits are initilialized to 1. But what about the WRITE SHIFT and the READ SHIFT registers? Are they affected somehow after a RESET has been applied?

2. Suppose the DRS is happily running and I have done some readouts in ROI mode, so that the only "1"-value bit in the READ SHIFT register is in a random position. If now I want to execute a FULL READOUT, should I use the procedure explained in the data sheet (figure 11) for the FULL READOUT mode? or is this procedure useless since my "1"-value bit is already set somewhere in the READ SHIFT register and therefore a ROI readout of 1024 cells would be the solution (and getting the initial position from the SROUT pin)?

Thanks a lot!

Have a nice day!

Giovanni

|

|

|

|

|

|

|

598

|

Tue Apr 11 09:07:33 2017 |

Giovanni Bruni | drs4 registers behaviour | Thank you Stefan for replying!

I have still the RESET issue in mind: how would you suggest to reset properly the DRS? Is there a particular procedure to follow instead of just sending a negative pulse to the RESET pin? Is it preferable to turn the DRS off and then restart?

Thanks!

Giovanni

| Stefan Ritt wrote: |

|

1. WRITE SHIFT register and CONFIG registers are initialized to "1" on power up, but if you want to change that, use A0-A3 etc. as you indicated.

2. If you address the READ SHIFT register by applyin "1011" to A0-A3, the input of the register is connected to SRIN. So in fig. 11, you apply 1023x"0" plus 1x"1", which effectively clears the register and keeps one "1" at the last position, so on the next rising clock this gets shifted into position #0. If you do the readout, and NOT addresing the READ SHIFT register, then the input of that register is connected to it's output internally. Therefore the single "1" keep rotating on every 1024 clock cycles.

| Giovanni Bruni wrote: |

|

Hej Stefan! Thank you for your answer!

Just to be sure to have understood properly:

1. Using the RESET line should be avoided. And in any case, the CONFIG register and the WRITE SHIFT register need to be initialized "by hand" using the A0-A3, SRCLK and SRIN pins. Is it correct?

2. Doing the procedure shown in Figure 11 will always inject a "1" in cell #0 of the READ SHIFT register, regardless if (before starting the procedure) there was a "1" in any other cell, right?

Thank you!

Giovanni

| Stefan Ritt wrote: |

|

Using the RESET line to reset registers is not a good idea since it can have some bad side-effects. The READ SHIFT register is NOT affected by RESET, so you have to inititialize these registers differently. To set a "1"-value at a defined position, you have to follow figure 11 in the data sheet. Once you executed that, your "1" is always at the same posiiton (namely cell #0), so after 1024 clock cycles you arrive at the same state, and do not have to re-do fig. 11 again.

Stefan

| Giovanni Bruni wrote: |

|

Hej everyone!

I have some questions regarding what happens to some DRS registers in some scenarios:

1. How are the registers affected by a RESET? According to the data sheet all the CONFIG REGISTER bits are initilialized to 1. But what about the WRITE SHIFT and the READ SHIFT registers? Are they affected somehow after a RESET has been applied?

2. Suppose the DRS is happily running and I have done some readouts in ROI mode, so that the only "1"-value bit in the READ SHIFT register is in a random position. If now I want to execute a FULL READOUT, should I use the procedure explained in the data sheet (figure 11) for the FULL READOUT mode? or is this procedure useless since my "1"-value bit is already set somewhere in the READ SHIFT register and therefore a ROI readout of 1024 cells would be the solution (and getting the initial position from the SROUT pin)?

Thanks a lot!

Have a nice day!

Giovanni

|

|

|

|

|

|

597

|

Mon Apr 10 14:05:17 2017 |

Stefan Ritt | drs4 registers behaviour | 1. WRITE SHIFT register and CONFIG registers are initialized to "1" on power up, but if you want to change that, use A0-A3 etc. as you indicated.

2. If you address the READ SHIFT register by applyin "1011" to A0-A3, the input of the register is connected to SRIN. So in fig. 11, you apply 1023x"0" plus 1x"1", which effectively clears the register and keeps one "1" at the last position, so on the next rising clock this gets shifted into position #0. If you do the readout, and NOT addresing the READ SHIFT register, then the input of that register is connected to it's output internally. Therefore the single "1" keep rotating on every 1024 clock cycles.

| Giovanni Bruni wrote: |

|

Hej Stefan! Thank you for your answer!

Just to be sure to have understood properly:

1. Using the RESET line should be avoided. And in any case, the CONFIG register and the WRITE SHIFT register need to be initialized "by hand" using the A0-A3, SRCLK and SRIN pins. Is it correct?

2. Doing the procedure shown in Figure 11 will always inject a "1" in cell #0 of the READ SHIFT register, regardless if (before starting the procedure) there was a "1" in any other cell, right?

Thank you!

Giovanni

| Stefan Ritt wrote: |

|

Using the RESET line to reset registers is not a good idea since it can have some bad side-effects. The READ SHIFT register is NOT affected by RESET, so you have to inititialize these registers differently. To set a "1"-value at a defined position, you have to follow figure 11 in the data sheet. Once you executed that, your "1" is always at the same posiiton (namely cell #0), so after 1024 clock cycles you arrive at the same state, and do not have to re-do fig. 11 again.

Stefan

| Giovanni Bruni wrote: |

|

Hej everyone!

I have some questions regarding what happens to some DRS registers in some scenarios:

1. How are the registers affected by a RESET? According to the data sheet all the CONFIG REGISTER bits are initilialized to 1. But what about the WRITE SHIFT and the READ SHIFT registers? Are they affected somehow after a RESET has been applied?

2. Suppose the DRS is happily running and I have done some readouts in ROI mode, so that the only "1"-value bit in the READ SHIFT register is in a random position. If now I want to execute a FULL READOUT, should I use the procedure explained in the data sheet (figure 11) for the FULL READOUT mode? or is this procedure useless since my "1"-value bit is already set somewhere in the READ SHIFT register and therefore a ROI readout of 1024 cells would be the solution (and getting the initial position from the SROUT pin)?

Thanks a lot!

Have a nice day!

Giovanni

|

|

|

|

|

596

|

Mon Apr 10 13:41:41 2017 |

Giovanni Bruni | drs4 registers behaviour | Hej Stefan! Thank you for your answer!

Just to be sure to have understood properly:

1. Using the RESET line should be avoided. And in any case, the CONFIG register and the WRITE SHIFT register need to be initialized "by hand" using the A0-A3, SRCLK and SRIN pins. Is it correct?

2. Doing the procedure shown in Figure 11 will always inject a "1" in cell #0 of the READ SHIFT register, regardless if (before starting the procedure) there was a "1" in any other cell, right?

Thank you!

Giovanni

| Stefan Ritt wrote: |

|

Using the RESET line to reset registers is not a good idea since it can have some bad side-effects. The READ SHIFT register is NOT affected by RESET, so you have to inititialize these registers differently. To set a "1"-value at a defined position, you have to follow figure 11 in the data sheet. Once you executed that, your "1" is always at the same posiiton (namely cell #0), so after 1024 clock cycles you arrive at the same state, and do not have to re-do fig. 11 again.

Stefan

| Giovanni Bruni wrote: |

|

Hej everyone!

I have some questions regarding what happens to some DRS registers in some scenarios:

1. How are the registers affected by a RESET? According to the data sheet all the CONFIG REGISTER bits are initilialized to 1. But what about the WRITE SHIFT and the READ SHIFT registers? Are they affected somehow after a RESET has been applied?

2. Suppose the DRS is happily running and I have done some readouts in ROI mode, so that the only "1"-value bit in the READ SHIFT register is in a random position. If now I want to execute a FULL READOUT, should I use the procedure explained in the data sheet (figure 11) for the FULL READOUT mode? or is this procedure useless since my "1"-value bit is already set somewhere in the READ SHIFT register and therefore a ROI readout of 1024 cells would be the solution (and getting the initial position from the SROUT pin)?

Thanks a lot!

Have a nice day!

Giovanni

|

|

|

|

595

|

Mon Apr 10 10:50:57 2017 |

Stefan Ritt | drs4 registers behaviour | Using the RESET line to reset registers is not a good idea since it can have some bad side-effects. The READ SHIFT register is NOT affected by RESET, so you have to inititialize these registers differently. To set a "1"-value at a defined position, you have to follow figure 11 in the data sheet. Once you executed that, your "1" is always at the same posiiton (namely cell #0), so after 1024 clock cycles you arrive at the same state, and do not have to re-do fig. 11 again.

Stefan

| Giovanni Bruni wrote: |

|

Hej everyone!

I have some questions regarding what happens to some DRS registers in some scenarios:

1. How are the registers affected by a RESET? According to the data sheet all the CONFIG REGISTER bits are initilialized to 1. But what about the WRITE SHIFT and the READ SHIFT registers? Are they affected somehow after a RESET has been applied?

2. Suppose the DRS is happily running and I have done some readouts in ROI mode, so that the only "1"-value bit in the READ SHIFT register is in a random position. If now I want to execute a FULL READOUT, should I use the procedure explained in the data sheet (figure 11) for the FULL READOUT mode? or is this procedure useless since my "1"-value bit is already set somewhere in the READ SHIFT register and therefore a ROI readout of 1024 cells would be the solution (and getting the initial position from the SROUT pin)?

Thanks a lot!

Have a nice day!

Giovanni

|

|

|

594

|

Mon Apr 10 10:48:03 2017 |

Stefan Ritt | DRS4 eval board v4 coincidence firmware changes for triger for short pulses | You have to download the package for your board, which then includes also the correct firmware for your board. If you have a V4 board, your firmware is in drs-4.0.2.tar.gz which you can download from Dropbox at https://www.dropbox.com/sh/clqo7ekr0ysbrip/AACoWJzrQAbf3WiBJHG89bGGa?dl=0

| Martin Petriska wrote: |

|

I would like to implement fpga firmware changes for DRS4 eval board v4 to put there posibility for standard coincidence (for example to get triger on two short (5ns pulses from Plastic scintilator) in 100ns coincidence window), Similar but more complex was done for eval v.5 boards ( https://forge.physik.rwth-aachen.de/projects/drs4-rwth ) Im beginner in state of FPGA design, but hope it will be not so dificult to implement same functionality in eval4 board. Is there any SVN server with firmware sources for evaluation board? Im litle bit confused with different firmware sources in linux and windows installation packages, For example whose are last eval4 board firmware souces ? (There are some eval4 sources in 5.0.6 files, but not sure if its workable)

May be didnt make same changes already?

|

|

|

593

|

Mon Apr 10 08:50:11 2017 |

Giovanni Bruni | drs4 registers behaviour | Hej everyone!

I have some questions regarding what happens to some DRS registers in some scenarios:

1. How are the registers affected by a RESET? According to the data sheet all the CONFIG REGISTER bits are initilialized to 1. But what about the WRITE SHIFT and the READ SHIFT registers? Are they affected somehow after a RESET has been applied?

2. Suppose the DRS is happily running and I have done some readouts in ROI mode, so that the only "1"-value bit in the READ SHIFT register is in a random position. If now I want to execute a FULL READOUT, should I use the procedure explained in the data sheet (figure 11) for the FULL READOUT mode? or is this procedure useless since my "1"-value bit is already set somewhere in the READ SHIFT register and therefore a ROI readout of 1024 cells would be the solution (and getting the initial position from the SROUT pin)?

Thanks a lot!

Have a nice day!

Giovanni |

|

592

|

Wed Apr 5 12:40:16 2017 |

Martin Petriska | DRS4 eval board v4 coincidence firmware changes for triger for short pulses | I would like to implement fpga firmware changes for DRS4 eval board v4 to put there posibility for standard coincidence (for example to get triger on two short (5ns pulses from Plastic scintilator) in 100ns coincidence window), Similar but more complex was done for eval v.5 boards ( https://forge.physik.rwth-aachen.de/projects/drs4-rwth ) Im beginner in state of FPGA design, but hope it will be not so dificult to implement same functionality in eval4 board. Is there any SVN server with firmware sources for evaluation board? Im litle bit confused with different firmware sources in linux and windows installation packages, For example whose are last eval4 board firmware souces ? (There are some eval4 sources in 5.0.6 files, but not sure if its workable)

May be didnt make same changes already? |

|

591

|

Wed Apr 5 12:28:28 2017 |

Stefan Ritt | drscl doesn't find eval board but drsosc does (Windows 7) | Two people report now this problem, while this works fine at our lab. So I'm puzzled right now.

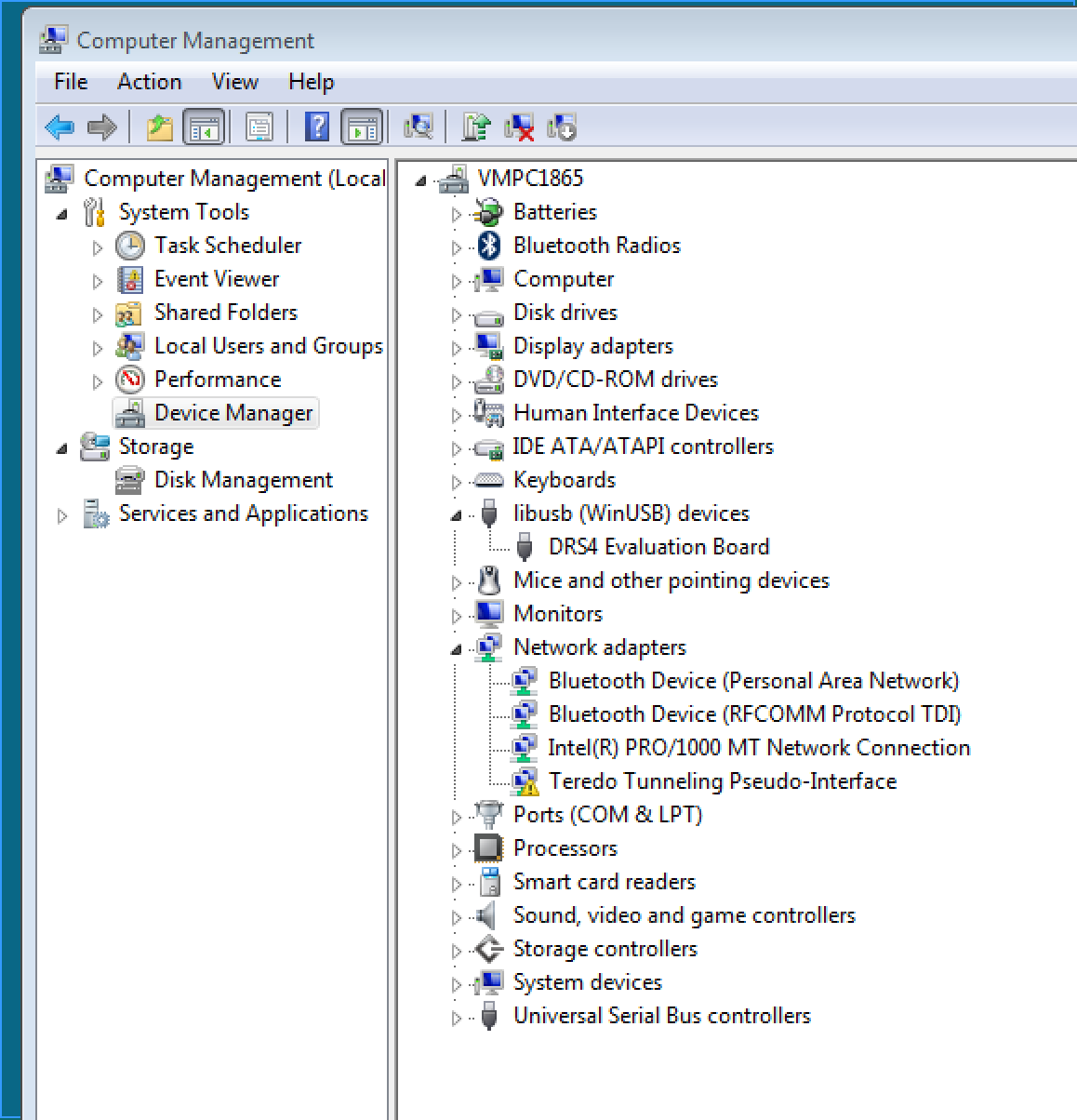

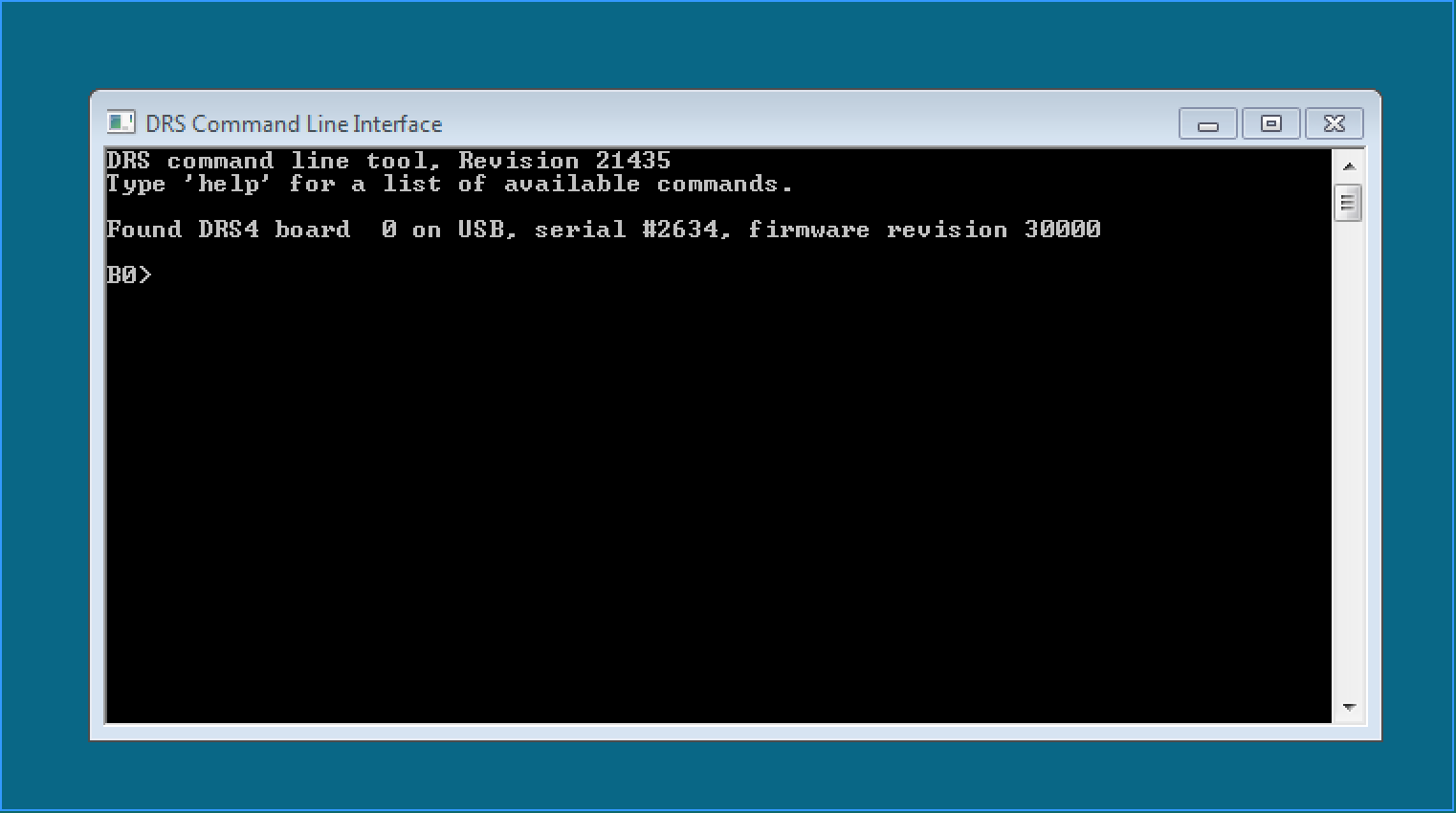

I attach two screenshots from the device manager and the Command Line interface. Can you compare it with what you see? Which is the firmware version of your evaluaiton board?

Stefan

| Jim Freeman wrote: |

|

I cannot find the EVAL board using drscl version 5.06 while the drsosc works fine. I tried 2 different eval boards and 2 different computers and the same effect. I looked under device manager at the libusb and the drs4 was there, and checked the driver which was found to be up to date.

|

|

| Attachment 1: Screen_Shot_2017-04-05_at_12.27.46_.png

|

|

| Attachment 2: Screen_Shot_2017-04-05_at_11.45.07_.png

|

|

|

590

|

Tue Mar 28 21:53:12 2017 |

Jim Freeman | drscl doesn't find eval board but drsosc does (Windows 7) | I cannot find the EVAL board using drscl version 5.06 while the drsosc works fine. I tried 2 different eval boards and 2 different computers and the same effect. I looked under device manager at the libusb and the drs4 was there, and checked the driver which was found to be up to date. |

|

589

|

Fri Feb 24 18:35:38 2017 |

Stefan Ritt | Passing parameters to drscl | This is indeed currently not implemented. But there is a simple C program drs_exam.cpp, which connects to a board and safes some data. You could modify that program to your needs.

Stefan

| Tarik Zengin wrote: |

|

Hi everyone,

I wonder if there is a way to pass parameters to drscl. What I specifically want to do is calling drscl from a shell script and read/save some data. I want to schedule a measurement. Therefore I need to call drscl from the command line using some parameters.

It would look something like this;

#!/bin/bash

for i in {0..100}

do

echo "Reading $i"

./drscl read 0 0 test.xml

sleep 1

done

This doesn't work of course. drscl won't take arguments from the command line. Can you suggest a way to do this please?

Thank you.

|

|

|

588

|

Fri Feb 24 17:34:28 2017 |

Tarik Zengin | Passing parameters to drscl | Hi everyone,

I wonder if there is a way to pass parameters to drscl. What I specifically want to do is calling drscl from a shell script and read/save some data. I want to schedule a measurement. Therefore I need to call drscl from the command line using some parameters.

It would look something like this;

#!/bin/bash

for i in {0..100}

do

echo "Reading $i"

./drscl read 0 0 test.xml

sleep 1

done

This doesn't work of course. drscl won't take arguments from the command line. Can you suggest a way to do this please?

Thank you. |

|

587

|

Tue Jan 31 08:40:04 2017 |

Stefan Ritt | LLD and ULD discriminations, | Not inside the board. Each channel has a single discriminator. You can select to trigger on a rising or falling edge, but you don't have two levels. What you can do however is to make an external trigger, like using old NIM logic. You can make discrimaiton with different levels and use a coincidence unit to combine them. Then feed the trigger into the external trigger input of the evaluation board (5V TTL level, not NIM level!).

Stefan

| VO HONG HAI wrote: |

| Dear Stefan, Is there any way to develop LLD and ULD discrimination in DSR-4 evaluation board? Best regards, V.H.Hai |

|

|

586

|

Tue Jan 31 01:37:35 2017 |

VO HONG HAI | LLD and ULD discriminations, | | Dear Stefan,

Is there any way to develop LLD and ULD discrimination in DSR-4 evaluation board?

Best regards,

V.H.Hai |

|

585

|

Mon Jan 30 16:37:33 2017 |

Stefan Ritt | AND trigger problems | In the evaluation board we use an ADCMP601 comparator, which has a setup and hold time of 4.6 ns. So a pulse which exceeds the threshold for less than 4.6 ns will not trigger the board. If you AND two signals together, an additional constraint might apply on the coincidence pulse. This is processed in the FPGA, but once it becomes too short, it won't trigger the board as well. I never made a real measurement of that, but I would not be suprised if the coicidence signal (output of AND), needs to be at least 4-5 ns wide.

If you need more refined trigger conditions, make yourself an old-fashioned external trigger (with NIM modules for example), stretch the output to 10 ns and feed it into the external trigger input of the DRS4 board (5V CMOS logic, not NIM!).

Best,

Stefan

| Danny Petschke wrote: |

|

Dear Stefan,

I have 2 identical pulses as a splittet signal with an amplitude of 300mV. Range is -0.5-0.5V, 5.12GSamp using the Evaluation-Board. Both signals are triggered in AND logic. One of the signals is delayed by a fixed value of 1-50ns for testing. On increasing the trigger Level from 10% to 50% of amplitude (pulse rise time is 2.5ns) pulses cannot anymore triggered above 4-5ns delay. It means there is a proportionality between the trigger level and the available range where 2 signals can be triggered in AND logic (Time-difference between 2 pulses). Do I anything misunderstand or is the time the comparator needs by higher trigger Levels for comparation longer than the 200ns at 5.12GSamp?

Board was timing and voltage calibrated before.

Thx

Danny

|

|

|

584

|

Sat Jan 28 14:11:58 2017 |

Danny Petschke | AND trigger problems | Dear Stefan,

I have 2 identical pulses as a splittet signal with an amplitude of 300mV. Range is -0.5-0.5V, 5.12GSamp using the Evaluation-Board. Both signals are triggered in AND logic. One of the signals is delayed by a fixed value of 1-50ns for testing. On increasing the trigger Level from 10% to 50% of amplitude (pulse rise time is 2.5ns) pulses cannot anymore triggered above 4-5ns delay. It means there is a proportionality between the trigger level and the available range where 2 signals can be triggered in AND logic (Time-difference between 2 pulses). Do I anything misunderstand or is the time the comparator needs by higher trigger Levels for comparation longer than the 200ns at 5.12GSamp?

Board was timing and voltage calibrated before.

Thx

Danny |

|