| ID |

Date |

Author |

Subject |

|

129

|

Fri Sep 9 09:31:33 2011 |

Stefan Ritt | DRS4 and AD9222 |

| Guillaume Blanchard wrote: |

|

Thank you for your answers,

Another question : Have you ever tried to split the differential signal at the output of the DRS4 chip ? For example to feed both an AD9222 and a diff. amplifier (followed by discriminators) ?

|

Yes. Just have a look at the schematics of the evaluation board. This is exactly what is done there.

Actually in the newest version we went one step further and put the comparator at the input of the DRS chip. This way it is active even during the readout of the DRS4 chip and we can use this as a counter to count the overall hit rate at the input.

- Stefan |

|

130

|

Fri Sep 16 22:06:07 2011 |

Andriy Zatserklyaniy | compilation error for version 4.0.0 on linux | Hi Stefan,

When I compiled DRS4 software version 4.0.0 on Linux (Debian Squeeze) I got this compilation error:

g++ -g -O2 -Wall -Wuninitialized -fno-strict-aliasing -Iinclude -DOS_LINUX -DHAVE_LIBUSB -DUSE_DRS_MUTEX musbstd.o mxml.o strlcpy.o DRS.o ConfigDialog.o DOFrame.o DOScreen.o DRSOsc.o MeasureDialog.o Measurement.o Osci.o InfoDialog.o DisplayDialog.o AboutDialog.o EPThread.o rb.o main.o -o drsosc -lpthread -lutil -lusb -pthread -lwx_gtk2u_richtext-2.8 -lwx_gtk2u_aui-2.8 -lwx_gtk2u_xrc-2.8 -lwx_gtk2u_qa-2.8 -lwx_gtk2u_html-2.8 -lwx_gtk2u_adv-2.8 -lwx_gtk2u_core-2.8 -lwx_baseu_xml-2.8 -lwx_baseu_net-2.8 -lwx_baseu-2.8

DOFrame.o: In function `DOFrame':

/srv/zatserkl/work/drs4/drs-4.0.0/src/DOFrame.cpp:237: undefined reference to `TriggerDialog::TriggerDialog(wxWindow*)'

/srv/zatserkl/work/drs4/drs-4.0.0/src/DOFrame.cpp:237: undefined reference to `TriggerDialog::TriggerDialog(wxWindow*)'

collect2: ld returned 1 exit status

make: *** [drsosc] Error 1

To fix it I added TriggerDialog.o into CPP_OBJ line of the Makefile:

CPP_OBJ = DRS.o ConfigDialog.o DOFrame.o DOScreen.o DRSOsc.o MeasureDialog.o Measurement.o Osci.o InfoDialog.o DisplayDialog.o AboutDialog.o EPThread.o rb.o TriggerDialog.o

Best,

Andriy. |

|

131

|

Mon Sep 19 08:53:22 2011 |

Stefan Ritt | compilation error for version 4.0.0 on linux |

| Andriy Zatserklyaniy wrote: |

|

To fix it I added TriggerDialog.o into CPP_OBJ line of the Makefile:

|

Thanks. I added your fix to the current 4.0.0 distribution.

- Stefan |

|

132

|

Sat Oct 15 04:45:25 2011 |

Aurelien Bouvier | DRS4 eval board: readout rate | Hi,

Our setup uses a DRS4 evaluation board (version 2.0).

Although we trigger the board at a rate of ~4kHz (on channel2), readout through USB2 is only happening at a rate of ~125Hz.

After some investigation, we could pin down that it is due to the time it takes to complete the following commands: musb_write() and musb_read() which both take ~150 microsecond to complete. Because they are called multiple times, reading out 1 trigger takes ~8 millisecond which explains the 125Hz we're seeing.

Is ~150 us to complete a musb_read()/musb_write() command expected?

Is there any way we could speed up the readout rate of the DRS4 board so that data acquisition through USB2 is closer to our trigger rate of 4kHz?

Any feedback you might have on this topic would be greatly appreciated.

Many thanks,

Aurelien |

|

133

|

Sat Oct 22 00:40:02 2011 |

Stefan Ritt | DRS4 eval board: readout rate |

| Aurelien Bouvier wrote: |

|

Hi,

Our setup uses a DRS4 evaluation board (version 2.0).

Although we trigger the board at a rate of ~4kHz (on channel2), readout through USB2 is only happening at a rate of ~125Hz.

After some investigation, we could pin down that it is due to the time it takes to complete the following commands: musb_write() and musb_read() which both take ~150 microsecond to complete. Because they are called multiple times, reading out 1 trigger takes ~8 millisecond which explains the 125Hz we're seeing.

Is ~150 us to complete a musb_read()/musb_write() command expected?

Is there any way we could speed up the readout rate of the DRS4 board so that data acquisition through USB2 is closer to our trigger rate of 4kHz?

Any feedback you might have on this topic would be greatly appreciated.

Many thanks,

Aurelien

|

With version 4 of the DRSOsc program and a decent computer, you should be able to achieve something close to 500 Hz, but that's the limit. The board is for evaluation purposes of the chip, not for production data acquisition. The main limit comes from USB2, which is limited to ~25 MB/sec. We are in the process of designing a new board with Gigabit Ethernet readout, with which you should be able to get your 4 kHz. But this board will not be ready before spring. There is also a VME board by CAEN in Italy which sits in a VME crate. This board is also much faster than the USB board. Here is the link:

http://www.caen.it/csite/CaenProfList.jsp?parent=13&Type=WOCateg&prodsupp=home

|

|

134

|

Sun Oct 23 23:32:28 2011 |

Hao Huan | Phase Shift for ADC Readout | Dear Dr. Ritt,

In the DRS 4 datasheet it is recommended to sample the analog output of the chip after 8~10 ns of the SRCLK edge for it to stablize and thus a phase shift between SRCLK and the ADC sampling clock is necessary. However in the latest version of the evaluation board firmware the phase-shifted clock was generated but not really used for the ADC interface. Is there any reason for that? |

|

135

|

Mon Oct 24 10:30:15 2011 |

Stefan Ritt | Phase Shift for ADC Readout |

| Hao Huan wrote: |

|

Dear Dr. Ritt,

In the DRS 4 datasheet it is recommended to sample the analog output of the chip after 8~10 ns of the SRCLK edge for it to stablize and thus a phase shift between SRCLK and the ADC sampling clock is necessary. However in the latest version of the evaluation board firmware the phase-shifted clock was generated but not really used for the ADC interface. Is there any reason for that?

|

Good questions. I looked myself in the code and found:

drs_readout_clk <= I_CLK33;

drs_readout_clk_ps <= I_CLK33; -- phase shifted clock for FADC

drs_serial_clk <= I_CLK33;

which is apparently wrong (should be drs_readout_clk_ps <= I_CLK33_PS;) . But apparently the board is working with the unshifted clock. Could be that the PCB traces to the DRS and the ADC have different lengths, and by accident, they have just the right value.

The way to find that out is to keep the ADC clock phase variable (most FPGAs allow a +-5 ns phase adjustment inside their clock blocks), and then try different values. If the phase shift is wrong, you will see spikes every 32 samples in the readout. The spikes are always there (from some internal switching of bus segments), and you can see them with a differential probe at the DRS output. The ADC phase must then be made such that the sampling point of the ADC comes after that spike, just at the end of the settling time, barely before the next analog value shows up at the DRS output. This is a bit tricky and can be made best just by trying out different values. |

|

136

|

Mon Oct 31 09:15:02 2011 |

Zhongwei Du | How to link PMT | I want to measure the signal from PMT . But it is a current signal, should i just put a series resistance, or use a amplifier to convert it to voltage signal before drs4?

Can you give me some advice ? |

|

137

|

Tue Nov 1 11:07:02 2011 |

Stefan Ritt | How to link PMT |

| Zhongwei Du wrote: |

|

I want to measure the signal from PMT . But it is a current signal, should i just put a series resistance, or use a amplifier to convert it to voltage signal before drs4?

Can you give me some advice ?

|

The evaluation board has a 50 Ohm termination resistor, which already converts your current into a voltage signal. If the resulting signal is too low (<20 mV) you can put in an amplifier or raise the HV of your PMT (inside the valid range given by its datasheet of course).

- Stefan |

|

138

|

Fri Dec 9 17:45:48 2011 |

Michael B�ker | Fixes to DOScreen.cpp for recent built on linux | > I was just building version 3.1.0 and ran into some problems in DOScreen.cpp. Basically the conversions from

> char* to wxString were generating "ambiguous overload" errors (in gcc 4.4.3, wx-2.8)

>

> The simple fix is given in the following diff output.

Today, I ran into the same problem and was happy to find your fix. I've incorporated it into a unified diff file,

that can easily be applied with the patch program by saving it into a file ('drsosc-3.1.0-wxfix.patch', say), and

in the drs-3.1.0 directory running:

patch -1 < drsosc-3.1.0-wxfix.patch

This is the file:

--- src/DOScreen.cpp.orig 2011-12-09 15:49:48.682201902 +0100

+++ src/DOScreen.cpp 2011-12-09 15:51:45.666000111 +0100

@@ -234,7 +234,7 @@ void DOScreen::DrawWaveform(wxDC& dc, wx

// display optional debug messages

if (*m_frame->GetOsci()->GetDebugMsg()) {

- wxst = m_frame->GetOsci()->GetDebugMsg();

+ wxst = wxString(m_frame->GetOsci()->GetDebugMsg(),wxConvUTF8);

dc.SetPen(wxPen(*wxLIGHT_GREY, 1, wxSOLID));

dc.SetBrush(*wxGREEN);

dc.SetTextForeground(*wxBLACK);

@@ -243,7 +243,7 @@ void DOScreen::DrawWaveform(wxDC& dc, wx

dc.DrawText(wxst, m_x1+4, m_y1+2);

}

if (m_debugMsg[0]) {

- wxst = m_debugMsg;

+ wxst = wxString(m_debugMsg,wxConvUTF8);

dc.SetPen(wxPen(*wxLIGHT_GREY, 1, wxSOLID));

dc.SetBrush(*wxGREEN);

dc.SetTextForeground(*wxBLACK);

@@ -474,9 +474,9 @@ void DOScreen::DrawWaveform(wxDC& dc, wx

if (m_osci->GetNumberOfBoards() && m_osci->IsIdle()) {

dc.SetTextForeground(*wxGREEN);

if (m_osci->GetTriggerMode() == TM_AUTO)

- wxst = "AUTO";

+ wxst = wxString("AUTO",wxConvUTF8);

else

- wxst = "TRIG?";

+ wxst = wxString("TRIG?",wxConvUTF8);

dc.GetTextExtent(wxst, &w, &h);

dc.DrawText(wxst, m_x2 - w - 2, m_y1 + 1);

} |

|

139

|

Mon Dec 12 16:43:04 2011 |

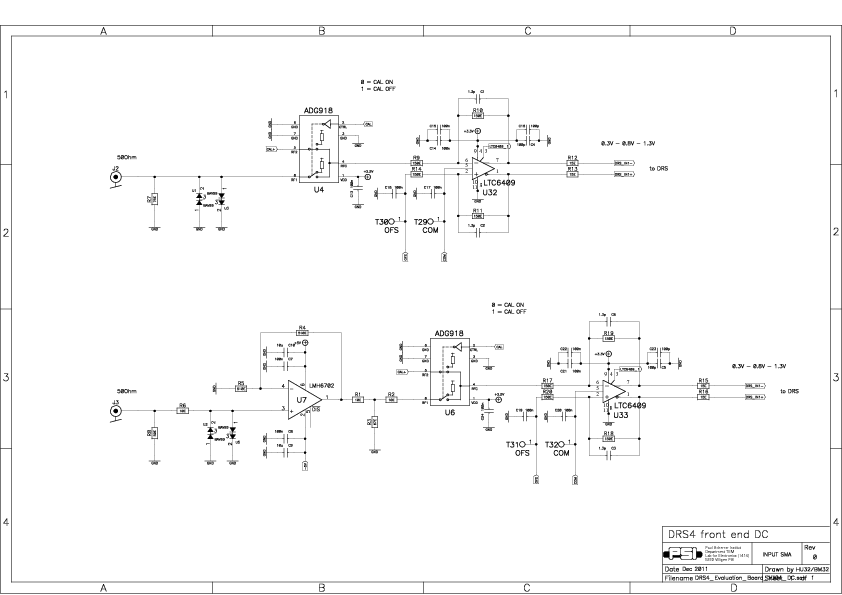

Stefan Ritt | DC coupled DRS4 input stage | In the attachement you will find a working DC-coupled input stage to the DRS4 chip. The bandwidth of this design is about 700 MHz, the gain is 1.

The upper version does not have an additional input buffer. This is not a very "clean" design, since the differential driver has an input impedance of 150 Ohm, which together with the 75 Ohm termination resistor gives about 50 Ohm termination.

The lover version has an additional input buffer, which nicely decouples the input from the differential driver, so a proper 50 Ohm termination can be used at the cost of additional power for that buffer.

The COM common mode voltage and the OFS voltage have to be set according to the required input range, so that ranges such as 0V...1V, -0.5V...+0.5V, -1V...0V can be used. The COM voltage can be high impedance (simple resistor divider), while the OFS voltage needs to be low impedance (fast active buffer). The analog switch ADG918 can be used to digitize a precise calibration voltage CAL+, which can then be used for precise gain calibration of the DRS4 sampling cells. |

| Attachment 1: DRS4_front_end_DC.pdf

|

|

|

140

|

Wed Dec 14 00:44:37 2011 |

Hao Huan | Synchronization Delay in the Firmware for 8051 Controller | Hi Stefan,

I have a question regarding the DRS 4 evaluation board firmware for the 8051 controller embedded in the CY7C68013 USB chip: on the board the controller is running at 12 MHz and the FIFO interface of the USB chip is running at 30 MHz, so the number of delay cycles for synchronization as defined in fx2sdly.h should be (3*12000+5*30000-1)/(2*30000)=3, but the actual number used in drs_eval.c is (3*12000+5*48000-1)/(2*48000)=2, so there is a mismatch between the IFCLK frequency used in this calculation and the actual IFCLK frequency configured. Am I misunderstanding something or is there an explanation for that?

Thanks,

Hao Huan |

|

141

|

Wed Dec 14 08:55:29 2011 |

Stefan Ritt | Synchronization Delay in the Firmware for 8051 Controller |

| Hao Huan wrote: |

|

Hi Stefan,

I have a question regarding the DRS 4 evaluation board firmware for the 8051 controller embedded in the CY7C68013 USB chip: on the board the controller is running at 12 MHz and the FIFO interface of the USB chip is running at 30 MHz, so the number of delay cycles for synchronization as defined in fx2sdly.h should be (3*12000+5*30000-1)/(2*30000)=3, but the actual number used in drs_eval.c is (3*12000+5*48000-1)/(2*48000)=2, so there is a mismatch between the IFCLK frequency used in this calculation and the actual IFCLK frequency configured. Am I misunderstanding something or is there an explanation for that?

Thanks,

Hao Huan

|

You are right. The SYNCDELAY should contain three wait cycles. I kind of remember that this delay is not very critical. That might be the reason why the system works even with the wrong delay reliably. |

|

142

|

Thu Jan 19 23:26:26 2012 |

Heejong Kim | drs_exam.cpp for evaluation board version 4 | Hello,

I'm using DRS4 evaluation board version4 in Linux (Scientific Linux 5).

Version4 software (drs-4.0.0) was installed without any troubles.

The oscilloscope interfrace program (drsosc) is working fine with version4 software.

But when I tried drs_exam program, it doesn't work as expected.

(500 mV positive (width 50ns) pulse is connected to Ch#1).

It keeps waiting trigger in the first event.

In the previous version (board/software drs-3.0.0), drs_exam program worked well.

I'm wondering if anybody is using drs_exam with V4 evaluation board.

Any comments/help would be welcomed.

Thanks,

Heejong |

|

143

|

Fri Jan 20 08:09:38 2012 |

Stefan Ritt | drs_exam.cpp for evaluation board version 4 |

| Heejong Kim wrote: |

|

Hello,

I'm using DRS4 evaluation board version4 in Linux (Scientific Linux 5).

Version4 software (drs-4.0.0) was installed without any troubles.

The oscilloscope interfrace program (drsosc) is working fine with version4 software.

But when I tried drs_exam program, it doesn't work as expected.

(500 mV positive (width 50ns) pulse is connected to Ch#1).

It keeps waiting trigger in the first event.

In the previous version (board/software drs-3.0.0), drs_exam program worked well.

I'm wondering if anybody is using drs_exam with V4 evaluation board.

|

The issue is that the V4 board has new trigger capabilities (such as coincidences between two channels) which require a slightly different configuration. Here it the new code:

/* use following lines to enable hardware trigger on CH1 at 50 mV positive edge */

if (b->GetBoardType() == 8) { // Evaluaiton Board V4

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

} else { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

b->SetTriggerSource(0); // use CH1 as source

}

The complete file is attached. Please try again with the new code. Probably next week I will make a new software release (including a Mac version of all programs) which will contain the new code. Sorry for any inconvenience.

Best regards,

Stefan

|

| Attachment 1: drs_exam.cpp

|

/********************************************************************\

Name: drs_exam.cpp

Created by: Stefan Ritt

Contents: Simple example application to read out a DRS4

evaluation board

$Id: drs_exam.cpp 18834 2012-01-05 12:38:20Z ritt $

\********************************************************************/

#include <math.h>

#ifdef _MSC_VER

#include <windows.h>

#elif defined(OS_LINUX)

#define O_BINARY 0

#include <unistd.h>

#include <ctype.h>

#include <sys/ioctl.h>

#include <errno.h>

#define DIR_SEPARATOR '/'

#endif

#include <stdio.h>

#include <string.h>

#include <stdlib.h>

#include "strlcpy.h"

#include "DRS.h"

/*------------------------------------------------------------------*/

int main()

{

int i, j, nBoards;

DRS *drs;

DRSBoard *b;

float time_array[1024];

float wave_array[8][1024];

FILE *f;

/* do initial scan */

drs = new DRS();

/* show any found board(s) */

for (i=0 ; i<drs->GetNumberOfBoards() ; i++) {

b = drs->GetBoard(i);

printf("Found DRS4 evaluation board, serial #%d, firmware revision %d\n",

b->GetBoardSerialNumber(), b->GetFirmwareVersion());

}

/* exit if no board found */

nBoards = drs->GetNumberOfBoards();

if (nBoards == 0) {

printf("No DRS4 evaluation board found\n");

return 0;

}

/* continue working with first board only */

b = drs->GetBoard(0);

/* initialize board */

b->Init();

/* set sampling frequency */

b->SetFrequency(5, true);

/* enable transparent mode needed for analog trigger */

b->SetTranspMode(1);

/* set input range to -0.5V ... +0.5V */

b->SetInputRange(0);

/* use following line to set range to 0..1V */

//b->SetInputRange(0.5);

/* use following lines to enable hardware trigger on CH1 at 50 mV positive edge */

if (b->GetBoardType() == 8) { // Evaluaiton Board V4

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

} else { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

b->SetTriggerSource(0); // use CH1 as source

}

b->SetTriggerLevel(0.05, false); // 0.05 V, positive edge

b->SetTriggerDelayNs(0); // zero ns trigger delay

/* open file to save waveforms */

f = fopen("data.txt", "w");

if (f == NULL) {

perror("ERROR: Cannot open file \"data.txt\"");

return 1;

}

/* repeat ten times */

for (j=0 ; j<10 ; j++) {

/* start board (activate domino wave) */

b->StartDomino();

/* wait for trigger */

printf("Waiting for trigger...");

fflush(stdout);

while (b->IsBusy());

/* read all waveforms */

b->TransferWaves(0, 8);

/* read time (X) array in ns */

b->GetTime(0, b->GetTriggerCell(0), time_array);

/* decode waveform (Y) array first channel in mV */

b->GetWave(0, 0, wave_array[0]);

/* decode waveform (Y) array second channel in mV

Note: On the evaluation board input #1 is connected to channel 0 and 1 of

the DRS chip, input #2 is connected to channel 2 and 3 and so on. So to

get the input #2 we have to read DRS channel #2, not #1 */

b->GetWave(0, 2, wave_array[1]);

/* Save waveform: X=time_array[i], Yn=wave_array[n][i] */

fprintf(f, "Event #%d: t y1 y2\n", j);

for (i=0 ; i<1024 ; i++)

//fprintf(f, "%1.2f %1.2f %1.2f\n", time_array[i], wave_array[0][i], wave_array[1][i]);

fprintf(f, "%5.2f %6.2f\n", time_array[i], wave_array[0][i]);

/* print some progress indication */

printf("\rEvent #%d read successfully\n", j);

}

fclose(f);

/* delete DRS object -> close USB connection */

delete drs;

}

|

|

144

|

Fri Jan 20 23:50:39 2012 |

Heejong Kim | drs_exam.cpp for evaluation board version 4 |

| Stefan Ritt wrote: |

|

| Heejong Kim wrote: |

|

Hello,

I'm using DRS4 evaluation board version4 in Linux (Scientific Linux 5).

Version4 software (drs-4.0.0) was installed without any troubles.

The oscilloscope interfrace program (drsosc) is working fine with version4 software.

But when I tried drs_exam program, it doesn't work as expected.

(500 mV positive (width 50ns) pulse is connected to Ch#1).

It keeps waiting trigger in the first event.

In the previous version (board/software drs-3.0.0), drs_exam program worked well.

I'm wondering if anybody is using drs_exam with V4 evaluation board.

|

The issue is that the V4 board has new trigger capabilities (such as coincidences between two channels) which require a slightly different configuration. Here it the new code:

/* use following lines to enable hardware trigger on CH1 at 50 mV positive edge */

if (b->GetBoardType() == 8) { // Evaluaiton Board V4

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

} else { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

b->SetTriggerSource(0); // use CH1 as source

}

The complete file is attached. Please try again with the new code. Probably next week I will make a new software release (including a Mac version of all programs) which will contain the new code. Sorry for any inconvenience.

Best regards,

Stefan

|

Hello Stefan,

Thanks for your prompt reply.

drs_exam is working now after modification as above.

By some trials, I found that external trigger is possible by 'b->EnableTrigger(1,0); b->SetTriggerSource(1<<4);'

Best,

Heejong

|

|

145

|

Thu Jan 26 09:12:03 2012 |

Ravindra Raghunath Shinde | DRS4 Rev2.0 for analog pulse counting | Hello,

We are using DRS4 Rev.2.0 board.

We want to measure number of pulses generated by charge particle detector. These negative going analog pulses are very fast having rise time about 2nS.

We want keep threshold level to -20mV. We expected pulse rate to be about 100 to 200 Hz.

I need help to implement this in current DRS board with dead time free operation.

|

|

146

|

Thu Jan 26 09:15:42 2012 |

Stefan Ritt | DRS4 Rev2.0 for analog pulse counting |

| Ravindra Raghunath Shinde wrote: |

|

Hello,

We are using DRS4 Rev.2.0 board.

We want to measure number of pulses generated by charge particle detector. These negative going analog pulses are very fast having rise time about 2nS.

We want keep threshold level to -20mV. We expected pulse rate to be about 100 to 200 Hz.

I need help to implement this in current DRS board with dead time free operation.

|

If you just want to count pulses, you do not need a DRS board. Just use a discriminator and a counter, that's much simpler. The DRS board is not dead time free. |

|

147

|

Thu Jan 26 09:44:34 2012 |

Ravindra Raghunath Shinde | DRS4 Rev2.0 for analog pulse counting |

| Stefan Ritt wrote: |

|

| Ravindra Raghunath Shinde wrote: |

|

Hello,

We are using DRS4 Rev.2.0 board.

We want to measure number of pulses generated by charge particle detector. These negative going analog pulses are very fast having rise time about 2nS.

We want keep threshold level to -20mV. We expected pulse rate to be about 100 to 200 Hz.

I need help to implement this in current DRS board with dead time free operation.

|

If you just want to count pulses, you do not need a DRS board. Just use a discriminator and a counter, that's much simpler. The DRS board is not dead time free.

|

Thanks for your prompt reply.

Along with pulse rate we also want see pulse shape as well as charge measurements. That is why we are exploring this option with our existing DRS Set-up.

|

|

148

|

Thu Jan 26 09:49:38 2012 |

Stefan Ritt | DRS4 Rev2.0 for analog pulse counting |

| Ravindra Raghunath Shinde wrote: |

|

| Stefan Ritt wrote: |

|

| Ravindra Raghunath Shinde wrote: |

|

Hello,

We are using DRS4 Rev.2.0 board.

We want to measure number of pulses generated by charge particle detector. These negative going analog pulses are very fast having rise time about 2nS.

We want keep threshold level to -20mV. We expected pulse rate to be about 100 to 200 Hz.

I need help to implement this in current DRS board with dead time free operation.

|

If you just want to count pulses, you do not need a DRS board. Just use a discriminator and a counter, that's much simpler. The DRS board is not dead time free.

|

Thanks for your prompt reply.

Along with pulse rate we also want see pulse shape as well as charge measurements. That is why we are exploring this option with our existing DRS Set-up.

|

I understand that. But still the board has some dead time which is dominated by the USB data transfer speed.

There is a way to perform the counting dead time free, but that requires the V4 board, which has a hardware comparator on all four channels (The V2 board has only one comparator and a multiplexer). The output of these comparators go directly to the FPGA, which can then trigger on these signals. In principle one could implement a hardware counter in the FPGA, which works practically dead time free. But this requires a new firmware which has to be written. Either you do it yourself using the Xilinx development tools, or you wait until I find some time to implement this, which could take a couple of weeks or even months.

Best regards,

Stefan |

|