| ID |

Date |

Author |

Subject |

|

552

|

Fri Oct 28 15:51:59 2016 |

Stefan Ritt | Problems with DRS command line | No, I absolutely have no idea. Both DRSOsc and drscl use exaclty the same code to access USB.

Stefan

| Simon Mendisch wrote: |

that means, I am the second one experiencing this problem. To be more specific, the "No DRS Board found" problem is only present at one machine running Win7x64.

DRSOsc, of course not running simultaneously works just fine. Only drscl shows this behavior. Upgrading to a newer software version or a re-installation of the old one didn't solve the issue.

On other Win7x64 machines everything works fine, so I am pretty sure the problem is on this specific machine. Do you have any idea what could be the cause of this behavior?

|

|

|

910

|

Fri Dec 20 20:35:31 2024 |

Matias Henriquez | Problem with C++ script to use DRS4 evaluation board. Not taking data. | Hello,

I need to write a script in C++ to take data using the DRS4 evaluation board v4. For that, I used the drs_exam.cpp example as a reference. This is my code (see attachement 2), which is very similar to the provided example, however the difference is that I need to trigger on CH1 OR CH2. In the next version I will need to trigger with an OR in all channels.

The problem is, my code gets stuck in waiting for trigger or only 1 event occurs (event 0). I read that event and it doesn't even go above 30mV, which was the threshold I set. There are some questions I have:

- Why Transparent mode is activated for Hardware Trigger?

- Why EnableTCal is activated? is the drs4_exam example based acquires the 100MHz reference just for the sake of the example? or is just a time calibration routine?

- Can someone explain the function EnableTrigger(flag1,flag2) in boardType 8? it si not clear to me how the trigger is enabled.

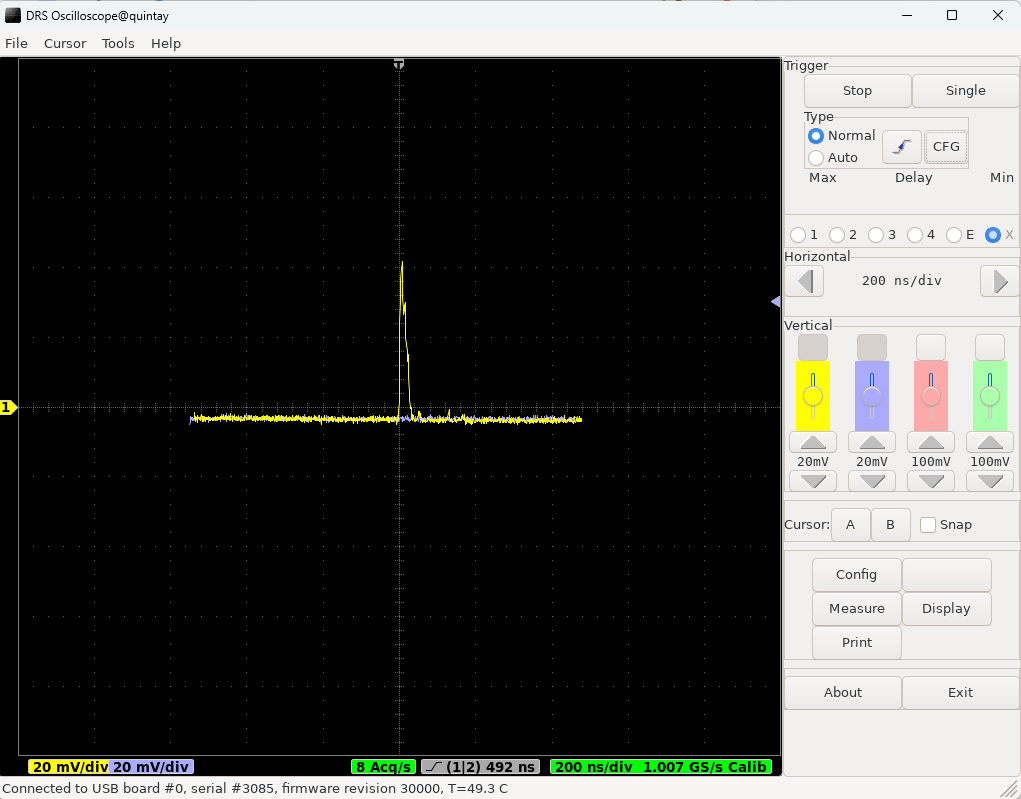

- To check that my input signals are correct, I run the drsosc application and I can see the signals with no problem (see attachement 1). However I noticed that I had to configure the trigger delay in the drsosc application, and I don't do that in my c++ code. I will try that later.

- How do I perform voltage calibration and time calibration using the c++ functions?

Thank you so much for your help.

|

| Attachment 1: 1.png

|

|

| Attachment 2: drs_test.cpp

|

/********************************************************************\

Name: drs_exam.cpp

Created by: Stefan Ritt

Contents: Simple example application to read out a DRS4

evaluation board

$Id: drs_exam.cpp 21308 2014-04-11 14:50:16Z ritt $

\********************************************************************/

#include <math.h>

#ifdef _MSC_VER

#include <windows.h>

#elif defined(OS_LINUX)

#define O_BINARY 0

#include <unistd.h>

#include <ctype.h>

#include <sys/ioctl.h>

#include <errno.h>

#define DIR_SEPARATOR '/'

#endif

#include <stdio.h>

#include <string.h>

#include <stdlib.h>

#include "strlcpy.h"

#include "DRS.h"

/*------------------------------------------------------------------*/

int main()

{

int i, j, nBoards;

DRS *drs;

DRSBoard *b;

float time_array[8][1024];

float wave_array[8][1024];

FILE *f;

double domino_freq = 2; //Domino Ring Frequency = 2GHz

double trigger_level_ch1 = 0.03; // Trigger level for channel 1

double trigger_level_ch2 = 0.03; // Trigger level for channel 2

//double trigger_level_ch3 = 0.01; // Trigger level for channel 3

//double trigger_level_ch4 = 0.01; // Trigger level for channel 4

int trigger_source_reg = (1<<0) + (1<<1);

//int trigger_source_reg = (1<<0) + (1<<1) + (1<<2) + (1<<3);

/* do initial scan */

drs = new DRS();

/* show any found board(s) */

for (i=0 ; i<drs->GetNumberOfBoards() ; i++) {

b = drs->GetBoard(i);

printf("Found DRS4 evaluation board, serial #%d, firmware revision %d\n",

b->GetBoardSerialNumber(), b->GetFirmwareVersion());

}

/* exit if no board found */

nBoards = drs->GetNumberOfBoards();

if (nBoards == 0) {

printf("No DRS4 evaluation board found\n");

return 0;

}

/* continue working with first board only */

b = drs->GetBoard(0);

/* initialize board */

b->Init();

/* set sampling frequency */

b->SetFrequency(domino_freq, true);

/* enable transparent mode needed for analog trigger */

b->SetTranspMode(0);

/* set input range to -0.5V ... +0.5V */

//b->SetInputRange(0.5);

/* use following line to set range to 0..1V */

b->SetInputRange(0.45);

/* use following line to turn on the internal 100 MHz clock connected to all channels */

//b->EnableTcal(1);

/* use following lines to enable hardware trigger on */

if (b->GetBoardType() >= 8) { // Evaluaiton Board V4&5

b->EnableTrigger(1, 0); // enable hardware trigger

//b->SetTriggerSource(1<<0);

} else if (b->GetBoardType() == 7) { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

//b->SetTriggerSource(0);

}

//b->SetTriggerLevel(0.05); // 0.05 V

b->SetTriggerPolarity(false); // positive edge

/* use following lines to set individual trigger elvels */

b->SetIndividualTriggerLevel(1, trigger_level_ch1);

b->SetIndividualTriggerLevel(2, trigger_level_ch2);

//b->SetIndividualTriggerLevel(3, trigger_level_ch3);

//b->SetIndividualTriggerLevel(4, trigger_level_ch4);

//Set Trigger Configuration

// OR Bit0 = CH1, Bit1 = CH2, Bit2 = CH3, Bit3 = CH4, Bit4 = EXT

// AND Bit8 = CH1, Bit9 = CH2, Bit10 = CH3, Bit11 = CH4, Bit12 = EXT

// TRANSP Bit15

b->SetTriggerSource(trigger_source_reg);

b->SetTriggerDelayNs(0); // zero ns trigger delay

/* use following lines to enable the external trigger */

//if (b->GetBoardType() == 8) { // Evaluaiton Board V4

// b->EnableTrigger(1, 0); // enable hardware trigger

// b->SetTriggerSource(1<<4); // set external trigger as source

//} else { // Evaluation Board V3

// b->EnableTrigger(1, 0); // lemo on, analog trigger off

// }

/* open file to save waveforms */

f = fopen("data.txt", "w");

if (f == NULL) {

perror("ERROR: Cannot open file \"data.txt\"");

return 1;

}

/* repeat ten times */

for (j=0 ; j<10 ; j++) {

/* start board (activate domino wave) */

b->StartDomino();

/* wait for trigger */

printf("Waiting for trigger...");

fflush(stdout);

while (b->IsBusy());

/* read all waveforms */

b->TransferWaves(0, 8);

/* read time (X) array of first channel in ns */

b->GetTime(0, 0, b->GetTriggerCell(0), time_array[0]);

/* decode waveform (Y) array of first channel in mV */

b->GetWave(0, 0, wave_array[0]);

/* read time (X) array of second channel in ns

Note: On the evaluation board input #1 is connected to channel 0 and 1 of

the DRS chip, input #2 is connected to channel 2 and 3 and so on. So to

get the input #2 we have to read DRS channel #2, not #1. */

b->GetTime(0, 2, b->GetTriggerCell(0), time_array[1]);

/* decode waveform (Y) array of second channel in mV */

b->GetWave(0, 2, wave_array[1]);

/* Save waveform: X=time_array[i], Yn=wave_array[n][i] */

fprintf(f, "Event #%d ----------------------\n t1[ns] u1[mV] t2[ns] u2[mV]\n", j);

for (i=0 ; i<1024 ; i++)

fprintf(f, "%7.3f %7.1f %7.3f %7.1f\n", time_array[0][i], wave_array[0][i], time_array[1][i], wave_array[1][i]);

/* print some progress indication */

printf("\rEvent #%d read successfully\n", j);

}

fclose(f);

/* delete DRS object -> close USB connection */

delete drs;

}

|

|

912

|

Fri Dec 27 22:04:48 2024 |

Matias Henriquez | Problem with C++ script to use DRS4 evaluation board. Not taking data. | Hello, some updates:

4. I was able to capture correct waveforms using c++ code. I needed to use the function SetTriggerDelayNs() to properly capture my waveforms.

5. I noticed that the drsosc program source code uses the functions: CalibrateVolt() and CalibrateTiming() for performing calibration. For these to work, is it necessary to use EnableAcal() and EnableTcal() functions right?

I'd appreciate if you can still give some insights about 1,2 and 3. Thank you!

| Matias Henriquez wrote: |

|

Hello,

I need to write a script in C++ to take data using the DRS4 evaluation board v4. For that, I used the drs_exam.cpp example as a reference. This is my code (see attachement 2), which is very similar to the provided example, however the difference is that I need to trigger on CH1 OR CH2. In the next version I will need to trigger with an OR in all channels.

The problem is, my code gets stuck in waiting for trigger or only 1 event occurs (event 0). I read that event and it doesn't even go above 30mV, which was the threshold I set. There are some questions I have:

- Why Transparent mode is activated for Hardware Trigger?

- Why EnableTCal is activated? is the drs4_exam example based acquires the 100MHz reference just for the sake of the example? or is just a time calibration routine?

- Can someone explain the function EnableTrigger(flag1,flag2) in boardType 8? it si not clear to me how the trigger is enabled.

- To check that my input signals are correct, I run the drsosc application and I can see the signals with no problem (see attachement 1). However I noticed that I had to configure the trigger delay in the drsosc application, and I don't do that in my c++ code. I will try that later.

- How do I perform voltage calibration and time calibration using the c++ functions?

Thank you so much for your help.

|

|

|

913

|

Mon Jan 6 12:52:23 2025 |

Stefan Ritt | Problem with C++ script to use DRS4 evaluation board. Not taking data. | 1. Transparent mode is not needed for the hardware trigger, no idea why the code is there. You can probably remove it.

2. EnableTCal is only for the sake of having some waveforms at the input. Indeed you have to disable it to sample real signals.

3. EnableTrigger() is there to enable the hardware trigger. The flag2 is ther for historical reasons (used in older versions of the board).

4. You figured that out already yourself.

5. The functions CalibrateVolt() and CalibrateTiming() are the ones which get called if you click on volt and time calibration in the DRSOsc application. The calibration is store on the evaluation board, so you do not have to call them in your program.

| Matias Henriquez wrote: |

|

Hello, some updates:

4. I was able to capture correct waveforms using c++ code. I needed to use the function SetTriggerDelayNs() to properly capture my waveforms.

5. I noticed that the drsosc program source code uses the functions: CalibrateVolt() and CalibrateTiming() for performing calibration. For these to work, is it necessary to use EnableAcal() and EnableTcal() functions right?

I'd appreciate if you can still give some insights about 1,2 and 3. Thank you!

| Matias Henriquez wrote: |

|

Hello,

I need to write a script in C++ to take data using the DRS4 evaluation board v4. For that, I used the drs_exam.cpp example as a reference. This is my code (see attachement 2), which is very similar to the provided example, however the difference is that I need to trigger on CH1 OR CH2. In the next version I will need to trigger with an OR in all channels.

The problem is, my code gets stuck in waiting for trigger or only 1 event occurs (event 0). I read that event and it doesn't even go above 30mV, which was the threshold I set. There are some questions I have:

- Why Transparent mode is activated for Hardware Trigger?

- Why EnableTCal is activated? is the drs4_exam example based acquires the 100MHz reference just for the sake of the example? or is just a time calibration routine?

- Can someone explain the function EnableTrigger(flag1,flag2) in boardType 8? it si not clear to me how the trigger is enabled.

- To check that my input signals are correct, I run the drsosc application and I can see the signals with no problem (see attachement 1). However I noticed that I had to configure the trigger delay in the drsosc application, and I don't do that in my c++ code. I will try that later.

- How do I perform voltage calibration and time calibration using the c++ functions?

Thank you so much for your help.

|

|

|

|

35

|

Mon Feb 15 19:43:34 2010 |

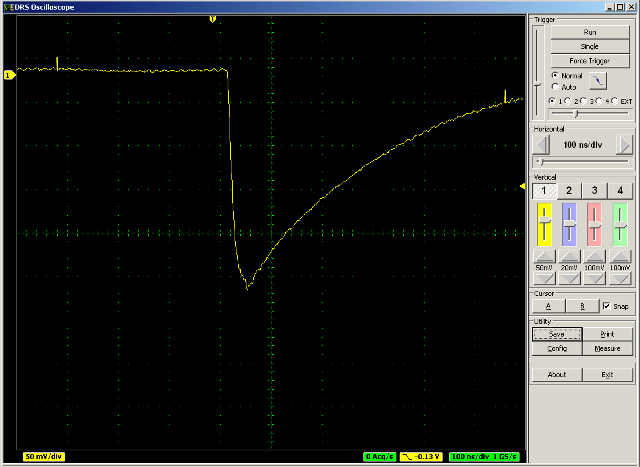

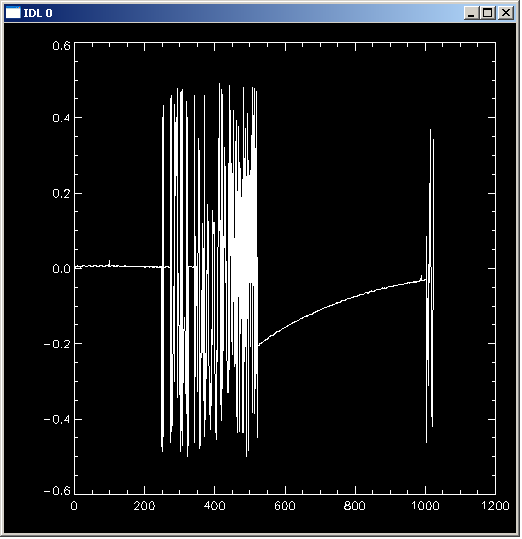

Ron Grazioso | Problem reading oscilloscope binary waveform output | I have saved some waveforms using the oscilloscope application in both binary and xml. I can see that the xml file gives me proper data values but when I try to read the binary file using IDL, it does not seem correct. This is a screen shot of the pulse I saved:

But when I open the binary file in IDL using:

data = uintarr(1024) ;unsigned integer array

readu,lun1,data

free_lun,lun1

close,lun1

;Convert bits to Volts

data=data*0.000015259-0.5

window,0,xs=512,ys=512

plot,data[*]

I get: I get:

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

Thanks, Ron

|

|

36

|

Tue Feb 16 09:38:59 2010 |

Stefan Ritt | Problem reading oscilloscope binary waveform output |

| Ron Grazioso wrote: |

|

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

|

Yes, but you have to recompile the oscilloscope application. Find following line in the source file DOFrame.cpp:

m_WFfd = open(filename.char_str(), O_RDWR | O_CREAT | O_TRUNC | O_TEXT, 0644);

and replace it with

m_WFfd = open(filename.char_str(), O_RDWR | O_CREAT | O_TRUNC | O_BINARY, 0644);

that fixes the problem. To compile the program, you need MS Visual C++ and you have to install the vxWidgets library. Let me know if you have any problem with that.

Anyhow I plan a major software update soon (weeks), which not only fixes this problem, but also reduces the noise considerably by doing a kind of two-fold calibration.

- Stefan |

|

170

|

Mon Jul 9 14:14:48 2012 |

Ivan Petrov | Problem compiling drs_exam.cpp on windows | Hello again. I have not got evaluation board yet, but already faced some difficulties:) I'm trying to compile drs_exam.cpp on Windows 7 using dev-c++ with imagelib-2 and WxWindows 2.4.2 DevPaks installed, but nothing works. Compile log is attached. Honestly, I'm not very familiar with c++, so any suggestions will be helpful. Thank you. |

| Attachment 1: compile_log.txt

|

Compiler: Default compiler

Building Makefile: "G:\devcpp\Makefile.win"

Executing make...

make.exe -f "G:\devcpp\Makefile.win" all

g++.exe -c AboutDialog.cpp -o AboutDialog.o -I"C:/Dev-Cpp/lib/gcc/mingw32/3.4.2/include" -I"C:/Dev-Cpp/include/c++/3.4.2/backward" -I"C:/Dev-Cpp/include/c++/3.4.2/mingw32" -I"C:/Dev-Cpp/include/c++/3.4.2" -I"C:/Dev-Cpp/include"

In file included from C:/Dev-Cpp/include/wx/wx.h:15,

from DRSOscInc.h:7,

from AboutDialog.cpp:7:

C:/Dev-Cpp/include/wx/defs.h:179: error: redeclaration of C++ built-in type `int'

In file included from C:/Dev-Cpp/include/wx/memory.h:20,

from C:/Dev-Cpp/include/wx/object.h:25,

from C:/Dev-Cpp/include/wx/wx.h:16,

from DRSOscInc.h:7,

from AboutDialog.cpp:7:

C:/Dev-Cpp/include/wx/string.h:160:4: #error "Please define string case-insensitive compare for your OS/compiler"

In file included from DRSOscInc.h:12,

from AboutDialog.cpp:7:

DRSOsc.h:38:26: wx/hyperlink.h: No such file or directory

In file included from DRSOscInc.h:12,

from AboutDialog.cpp:7:

DRSOsc.h:532: error: ISO C++ forbids declaration of `wxHyperlinkCtrl' with no type

DRSOsc.h:532: error: expected `;' before '*' token

make.exe: *** [AboutDialog.o] Error 1

Execution terminated

|

|

171

|

Tue Jul 10 13:15:00 2012 |

Stefan Ritt | Problem compiling drs_exam.cpp on windows |

| Ivan Petrov wrote: |

|

Hello again. I have not got evaluation board yet, but already faced some difficulties:) I'm trying to compile drs_exam.cpp on Windows 7 using dev-c++ with imagelib-2 and WxWindows 2.4.2 DevPaks installed, but nothing works. Compile log is attached. Honestly, I'm not very familiar with c++, so any suggestions will be helpful. Thank you.

|

I have no experience with dev-c++, so I cannot be of help here. The supported systems are Linux and Windows with MS Visual C++. But it looks like the problems are related to compiling wxWidgets, which actually you do NOT need for drs_exam.cpp. The wxWidgets library is only needed for the DRSOsc application. If you want to compile it anyhow, first learn how to compile standard WxWidgets applications from

http://www.wxwidgets.org/docs/tutorials/devcpp.htm

Best regards,

Stefan |

|

172

|

Wed Jul 11 10:04:51 2012 |

Ivan Petrov | Problem compiling drs_exam.cpp on windows |

| Stefan Ritt wrote: |

|

| Ivan Petrov wrote: |

|

Hello again. I have not got evaluation board yet, but already faced some difficulties:) I'm trying to compile drs_exam.cpp on Windows 7 using dev-c++ with imagelib-2 and WxWindows 2.4.2 DevPaks installed, but nothing works. Compile log is attached. Honestly, I'm not very familiar with c++, so any suggestions will be helpful. Thank you.

|

I have no experience with dev-c++, so I cannot be of help here. The supported systems are Linux and Windows with MS Visual C++. But it looks like the problems are related to compiling wxWidgets, which actually you do NOT need for drs_exam.cpp. The wxWidgets library is only needed for the DRSOsc application. If you want to compile it anyhow, first learn how to compile standard WxWidgets applications from

http://www.wxwidgets.org/docs/tutorials/devcpp.htm

Best regards,

Stefan

|

Ok, this was my bad, I added some unnecessary files to project. Drs_exam compiles well with ms vc++. Thanks! |

|

523

|

Thu May 12 05:18:47 2016 |

Yu | Problem For Software Download | Hi

I can't download the software for windows on this website 'www.psi.ch/drs/software-download', there is some mistake when i click on download.

If convenient, can you send the software Version 5.0.5 for windows to me? My E-mail address is 'yuhaiyang421@163.com'. Thank you!

Best Regards

Yu |

|

524

|

Thu May 12 08:16:41 2016 |

Stefan Ritt | Problem For Software Download | Can you tell me (screendump) what is the problem on the web site https://www.psi.ch/drs/software-download ? It should redirect you to

https://www.dropbox.com/sh/qul1cgtm4x7zx13/AADKQ-qGQGdAHPu6OR3vTNY0a?dl=0

for the Windows download.

I cannot send executables via email, that won't go though any spam filter.

Stefan

| Yu wrote: |

|

Hi

I can't download the software for windows on this website 'www.psi.ch/drs/software-download', there is some mistake when i click on download.

If convenient, can you send the software Version 5.0.5 for windows to me? My E-mail address is 'yuhaiyang421@163.com'. Thank you!

Best Regards

Yu

|

|

|

10

|

Tue Jul 7 16:39:57 2009 |

Stefan Ritt | Power up problem and remedy | Maybe some of you have experienced that the DRS4 chip can get pretty hot after power up. After it's initialized the first time, the power consumption goes back to normal. I finally found the cause of this problem and have a remedy. Here is the new paragraph from the updated data sheet:

During power-up, care has to be taken that the DENABLE and DWRITE signals are low. If not, the domino wave can get started before the power supply voltages are stable, which brings the DRS4 chip into a state where it draws a considerable amount of current and heats up significantly. This can be problematic if the signals are directly generated by a FPGA, since most FPGAs have internal pull-up resistors which get activated during the configuration phase of the FPGA. In such a case, the DENABLE and DWRITE signals should be connected to GND with a pull down resistor. This resistor should be much smaller than the FPGA pull-up resistor in order to keep the signals close to GND during the FPGA configuration. A typical value is 4.7 kOhm.

The attached schematics shows the location of the two required resistors. |

| Attachment 1: typical_mode.gif

|

|

|

566

|

Wed Nov 23 08:17:23 2016 |

Abhishek Rajput | Potential Incorrect Timing Calibration for DRS4 Data | Hello,

I was running through a particular binary file containing data taken on all 4 channels of the DRS4 and printing out the value of the first time sample for each channel (per event). While doing so, I noticed that some of these times were negative. For this dataset, channel 1 was chosen as the reference channel (which is the default setup in Stefan's DRS4 macro). From my understanding, the calibration procedure delineated in the DRS4 manual and shown in the code below is supposed to sync the timing of each channel relative to sample 0. However, this does not appear to be the case for when I print out the time value of the first sample, I notice that only channel 1's 0th sample is set to 0. The first sample for the other channels is nonzero (and most often negative).

Even more strange is when I test another 4-channel dataset with the same code, this issue does not appear. More specifically, the first time sample on each waveform on all channels is set to 0, as should be the case.

My question is therefore whether or not the timing calibration varies from dataset to dataset. My initial thought was that this should not be the case, but I have two different data sets taken on the same set of channels which give different timing calibration results. Are there any circumstances under which this behavior can happen?

for (ch=0 ; ch<5 ; ch++) {

i = fread(hdr, sizeof(hdr), 1, f);

if (i < 1)

break;

if (hdr[0] != 'C') {

// event header found

fseek(f, -4, SEEK_CUR);

break;

}

chn_index = hdr[3] - '0' - 1;

fread(voltage, sizeof(short), 1024, f);

for (i=0 ; i<1024 ; i++) {

// convert data to volts

waveform[chn_index][i] = (voltage[i] / 65536. - 0.5);

// calculate time for this cell

for (j=0,time[chn_index][i]=0 ; j<i ; j++)

time[chn_index][i] += bin_width[chn_index][(j+eh.trigger_cell) % 1024];

}

}

// align cell #0 of all channels

t1 = time[0][(1024-eh.trigger_cell) % 1024];

for (ch=1 ; ch<4 ; ch++) {

t2 = time[ch][(1024-eh.trigger_cell) % 1024];

dt = t1 - t2;

for (i=0 ; i<1024 ; i++)

time[ch][i] += dt;

} |

|

569

|

Thu Nov 24 13:24:26 2016 |

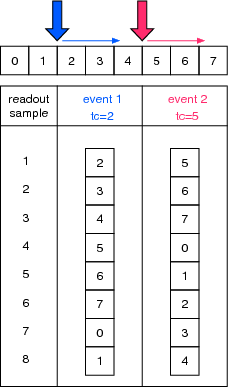

Stefan Ritt | Potential Incorrect Timing Calibration for DRS4 Data | The code in the macro is correct. The misconception lies in the definition what "sample 0" means. Please view the attached picture. This is simplified case with a DRS chip with only 8 cells (instead of 1024). There are two events (blue and red). In the first event, the chip is stopped at trigger cell (tc) 2, in the second case at 5. Since the readout starts with the trigger cell, the first readout sample in the first event belongs to cell #2, the next one to cell #3 and so on. In the second (red) case, the first sample belongs to cell #5, the second to cell #6 and so on. "Aligning cells 0" now means that the physical cell 0 (not the readout sample) is aligned for each channel. In the first event, the 7th readout sample will have the same time in all channels, in the second event the fourth readout cells will have the same time. This is because physical cell #0 is always at different places inside the readout array.

Stefan

| Abhishek Rajput wrote: |

|

Hello,

I was running through a particular binary file containing data taken on all 4 channels of the DRS4 and printing out the value of the first time sample for each channel (per event). While doing so, I noticed that some of these times were negative. For this dataset, channel 1 was chosen as the reference channel (which is the default setup in Stefan's DRS4 macro). From my understanding, the calibration procedure delineated in the DRS4 manual and shown in the code below is supposed to sync the timing of each channel relative to sample 0. However, this does not appear to be the case for when I print out the time value of the first sample, I notice that only channel 1's 0th sample is set to 0. The first sample for the other channels is nonzero (and most often negative).

Even more strange is when I test another 4-channel dataset with the same code, this issue does not appear. More specifically, the first time sample on each waveform on all channels is set to 0, as should be the case.

My question is therefore whether or not the timing calibration varies from dataset to dataset. My initial thought was that this should not be the case, but I have two different data sets taken on the same set of channels which give different timing calibration results. Are there any circumstances under which this behavior can happen?

for (ch=0 ; ch<5 ; ch++) {

i = fread(hdr, sizeof(hdr), 1, f);

if (i < 1)

break;

if (hdr[0] != 'C') {

// event header found

fseek(f, -4, SEEK_CUR);

break;

}

chn_index = hdr[3] - '0' - 1;

fread(voltage, sizeof(short), 1024, f);

for (i=0 ; i<1024 ; i++) {

// convert data to volts

waveform[chn_index][i] = (voltage[i] / 65536. - 0.5);

// calculate time for this cell

for (j=0,time[chn_index][i]=0 ; j<i ; j++)

time[chn_index][i] += bin_width[chn_index][(j+eh.trigger_cell) % 1024];

}

}

// align cell #0 of all channels

t1 = time[0][(1024-eh.trigger_cell) % 1024];

for (ch=1 ; ch<4 ; ch++) {

t2 = time[ch][(1024-eh.trigger_cell) % 1024];

dt = t1 - t2;

for (i=0 ; i<1024 ; i++)

time[ch][i] += dt;

}

|

|

| Attachment 1: drs.pdf

|

|

|

573

|

Tue Nov 29 23:19:06 2016 |

Abhishek Rajput | Potential Incorrect Timing Calibration for DRS4 Data | Hello Stefan,

Thank you for the excellent explanation and diagram. This part of the code is now much clearer to me.

My other questions pertain to the "trigger cell". Firstly, what precisely does this mean? Moreover, how does the "trigger cell" relate to the trigger time delay we can set in the DRS4 application? This is causing some confusion for me, because regardless of where you set the trigger time delay on the DRS4 application, there are still points on the waveform that are saved prior to the moment in time when a pulse exceeds some voltage threshold we set in the application. I get the impression that "trigger delay" and "trigger cell" are unrelated concepts, so any clarification you can provide would be greatly appreciated.

Abhishek

| Stefan Ritt wrote: |

|

The code in the macro is correct. The misconception lies in the definition what "sample 0" means. Please view the attached picture. This is simplified case with a DRS chip with only 8 cells (instead of 1024). There are two events (blue and red). In the first event, the chip is stopped at trigger cell (tc) 2, in the second case at 5. Since the readout starts with the trigger cell, the first readout sample in the first event belongs to cell #2, the next one to cell #3 and so on. In the second (red) case, the first sample belongs to cell #5, the second to cell #6 and so on. "Aligning cells 0" now means that the physical cell 0 (not the readout sample) is aligned for each channel. In the first event, the 7th readout sample will have the same time in all channels, in the second event the fourth readout cells will have the same time. This is because physical cell #0 is always at different places inside the readout array.

Stefan

| Abhishek Rajput wrote: |

|

Hello,

I was running through a particular binary file containing data taken on all 4 channels of the DRS4 and printing out the value of the first time sample for each channel (per event). While doing so, I noticed that some of these times were negative. For this dataset, channel 1 was chosen as the reference channel (which is the default setup in Stefan's DRS4 macro). From my understanding, the calibration procedure delineated in the DRS4 manual and shown in the code below is supposed to sync the timing of each channel relative to sample 0. However, this does not appear to be the case for when I print out the time value of the first sample, I notice that only channel 1's 0th sample is set to 0. The first sample for the other channels is nonzero (and most often negative).

Even more strange is when I test another 4-channel dataset with the same code, this issue does not appear. More specifically, the first time sample on each waveform on all channels is set to 0, as should be the case.

My question is therefore whether or not the timing calibration varies from dataset to dataset. My initial thought was that this should not be the case, but I have two different data sets taken on the same set of channels which give different timing calibration results. Are there any circumstances under which this behavior can happen?

for (ch=0 ; ch<5 ; ch++) {

i = fread(hdr, sizeof(hdr), 1, f);

if (i < 1)

break;

if (hdr[0] != 'C') {

// event header found

fseek(f, -4, SEEK_CUR);

break;

}

chn_index = hdr[3] - '0' - 1;

fread(voltage, sizeof(short), 1024, f);

for (i=0 ; i<1024 ; i++) {

// convert data to volts

waveform[chn_index][i] = (voltage[i] / 65536. - 0.5);

// calculate time for this cell

for (j=0,time[chn_index][i]=0 ; j<i ; j++)

time[chn_index][i] += bin_width[chn_index][(j+eh.trigger_cell) % 1024];

}

}

// align cell #0 of all channels

t1 = time[0][(1024-eh.trigger_cell) % 1024];

for (ch=1 ; ch<4 ; ch++) {

t2 = time[ch][(1024-eh.trigger_cell) % 1024];

dt = t1 - t2;

for (i=0 ; i<1024 ; i++)

time[ch][i] += dt;

}

|

|

|

|

574

|

Wed Nov 30 08:53:58 2016 |

Stefan Ritt | Potential Incorrect Timing Calibration for DRS4 Data | The inverter chain in the DRS4 is continously running in a ring. Once you get a trigger, it is stopped. This happens in any of the 1024 cells. The last cell which sampled a signal plus ne is called "trigger cell". In the previous diagram in event #1, the last cell sampling was "1", so the trigger cell is "2". In event 2 (red case), the trigger cell is 5. If you would run like this, you see only the part of the waveform BEFORE your trigger (since the DRS4 is continously sampling and is stopped with the trigger). In order to see the full peak of your waveform, you can apply some external trigger to shift the trigger position to the right. This is done in the FPGA reading out the DRS4 chip. If your peak is let's say 20 ns wide, and you delay your trigger by 30 ns, you see the peak plus 10 ns right of the peak.

Stefan

| Abhishek Rajput wrote: |

|

Hello Stefan,

Thank you for the excellent explanation and diagram. This part of the code is now much clearer to me.

My other questions pertain to the "trigger cell". Firstly, what precisely does this mean? Moreover, how does the "trigger cell" relate to the trigger time delay we can set in the DRS4 application? This is causing some confusion for me, because regardless of where you set the trigger time delay on the DRS4 application, there are still points on the waveform that are saved prior to the moment in time when a pulse exceeds some voltage threshold we set in the application. I get the impression that "trigger delay" and "trigger cell" are unrelated concepts, so any clarification you can provide would be greatly appreciated.

Abhishek

|

|

|

580

|

Fri Dec 9 04:17:46 2016 |

Abhishek Rajput | Potential Incorrect Timing Calibration for DRS4 Data | Hello Stefan,

Many thanks for the explanations. You've cleared my confusion in this matter.

Abhishek Rajput

| Stefan Ritt wrote: |

|

The inverter chain in the DRS4 is continously running in a ring. Once you get a trigger, it is stopped. This happens in any of the 1024 cells. The last cell which sampled a signal plus ne is called "trigger cell". In the previous diagram in event #1, the last cell sampling was "1", so the trigger cell is "2". In event 2 (red case), the trigger cell is 5. If you would run like this, you see only the part of the waveform BEFORE your trigger (since the DRS4 is continously sampling and is stopped with the trigger). In order to see the full peak of your waveform, you can apply some external trigger to shift the trigger position to the right. This is done in the FPGA reading out the DRS4 chip. If your peak is let's say 20 ns wide, and you delay your trigger by 30 ns, you see the peak plus 10 ns right of the peak.

Stefan

| Abhishek Rajput wrote: |

|

Hello Stefan,

Thank you for the excellent explanation and diagram. This part of the code is now much clearer to me.

My other questions pertain to the "trigger cell". Firstly, what precisely does this mean? Moreover, how does the "trigger cell" relate to the trigger time delay we can set in the DRS4 application? This is causing some confusion for me, because regardless of where you set the trigger time delay on the DRS4 application, there are still points on the waveform that are saved prior to the moment in time when a pulse exceeds some voltage threshold we set in the application. I get the impression that "trigger delay" and "trigger cell" are unrelated concepts, so any clarification you can provide would be greatly appreciated.

Abhishek

|

|

|

|

722

|

Mon Nov 5 17:17:08 2018 |

Sean Quinn | Pi attenuator on eval board inputs? | Dear DRS4 team,

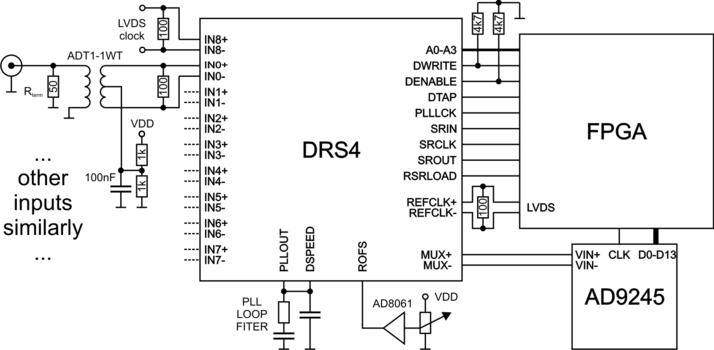

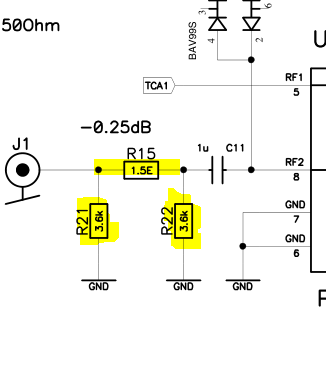

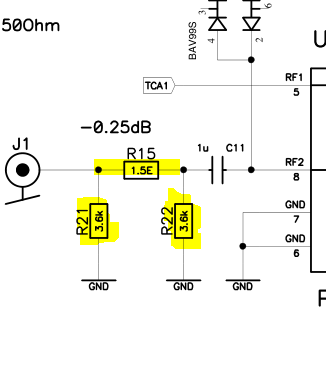

I am curious about this part of the circuit:

What is the purpose of this? |

|

723

|

Thu Nov 8 09:57:26 2018 |

Stefan Ritt | Pi attenuator on eval board inputs? | The attenuator compensates for the gain of the buffer which is slightly above one. In addition, it serves as a "placeholder" in case one wants larger input signals. One can easily convert the attenuator to -6db, -12db, etc. by chaning the resistors.

Stefan

| Sean Quinn wrote: |

|

Dear DRS4 team,

I am curious about this part of the circuit:

What is the purpose of this?

|

|

|

134

|

Sun Oct 23 23:32:28 2011 |

Hao Huan | Phase Shift for ADC Readout | Dear Dr. Ritt,

In the DRS 4 datasheet it is recommended to sample the analog output of the chip after 8~10 ns of the SRCLK edge for it to stablize and thus a phase shift between SRCLK and the ADC sampling clock is necessary. However in the latest version of the evaluation board firmware the phase-shifted clock was generated but not really used for the ADC interface. Is there any reason for that? |

|