| ID |

Date |

Author |

Subject |

|

664

|

Fri Mar 2 20:17:17 2018 |

Stefan Ritt | ROI | N'/N is correct. The 2 us "from the response you got from me" come from the fact that after readout, you have to start the DRS4 again. During this time, the power supply usually becomes slightly unstable, and it takes on the evaluation board about 2us to stabilize it again. Tha't why I add the 2 us. If you don't care about slight offset effect, or if you make a better power supply, you dead time would be 10*30ns = 300ns for 10 samples. Starting the DRS again will take one or two clock cycles from the FPGA, which might add another 30 ns or so, depending on how you program the FPGA. So the best you can achieve for 10 samples is maybe 330 ns, if you have a really good power supply (large capacitors).

You can achieve this functionality with the evaluation board, but you would have to make a special firmware for it.

Stefan

| Steven Block wrote: |

|

Hello,

I have a question about how ROI works. From what I have read, it will only save data that ocurs some time [ta] dictated by the user after an event is triggered as well as a small time [tb] before the event. The technical manual seems to indicated that the deadtime assciated with operating in ROI mode can be reduced by the following factor:

. .

Where N is the number of points in the time window (ex. 2048 or 1024). Is it ok to describe this as:

Where N' is the number of samples in the ROI and N is the same as before.

For example, if I were running at 5Gsps (200ps between samples), only recording 1024 samples per event and I had an signal that lasted 2ns, that means the signal would last 10 samples. If I set the ROI to only save 20 samples around this signal, would my Deadtime go to:

? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly) ? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly)

I recognize that the caveat is that this would work only if the signal was detected during acquistion, which leads to my next question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (using the factor = 1 from above equation), or would it dump the earliest events in the buffer for the more recent ones until it detects a signal?

Finally, I assume this functionality can only be utilized with custom electornics with the DRS4, not the evaulation/demo board, please let me know if this is the case.

Best,

Steven

|

|

|

665

|

Fri Mar 2 21:05:48 2018 |

Steven Block | ROI | Great! That is very helpful.

One more question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (or 30us depending on the supply) for, or would it dump the earliest events in the buffer for the more recent ones until it detects a signal to readout? Or rather, does filling the buffer force a readout or can it dynamically shift out old data until it detects a signal to readout.

Steven

| Stefan Ritt wrote: |

|

N'/N is correct. The 2 us "from the response you got from me" come from the fact that after readout, you have to start the DRS4 again. During this time, the power supply usually becomes slightly unstable, and it takes on the evaluation board about 2us to stabilize it again. Tha't why I add the 2 us. If you don't care about slight offset effect, or if you make a better power supply, you dead time would be 10*30ns = 300ns for 10 samples. Starting the DRS again will take one or two clock cycles from the FPGA, which might add another 30 ns or so, depending on how you program the FPGA. So the best you can achieve for 10 samples is maybe 330 ns, if you have a really good power supply (large capacitors).

You can achieve this functionality with the evaluation board, but you would have to make a special firmware for it.

Stefan

| Steven Block wrote: |

|

Hello,

I have a question about how ROI works. From what I have read, it will only save data that ocurs some time [ta] dictated by the user after an event is triggered as well as a small time [tb] before the event. The technical manual seems to indicated that the deadtime assciated with operating in ROI mode can be reduced by the following factor:

. .

Where N is the number of points in the time window (ex. 2048 or 1024). Is it ok to describe this as:

Where N' is the number of samples in the ROI and N is the same as before.

For example, if I were running at 5Gsps (200ps between samples), only recording 1024 samples per event and I had an signal that lasted 2ns, that means the signal would last 10 samples. If I set the ROI to only save 20 samples around this signal, would my Deadtime go to:

? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly) ? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly)

I recognize that the caveat is that this would work only if the signal was detected during acquistion, which leads to my next question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (using the factor = 1 from above equation), or would it dump the earliest events in the buffer for the more recent ones until it detects a signal?

Finally, I assume this functionality can only be utilized with custom electornics with the DRS4, not the evaulation/demo board, please let me know if this is the case.

Best,

Steven

|

|

|

|

675

|

Mon Mar 19 16:22:42 2018 |

Stefan Ritt | ROI | The DRS4 has an internal storage of 1024 capacitors. They work as a ring buffer, so at 5GSPS you can store 200ns wide signals. After 200ns, the first samples are overwritten by new samples, so you always have the last 200ns of samples stored. Once you trigger the DRS4, this buffer is frozen, and the readout of this buffer causes the dead time. No trigger, no dead time. Hope this answers your question.

Stefan

| Steven Block wrote: |

|

Great! That is very helpful.

One more question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (or 30us depending on the supply) for, or would it dump the earliest events in the buffer for the more recent ones until it detects a signal to readout? Or rather, does filling the buffer force a readout or can it dynamically shift out old data until it detects a signal to readout.

Steven

| Stefan Ritt wrote: |

|

N'/N is correct. The 2 us "from the response you got from me" come from the fact that after readout, you have to start the DRS4 again. During this time, the power supply usually becomes slightly unstable, and it takes on the evaluation board about 2us to stabilize it again. Tha't why I add the 2 us. If you don't care about slight offset effect, or if you make a better power supply, you dead time would be 10*30ns = 300ns for 10 samples. Starting the DRS again will take one or two clock cycles from the FPGA, which might add another 30 ns or so, depending on how you program the FPGA. So the best you can achieve for 10 samples is maybe 330 ns, if you have a really good power supply (large capacitors).

You can achieve this functionality with the evaluation board, but you would have to make a special firmware for it.

Stefan

| Steven Block wrote: |

|

Hello,

I have a question about how ROI works. From what I have read, it will only save data that ocurs some time [ta] dictated by the user after an event is triggered as well as a small time [tb] before the event. The technical manual seems to indicated that the deadtime assciated with operating in ROI mode can be reduced by the following factor:

. .

Where N is the number of points in the time window (ex. 2048 or 1024). Is it ok to describe this as:

Where N' is the number of samples in the ROI and N is the same as before.

For example, if I were running at 5Gsps (200ps between samples), only recording 1024 samples per event and I had an signal that lasted 2ns, that means the signal would last 10 samples. If I set the ROI to only save 20 samples around this signal, would my Deadtime go to:

? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly) ? (The second portion of this equation comes from a response I recieved earlier, but I just want to make sure I understand this concept properly)

I recognize that the caveat is that this would work only if the signal was detected during acquistion, which leads to my next question. If no signals were detected in the 1024*200ps time frame in ROI mode, would the DRS4 go dead for 32us (using the factor = 1 from above equation), or would it dump the earliest events in the buffer for the more recent ones until it detects a signal?

Finally, I assume this functionality can only be utilized with custom electornics with the DRS4, not the evaulation/demo board, please let me know if this is the case.

Best,

Steven

|

|

|

|

|

59

|

Tue Mar 30 22:57:34 2010 |

Hao Huan | ROFS Configuration | Hi Stefan,

according to the DRS4 datasheet, if we want an input range centered around U0, the ROFS should be 1.55V-U0. However when I read the codes of the evaluation board application, ROFS seems to be 1.6V-1.25*U0 where the coefficient 1.25 is said to come from sampling cell charge injection correction. Is it the right equation to use? What exactly does that charge injection correction mean?

Thanks a lot.

|

|

68

|

Thu Apr 15 13:48:40 2010 |

Stefan Ritt | ROFS Configuration |

| Hao Huan wrote: |

|

Hi Stefan,

according to the DRS4 datasheet, if we want an input range centered around U0, the ROFS should be 1.55V-U0. However when I read the codes of the evaluation board application, ROFS seems to be 1.6V-1.25*U0 where the coefficient 1.25 is said to come from sampling cell charge injection correction. Is it the right equation to use? What exactly does that charge injection correction mean?

Thanks a lot.

|

1.55V-U0 is the theoretical values, but there are certain "dirt" effects like chip-to-chip variation and charge injection. The difference between various chips is easily 20-30mV, so there is not a single "correct" value. The formula 1.6V-1.25*U0 I developed for a special evaluation board, where it kind of worked better than the theoretical value, but I never made systematic studies. One should average over several chips and use some solid average there. Best is if you try both formulas and check what give you the better linearity. |

|

200

|

Tue Dec 4 09:24:22 2012 |

Zhongwei Du | Question of drs4 using | When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now. |

|

201

|

Tue Dec 4 09:39:44 2012 |

Stefan Ritt | Question of drs4 using |

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan |

|

202

|

Tue Dec 4 09:50:11 2012 |

Zhongwei Du | Question of drs4 using |

| Stefan Ritt wrote: |

|

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan

|

"Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. "

In this process , should i config any registers( WSR,WCR,CR ) ? |

|

203

|

Tue Dec 4 09:55:43 2012 |

Stefan Ritt | Question of drs4 using |

| Zhongwei Du wrote: |

|

| Stefan Ritt wrote: |

|

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan

|

"Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. "

In this process , should i config any registers( WSR,WCR,CR ) ?

|

After power-up reset, these registers are all set to "1", which should be ok to start.

BTW, Jinhong Wang <wangjinh@mail.ustc.edu.cn> from your institute hast the chip correctly working. Maybe he can help you in a more direct way than I can.

|

|

193

|

Wed Nov 21 08:34:52 2012 |

Gyuhee Kim | Question for using Multi board | Hi.

I have 2 DRS4 evaluation V4 boards, and I want to use these 2 board to multi board DAQ system for 4 ch vs 4 ch DAQ.

But there is no option for multi board use. I just only find the multi board trigger mode check button on DRS4 Oscilloscope program, but I couldn`t check.

Is there any method to use multi board?

Best regards.

Gyuhee. |

|

194

|

Wed Nov 21 08:38:26 2012 |

Stefan Ritt | Question for using Multi board |

| Gyuhee Kim wrote: |

|

Hi.

I have 2 DRS4 evaluation V4 boards, and I want to use these 2 board to multi board DAQ system for 4 ch vs 4 ch DAQ.

But there is no option for multi board use. I just only find the multi board trigger mode check button on DRS4 Oscilloscope program, but I couldn`t check.

Is there any method to use multi board?

Best regards.

Gyuhee.

|

This mode is not yet implemented in firmware. Maybe I find some time towards the end of this year to add this. At the moment, you have to build and external trigger to synchronize the two boards. There are also 16-channel boards on the market where you would not need a multi-board mode. Just Google for "DT5742".

/Stefan |

|

195

|

Wed Nov 21 08:48:00 2012 |

Gyuhee Kim | Question for using Multi board |

| Stefan Ritt wrote: |

|

| Gyuhee Kim wrote: |

|

Hi.

I have 2 DRS4 evaluation V4 boards, and I want to use these 2 board to multi board DAQ system for 4 ch vs 4 ch DAQ.

But there is no option for multi board use. I just only find the multi board trigger mode check button on DRS4 Oscilloscope program, but I couldn`t check.

Is there any method to use multi board?

Best regards.

Gyuhee.

|

This mode is not yet implemented in firmware. Maybe I find some time towards the end of this year to add this. At the moment, you have to build and external trigger to synchronize the two boards. There are also 16-channel boards on the market where you would not need a multi-board mode. Just Google for "DT5742".

/Stefan

|

Thanks Stefan.

I will build external trigger system. |

|

495

|

Sat Apr 2 11:21:10 2016 |

Felix Bachmair | Question about timimng calibration | Hi,

I am trying to understand some details about the timing calibration.

We wrote our own code but we more or less use the ideas of the Oscilloscope class.

In the binary file writing of in the function Osci.cpp::SaveWaveforms() (line 924ff)

the following code is executed:

if (m_waveDepth == 2048) {

t = (tcal[j]+tcal[j+1])/2;

j++;

} else

t = tcal[j];

I do not understand the averaging of the to adjacent calibration constants. Could you explain this? Do one have two measurements?

Cheers

Felix

|

|

496

|

Sat Apr 2 11:41:07 2016 |

Stefan Ritt | Question about timimng calibration | The evaluation board normally has 1024 bins per channel. We offer an option with 2048 bins using channel cascading, to capture longer waveform windows. The binary data format is however defined as having 1024 bins. Therefore, for the 2048 bin boards, the software averages over two adjacent cells and saves effectively 1024 bins. The noise of each bin improves this way by sqrt(2). The time however is not very well defined, since you average the voltage of two bins. Therefore, I simple also average over the time of the two bins. Maybe this is not the best way, so feel free to change this.

Stefan

| Felix Bachmair wrote: |

|

Hi,

I am trying to understand some details about the timing calibration.

We wrote our own code but we more or less use the ideas of the Oscilloscope class.

In the binary file writing of in the function Osci.cpp::SaveWaveforms() (line 924ff)

the following code is executed:

if (m_waveDepth == 2048) {

t = (tcal[j]+tcal[j+1])/2;

j++;

} else

t = tcal[j];

I do not understand the averaging of the to adjacent calibration constants. Could you explain this? Do one have two measurements?

Cheers

Felix

|

|

|

445

|

Wed Aug 19 15:07:53 2015 |

Martin Petriska | QtPALS | There is software for DRS4 board and positron lifetime measurement availiable. Still in beta but works. Its usable for measuring time between pulses in two or three channels and histogramming that time. (May be time of flight measurement should be tested too) Project code is here: http://sourceforge.net/projects/qtpals/. More about it is here http://iopscience.iop.org/1742-6596/505/1/012044/. Still tested only with v3 and v4 evaluation board, but should work with new callibration in v5 board too. |

|

522

|

Wed May 11 15:48:57 2016 |

SANDJONG Saturnin Orly | Probl�me de Calibration de la DRS4 | Bonjour, Je suis en stage dans un laboratoire ou on utilise pour echantillonnage des données, une cartes DRS4 5GSPS avec 1024 cell, mon probléme réside dans la partie Calibration en tension selon l'article "Novel Calibration Method for Switched Capacitor Arrays Enables Time Measurements with Sub-Picosecond Resolution".

En fait je ne comprends pas précisément ces 3 parties de la calibration en tension. Quelqu'un pourras t-il s'il vous plait m'expliquer assez clairement avec des exemples comment il faut s'y prendre?

Merci et bien Cordialement. |

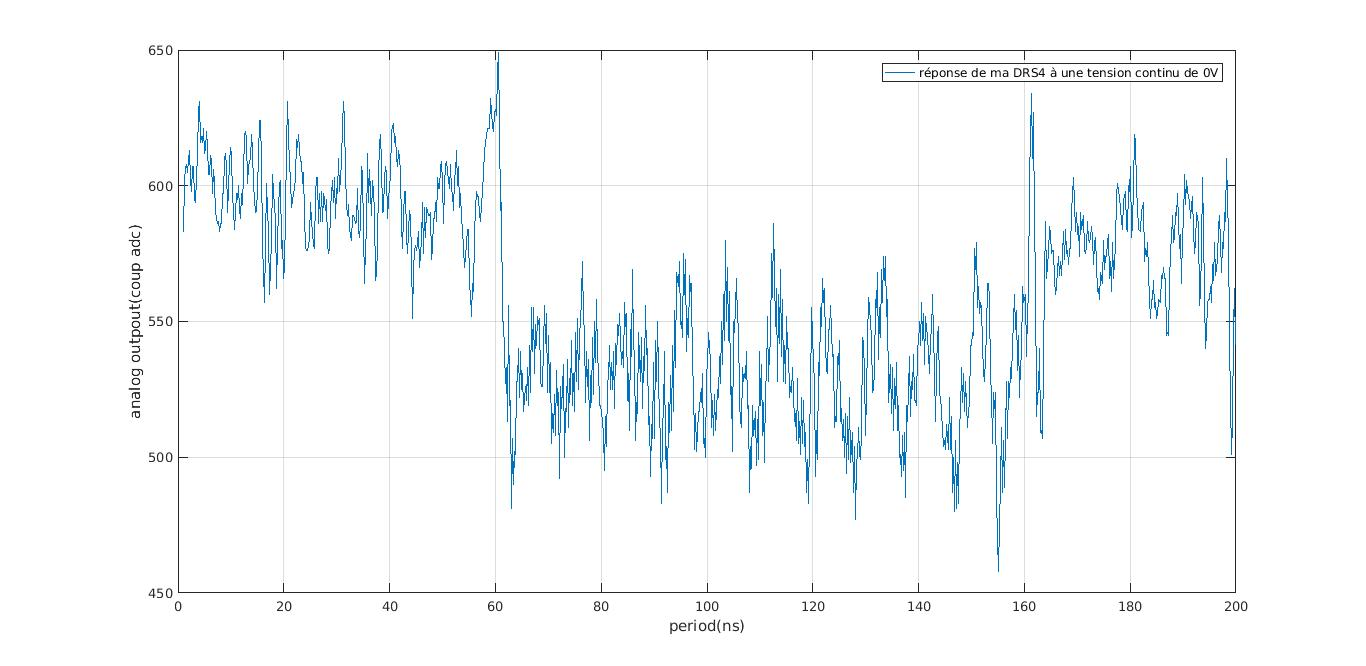

| Attachment 1: piedestaux_per_time.jpg

|

|

|

873

|

Mon Mar 7 13:38:03 2022 |

Radoslaw Marcinkowski | Problems with DRS4 Evaluation Board after Windows 10 upgrade - share of experiences | Dear DRS4 Users,

I would like to share my expireinces with using of DRS4 Evaluation Board software (oscilloscope) after upgrade of Windows 10.

I had Windows 10 (Enterprise) in version from ~2016. It was working fine with DRS4 Scope software. Due to the company policy, Windows was upgraded to the newer version (2019). Since this time the board was not recognized any more as DRS4 Evaluation Board, both by Windows and DRS4 Scope standard software. Changing USB sockets did not help at all. I installed once more time Zadig USB driver (suggested by https://www.psi.ch/en/drs/software-download), no Admistrator rights were needed. It took long time, about 10 minutes or more, it suggested restart in the meantime, and finally noticed that ... installation failed! Even that, DRS4 software started to recognize the board without the problem even without reboot. Let me notice that all users on this machine can use the DRS4 software even if installation was done by non-administrator user.

Regards,

Radek |

|

549

|

Wed Oct 26 21:15:35 2016 |

Alexey Lubinets | Problems with DRS command line | Hello, everybody

I have installed the software for the DRS4 Evaluation Board.

When I run the DRS Oscilloscope, it works OK (at least, my computer "knows", that the board is connected). But when I run the DRS Command Line Interface, it writes "USB successfully scanned, but no boards found

No DRS boards found".

How can I manage with this problem? The drivers for the DRS Evaluation Board are installed.

Regards, Alexey Lubinets |

|

550

|

Thu Oct 27 08:29:26 2016 |

Stefan Ritt | Problems with DRS command line |

| Alexey Lubinets wrote: | Hello, everybody

I have installed the software for the DRS4 Evaluation Board.

When I run the DRS Oscilloscope, it works OK (at least, my computer "knows", that the board is connected). But when I run the DRS Command Line Interface, it writes "USB successfully scanned, but no boards found

No DRS boards found".

How can I manage with this problem? The drivers for the DRS Evaluation Board are installed.

Regards, Alexey Lubinets |

You are the first one describing this problem (out of ~200 people), so I guess the problem must be on your side. Have you made sure to start the DRS oscilloscope and the Command Line Interface not at the same time? Only one program can access the board at a given time. Have you tried disconnecting and re-connecting the board?

Stefan |

|

551

|

Fri Oct 28 15:02:18 2016 |

Simon Mendisch | Problems with DRS command line |

| Stefan Ritt wrote: |

You are the first one describing this problem (out of ~200 people), so I guess the problem must be on your side. Have you made sure to start the DRS oscilloscope and the Command Line Interface not at the same time? Only one program can access the board at a given time. Have you tried disconnecting and re-connecting the board?

Stefan |

Hello,

that means, I am the second one experiencing this problem. To be more specific, the "No DRS Board found" problem is only present at one machine running Win7x64.

DRSOsc, of course not running simultaneously works just fine. Only drscl shows this behavior. Upgrading to a newer software version or a re-installation of the old one didn't solve the issue.

On other Win7x64 machines everything works fine, so I am pretty sure the problem is on this specific machine. Do you have any idea what could be the cause of this behavior?

Best Regards,

Simon |

|