| ID |

Date |

Author |

Subject |

|

907

|

Thu Feb 22 10:37:03 2024 |

Stefan Ritt | Simulation of FPGA | The Cypress has its own firmware, contained in the distribution under firmware/CY7C68013A/drs_eval.c. There you can see how the data is fetched. I kind of forgot how exactly it worked, since I wrote that code back in 2011. But most if the Cypress code is just the configuration of the USB, the communication with the FPGA is kind of straight forward in the Cypress implementation. But you have to read the manual of that chip to understand it.

Unfrtunately there is no full testbench for the firmware, since I didn't have a VHDL Model of the Cypress, so I implemente dit the "hard" way ;-)

Best,

Stefan

| Rod McInnis wrote: |

|

Hello:

A bit of background: I am working on a project that is utilizing the DRS4 Evaluation board as a prototype platform for a dedicated, special use capture. We will only be utilizing one channel of the ADC capture, and the 1024 samples is more than enough.

What I will need to do, however, is do some preprocessing on the incoming ADC data, running some calculation on the fly, possibly some filtering and other transformations before putting the data into the FPGA block memory for transfer to the host via the Cypress USB interface. I will be modifying the "drs4_eval5" VHDL file and doing a new FPGA build.

It will be essential that I be able to simulate this, from the ADC input to the data flow to the Cypress chip. I have "eval board files" which includes the VHDL source files, Xilinxe ISE project files and some very basic simulation testbenches.

Unfortunately, the simulation testbenches call out a "drs4_eval1" module while the Xilinx project uses a "drs4_eval5" module, and the module ports are a little different. I think I can work around that, however. I have run the simulatilon "drs4_eval1_tb", which does a simple write to a Control Register. I need to expand this simulation so that it will initiate a full capture and then transfer the data from the RAM to the Cypress chip.

What I am most confused about is how the Cypress chip sucks out the data from the FPGA block ram. I would expect it to use a burst mode data transfer rather than the cumbersom CSR read/write, but I haven't found any documentation on how this interface works.

Q1: Is there a simulation testbench file available that does the 1024 sample data transfer?

Q2: Is there a waveform diagram that shows the protocol / signal handshake between the FPGA and Cypress chip for this data transfer?

Thank you

Rod McInnis

|

|

|

913

|

Mon Jan 6 12:52:23 2025 |

Stefan Ritt | Problem with C++ script to use DRS4 evaluation board. Not taking data. | 1. Transparent mode is not needed for the hardware trigger, no idea why the code is there. You can probably remove it.

2. EnableTCal is only for the sake of having some waveforms at the input. Indeed you have to disable it to sample real signals.

3. EnableTrigger() is there to enable the hardware trigger. The flag2 is ther for historical reasons (used in older versions of the board).

4. You figured that out already yourself.

5. The functions CalibrateVolt() and CalibrateTiming() are the ones which get called if you click on volt and time calibration in the DRSOsc application. The calibration is store on the evaluation board, so you do not have to call them in your program.

| Matias Henriquez wrote: |

|

Hello, some updates:

4. I was able to capture correct waveforms using c++ code. I needed to use the function SetTriggerDelayNs() to properly capture my waveforms.

5. I noticed that the drsosc program source code uses the functions: CalibrateVolt() and CalibrateTiming() for performing calibration. For these to work, is it necessary to use EnableAcal() and EnableTcal() functions right?

I'd appreciate if you can still give some insights about 1,2 and 3. Thank you!

| Matias Henriquez wrote: |

|

Hello,

I need to write a script in C++ to take data using the DRS4 evaluation board v4. For that, I used the drs_exam.cpp example as a reference. This is my code (see attachement 2), which is very similar to the provided example, however the difference is that I need to trigger on CH1 OR CH2. In the next version I will need to trigger with an OR in all channels.

The problem is, my code gets stuck in waiting for trigger or only 1 event occurs (event 0). I read that event and it doesn't even go above 30mV, which was the threshold I set. There are some questions I have:

- Why Transparent mode is activated for Hardware Trigger?

- Why EnableTCal is activated? is the drs4_exam example based acquires the 100MHz reference just for the sake of the example? or is just a time calibration routine?

- Can someone explain the function EnableTrigger(flag1,flag2) in boardType 8? it si not clear to me how the trigger is enabled.

- To check that my input signals are correct, I run the drsosc application and I can see the signals with no problem (see attachement 1). However I noticed that I had to configure the trigger delay in the drsosc application, and I don't do that in my c++ code. I will try that later.

- How do I perform voltage calibration and time calibration using the c++ functions?

Thank you so much for your help.

|

|

|

|

915

|

Wed Mar 26 08:42:08 2025 |

Stefan Ritt | drs_exam.cpp not compile | You have to link against the DRS.cpp library, plus usblib, plus ... Note there is both a Makefile and a CMakeLists.txt for it. Google how to use "make" or "cmake".

Stefan |

|

920

|

Fri May 9 08:17:50 2025 |

Stefan Ritt | Handling of Write Shift Register and Write Config Register | This is correct. Setting A0-A3 to 0b1101 multiplexes the Shift Write Register to SROUT, so you will either a "0" or a "1" depending on which of the two channels was written last.

Your segmented capture does unfortunately not work. Due to a bug in the silicon, the first (e.g. even) written channel gets half overwritten when you start sampling the second (odd) channel. I should remove that from the documentation.

Furthermore, reading the chip while writing on the "other side" introduces quite some additional noise. The recommended way to do simultaneous reading and writing is therefore to use two separate DRS4 chips and split the input signals to both chips, then read from one chip while writing to the other chip. This keeps the crosstalk at a minimum and both chips run at full performance.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)?

|

|

|

921

|

Fri May 9 08:26:17 2025 |

Stefan Ritt | Clarification of full channel readout | The full readout mode is not really recommended since you have to pull out the stop position separately. Just do the ROI readout using the RSRLOAD signal, and then do 1024 samples, which also gives you the full waveform, but also the stop position in a single readout cyclce. The "full readout mode" is more there for "historical reasons", but nobody really uses it any more.

If you are interested in all details of the control signals, I propose you have a look at the VHDL code which comes with the software distribution. It's contained in the "firmware" subdirectoy and called drs4_eval5_app.vhd

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're working on a new product using the DRS4 IC, and want to do a full readout from cell 0 (not just Region of Interest). I have a couple of questions I hope you can help me with:

- We plan to do a full readout sequence, starting at cell 0. Part of that sequence includes pulsing RSRLOAD and reading out the stop position as shown in v0.9 datasheet Figure 15. What should the DRS4 address bits A3..0 be set to for reading out the stop position? (I’m assuming it’s 1011 ‘Address Read Shift Register’)

- What is the output delay from the falling edge of SRCLK to valid data at SROUT?

- For channel readout, we pulse SRCLK to advance the read shift register. The diagram shown in v0.9 datasheet Figure 12 appears to show that the analog output is updated on the rising edge of SRCLK. Is this correct or have I misread the diagram? (Other shift register transfers are clocked on the falling edge

- The DRS4 v0.9 datasheet Figure 7 shows that the Configuration register is clocked on the falling edge of SRCLK. Just below that is the text “The new register content becomes immediately active at the eighth rising edge of the SRCLK signal.” Should that perhaps read ‘… the eighth falling edge of the SRCLK signal’?

|

|

|

923

|

Tue May 13 08:51:34 2025 |

Stefan Ritt | Handling of Write Shift Register and Write Config Register | Yes this is correct. Anyhow, even if it would be working, you would not be happy with it. After having designed ~10 boards with the DRS4 chip, I learned the hard way that any digital activity on the board during the sampling phase is strictly forbidden. You see crosstalk up to 100's of mV in some cases (with a preamplifier on the board, 10-20mV without preamp). So rule #1 is to keep the board as "quite" as possible when sampling the input. If you would readout the odd channels of the DRS4 during sampling of the even channels, you would probably get so much crosstalk that the samples are almost unusable. Even if you would do this with two DRS4 chips next to each other, you have to make sure to put proper grounding between the two chips, and operate them completely independent (like each one has it's onw contol lines going to the FPGA). Designing such boards is not so easy and takes lots of experience from the layouter.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi Stefan

Just so I'm 100% clear; is there no reliable way to perform 2 segmented captures with a single DRS4 IC?

While not a showstopper, this is a bit disappointing.

| Stefan Ritt wrote: |

|

This is correct. Setting A0-A3 to 0b1101 multiplexes the Shift Write Register to SROUT, so you will either a "0" or a "1" depending on which of the two channels was written last.

Your segmented capture does unfortunately not work. Due to a bug in the silicon, the first (e.g. even) written channel gets half overwritten when you start sampling the second (odd) channel. I should remove that from the documentation.

Furthermore, reading the chip while writing on the "other side" introduces quite some additional noise. The recommended way to do simultaneous reading and writing is therefore to use two separate DRS4 chips and split the input signals to both chips, then read from one chip while writing to the other chip. This keeps the crosstalk at a minimum and both chips run at full performance.

Stefan

| Jonathan Bradshaw wrote: |

|

Hi all

We're building a product which will use two different operating modes; firstly a long capcture using channel daisy chaining (2048 samples) and secondly a segmented capture (2 separate captures of 1024 samples each).

For the long capture, I'm looking to capture 2048 samples for 4 channels. Therefore I configure the Write Shift Register to 0b01010101 and the Write Config Register to 0b11111111. During capture with DWRITE=1 the Write Shift Register will update. Am I correct that once the capture is done and DWRITE=0, I can set A3..0 to 0b1101 and simply read the value of WSROUT to tell the difference?

For the segmented capture, I'm looking to capture 1024 samples for 4 channels on a first tirgger pulse, followed by 1024 samples for 4 channels on a second pulse. Therefore I configure the Write Shift Register to 0b11111111 and the Write Config Register to 0b01010101 and set DWRITE=0 to capture. After the first trigger I set DWRITE=0 and need to update the Write Config Register. Do I need to write in a whole 8 bits to the Write Config Register (i.e. 0b10101010), or can I just shift in a single new bit (value 0b0)?

|

|

|

|

|

926

|

Mon Jul 7 16:53:26 2025 |

Stefan Ritt | Wrong Firmware Version: board has 13279, required is 15147. Board may not work properly | You have to use the software belonging to that board. You cannot use the newest software with an old board. Look here:

https://www.psi.ch/en/ltp-muon-physics/software-download

So you need teh software version 2.0.

/Stefan

|

|

156

|

Wed Feb 29 06:46:47 2012 |

Sonal | DRS4- analog pulse counting |

| Stefan Ritt wrote: |

|

| sonal wrote: |

|

Hello Sir,

Regarding to analog pulse counting by using DRS4 Rev.2.0 board, you have said that "There is a way to perform the counting dead time free, but that requires the V4 board, which has a hardware comparator on all four channels (The V2 board has only one comparator and a multiplexer). The output of these comparators go directly to the FPGA, which can then trigger on these signals. In principle one could implement a hardware counter in the FPGA, which works practically dead time free. But this requires a new firmware which has to be written. Either you do it yourself using the Xilinx development tools, or you wait until I find some time to implement this, which could take a couple of weeks or even months."

I am interested in it. I have DRS4 Rev.2.0 board. I have FPGA and Microcontroller firmware for this board. How can I implement this concept of counting pulses?

|

As I said above, you need a V4 board which has the four hardware comparators mounted. You cannot do that with the V2 board, even with a firmware upgrade.

The firmware upgrade for the V4 board is not yet ready and I won't have time for that in the next 3-4 weeks, but afterwards maybe.

Best regards,

Stefan

|

Thank you for your response.

The DRS4 Rev.2.0 with one Multiplexer and a Comparator I think may be is ok for me. Since I wanted to implement counter in FPGA, I have gone through firmware but its very difficult for me to get the flow of data from DRS to USB. Could you help me to get familiar with or to get flow of the data from DRS to the USB?

Thank You,

Sonal |

|

679

|

Mon Apr 16 21:21:29 2018 |

Sobimpe Eniola | DRS4 read_binary.cpp | Hello everyone,

The new read_binary.cpp code

I will be very glad if anyone can help with the old version of read_binary.cpp code. The latest version I saw online was updated on June 30th, 2014, but I need the old version of the code to compare what changes were made in the latest version. This will help me to modify it and be able to read my data successfully. Thanks |

|

386

|

Wed Oct 15 10:14:32 2014 |

Simon Weingarten | Clock settings in daisy chain DAQ | Hi,

I'm currently working on a little DAQ system with four DRS evaluation boards. Do i need to apply any specific settings when using the clock in/out connectors for synchronization? I do not see anything like that in the drs_exam_multi example.

Any help would be greatly appreciated!

Best,

Simon |

|

388

|

Wed Oct 15 11:34:43 2014 |

Simon Weingarten | Clock settings in daisy chain DAQ |

| Stefan Ritt wrote: |

|

| Simon Weingarten wrote: |

|

Hi,

I'm currently working on a little DAQ system with four DRS evaluation boards. Do i need to apply any specific settings when using the clock in/out connectors for synchronization? I do not see anything like that in the drs_exam_multi example.

Any help would be greatly appreciated!

Best,

Simon

|

Right, I did not yet put any code there. What you need on all slave boards is

b->SetRefclk(true);

b->SetFrequency(...);

Set SetFrequency() is needed to restart the boards with the external clock.

This works of course only if you have the clock signals connected as written in the manual. If not, the boards won't work after you switch the reference clock.

Best regards,

Stefan

|

Thank you so much for the fast reply! I'll give it a try.

Best regards,

Simon |

|

403

|

Fri Apr 17 10:07:38 2015 |

Simon Weingarten | Clock settings in daisy chain DAQ | Hi Stefan,

do you know how these numbers (400ps and 60ps) scale with the sampling rate? The manual says they are for 5GS/s, do they change with slower sampling?

Thanks and best regards,

Simon

| Stefan Ritt wrote: |

|

Here is the full version of the program with clock daisy-chaining. Before switching to the external clock, it checks if the clock really is there (by reading an internal scaler), and only then enables it. Note that the code also works without clock daisy-chaining. But without clock daisy-chaining your have some 400 ps time resolution between boards, and with clock daisy-chaining you get some 60 ps.

|

|

|

551

|

Fri Oct 28 15:02:18 2016 |

Simon Mendisch | Problems with DRS command line |

| Stefan Ritt wrote: |

You are the first one describing this problem (out of ~200 people), so I guess the problem must be on your side. Have you made sure to start the DRS oscilloscope and the Command Line Interface not at the same time? Only one program can access the board at a given time. Have you tried disconnecting and re-connecting the board?

Stefan |

Hello,

that means, I am the second one experiencing this problem. To be more specific, the "No DRS Board found" problem is only present at one machine running Win7x64.

DRSOsc, of course not running simultaneously works just fine. Only drscl shows this behavior. Upgrading to a newer software version or a re-installation of the old one didn't solve the issue.

On other Win7x64 machines everything works fine, so I am pretty sure the problem is on this specific machine. Do you have any idea what could be the cause of this behavior?

Best Regards,

Simon |

|

756

|

Tue Jun 25 23:04:29 2019 |

Si Xie | drs_exam is always reading out a sin wave | We are using the drs_exam.cpp to read out waveforms, but it seems to be outputting only sin waves on all channels - as if it was reading out the simulated waveform from the oscilloscope program if we run it without the board plugged in. Does anyone know what is causing this?

We are taking data with a pulser plugged into channel 1, which produces a single pulse with width of 8ns, and nothing plugged into channel 2.

Our board is as follows:

Found DRS4 evaluation board, serial #2567, firmware revision 21305

Board type: 9

The output is something like the following:

Event #0 ----------------------

t1[ns] u1[mV] t2[ns] u2[mV]

0.000 -452.7 0.026 -469.3

0.289 -460.8 0.293 -469.8

0.413 -477.3 0.400 -481.5

0.642 -485.3 0.650 -482.4

0.806 -486.9 0.821 -477.8

1.086 -476.8 1.085 -457.2

1.183 -467.3 1.162 -446.4

1.450 -435.6 1.459 -405.1

1.619 -410.1 1.630 -373.3

1.843 -366.2 1.851 -323.9

1.945 -342.9 1.948 -298.9

2.221 -275.7 2.210 -229.3

2.359 -237.6 2.357 -187.6

2.602 -165.6 2.609 -111.2

2.687 -141.1 2.697 -84.3

2.976 -50.5 2.987 5.5

3.164 8.4 3.144 53.3

3.377 73.9 3.384 124.2

3.503 111.4 3.506 158.0

3.753 182.0 3.769 226.9

3.924 227.5 3.929 265.8

|

|

758

|

Wed Jun 26 15:10:09 2019 |

Si Xie | drs_exam is always reading out a sin wave | I see. Where is the code that we can use to turn off the generator? I thought the example is taking data with CH1 as the trigger.

For our board, which is BoardType == 9, it is running these lines:

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

Is that not using the hardware trigger with CH1 as the source?

| Stefan Ritt wrote: |

|

Sure, that’s correct. The example program turns on the internal sine wave generator in case people don’t have a real signal. That’s why it’s called „example“. Find the code which turns on the generator and change it. You will also have to change the trigger settings depending on your actual signal.

Stefan

| Si Xie wrote: |

|

We are using the drs_exam.cpp to read out waveforms, but it seems to be outputting only sin waves on all channels - as if it was reading out the simulated waveform from the oscilloscope program if we run it without the board plugged in. Does anyone know what is causing this?

We are taking data with a pulser plugged into channel 1, which produces a single pulse with width of 8ns, and nothing plugged into channel 2.

Our board is as follows:

Found DRS4 evaluation board, serial #2567, firmware revision 21305

Board type: 9

The output is something like the following:

Event #0 ----------------------

t1[ns] u1[mV] t2[ns] u2[mV]

0.000 -452.7 0.026 -469.3

0.289 -460.8 0.293 -469.8

0.413 -477.3 0.400 -481.5

0.642 -485.3 0.650 -482.4

0.806 -486.9 0.821 -477.8

1.086 -476.8 1.085 -457.2

1.183 -467.3 1.162 -446.4

1.450 -435.6 1.459 -405.1

1.619 -410.1 1.630 -373.3

1.843 -366.2 1.851 -323.9

1.945 -342.9 1.948 -298.9

2.221 -275.7 2.210 -229.3

2.359 -237.6 2.357 -187.6

2.602 -165.6 2.609 -111.2

2.687 -141.1 2.697 -84.3

2.976 -50.5 2.987 5.5

3.164 8.4 3.144 53.3

3.377 73.9 3.384 124.2

3.503 111.4 3.506 158.0

3.753 182.0 3.769 226.9

3.924 227.5 3.929 265.8

|

|

|

|

759

|

Wed Jun 26 15:17:51 2019 |

Si Xie | Running drs_example.cpp | Hi Rodrigo, I'm wondering how you solved your original triggering problem. We are also having trouble with collecting data continously using the example. Thanks.

| Rodrigo Trindade de Menezes wrote: |

|

We found a way to solve the previous problem, but right now when we try to set the input range only -0.5 to 0.5 is working. When we set the function "SetInputRange(0.5)" for 0 to 1V the output is all zeros and with "SetInputRange(0.45)" we just get all the outputs -49.9mV. What does that means? How to fix?

| odrigo Trindade de Menezes wrote: |

|

Hello,

We have been using the DRS4 evaluation board (S/N 2636) that works with the scope application. However we are trying to run the DRS4 evaluation board remotely by modifying the drs_exam.cpp to acquire and store data continuously.

We compiled the DRS_example.cpp without the wxWidgets but when we try to run the program, it appears to trigger on nonsense. The program appears to not be sensitive to the trigger threshold (although for very large trigger threshold it gets stuck in a waiting mode). Is there a way to ensure that the "normal" trigger mode is set? We are worried that the auto mode is running. Otherwise, not sure why the program is triggering on nonsense. By the way, it does not work with the wxWidgets compiled either so we are worried that there is an additional flag that needs to be set. The routine does not appear to conduct a calibration -- is this not necessary?

Another issue that we are having is with the data set stored on the .txt file looks incorrect. The time channel stops at 200 (but we think it should go up to 1024). In addition, the voltage channel appears to hover around small values near zero (as if triggering on noise). The output file appears this way even when we change the threshold to much higher values. It suggests that the trigger threshold is not actually being set? There are events where the output voltage appears to oscillate through huge negative and positive values too. So not sure what's going on.

Thanks!

Rodrigo

|

|

|

|

800

|

Wed Oct 21 15:03:13 2020 |

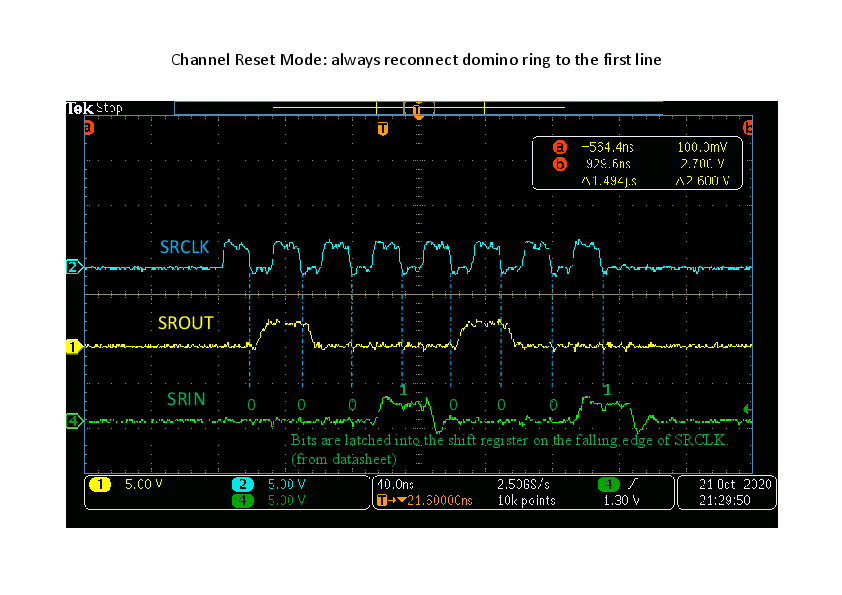

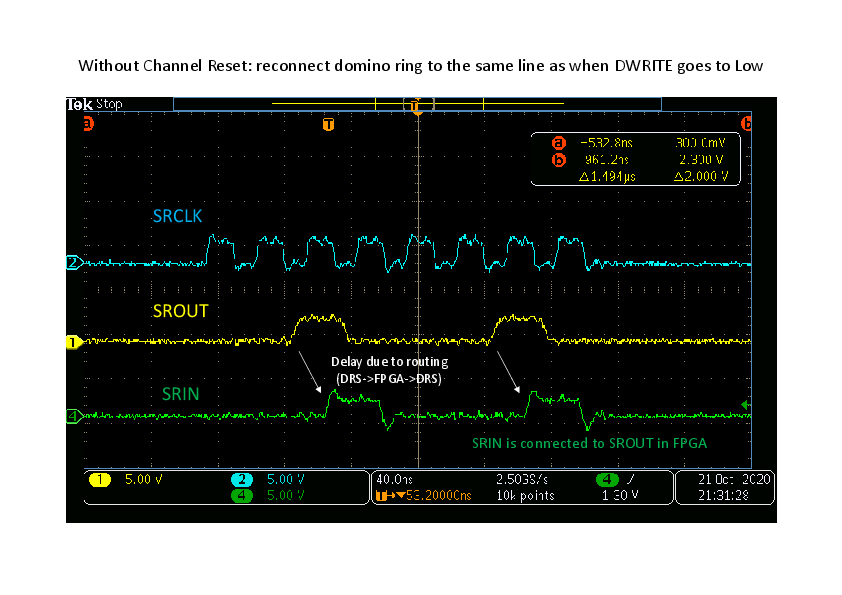

Seiya Nozaki | Timing diagram of SROUT/SRIN signal to write/read a write shift register | Dear Stefan,

I have questions about the timing diagram of SROUT/SRIN signal to write/read a write shift register.

1) Value of SRIN signal is saved at the falling edge of SRCLK, correct? (It is written in datasheet, page12, "Bits are latched into the shift register on the falling edge of SRCLK")

2) When are 8-bits of write shift register shown through SROUT? At ridging edges of SRCLK? and with additional delay(~10ns)? or falling edges?

3) In my understanding, when SRCLK is sent to DRS4, we can read and write the values in parallel, right? If so, is it possible just to read the registers without updating the registers?

[Background]

We have two modes to set the write shift register, the first one is to always reconnect to the first line and another one is to reconnect to the same line as when DWRITE goes to Low.

We can read/write the write shift register with the first mode (channel reset, page1). But we rarely face the problem of write shift register, unexpected values are written, with the second mode. With this mode, SROUT signal is sent back to DRS from FPGA as SRIN to write the same value on the write shift register. So there is a small delay(~10ns) due to the routing (DRS->FPGA->DRS, page2). It seems SRIN signal is not stable around the falling edges of SRCLK, thus it could cause that unexpected values are written in write shifter register.

To understand the situation clearly, I'd like to know the answer to the above questions.

Thank you.

Best regards,

Seiya |

| Attachment 1: drs4_srin_srout_srclk.pdf

|

|

|

802

|

Tue Oct 27 15:02:09 2020 |

Seiya Nozaki | Timing diagram of SROUT/SRIN signal to write/read a write shift register | Dear Stefan,

Thank you for your reply.

SRIN is directly connected to SROUT via FPGA for now, but it is unstable for the timing between clock and SRIN depending on the firmware logic.

We want to make our system more robust, so we are thinking to use a clock with a lower frequency (let's say 16.6 MHz) or change the duty cycle of a clock to keep more time between the rising edge and falling edge of a clock. This change is just for reading/writing the write shift register, we will use a 33 MHz clock for the analog readout in any case.

If we change like above, are there any concerns from the DRS4 side?

Best,

Seiya

| Stefan Ritt wrote: |

|

Dear Seiya,

1) That's correct. SRIN is ampled at the falling edge. Pleae make sure to obey the hold-time as written in the datasheet. P.12, Fig. 11: SRIN must be stable before the falling edge of SRCLK and tH after the falling clock. tH is 5ns according to table 1.

2) The write shift register is a 8-bit shift register, with an input, output and clock. After the first clock pulse, the 7th bit is shown, after the second clock pulse the 6th bit and so on. You you need 8 clock pulses to read the whole register. At the same time you write to the register, so what ever is present at SRIN will replace the old 8 bits of that register.

3) No this is not possible. When you read the register, you write to it at the same time. One possibilty is to connect SROUT to SRIN during that (maybe via the FPGA). Then you have a circular register wich is the same after each 8 clock pulses.

For your reference, I posted a commercial D-Flip Flop (TI SNHCS72). The DRS4 write shift register is a simple array of 8 such registers, with no CLR or PRE, where SROUT is Q of the last Flip Flop.

Best,

Stefan

| Seiya Nozaki wrote: |

|

Dear Stefan,

I have questions about the timing diagram of SROUT/SRIN signal to write/read a write shift register.

1) Value of SRIN signal is saved at the falling edge of SRCLK, correct? (It is written in datasheet, page12, "Bits are latched into the shift register on the falling edge of SRCLK")

2) When are 8-bits of write shift register shown through SROUT? At ridging edges of SRCLK? and with additional delay(~10ns)? or falling edges?

3) In my understanding, when SRCLK is sent to DRS4, we can read and write the values in parallel, right? If so, is it possible just to read the registers without updating the registers?

[Background]

We have two modes to set the write shift register, the first one is to always reconnect to the first line and another one is to reconnect to the same line as when DWRITE goes to Low.

We can read/write the write shift register with the first mode (channel reset, page1). But we rarely face the problem of write shift register, unexpected values are written, with the second mode. With this mode, SROUT signal is sent back to DRS from FPGA as SRIN to write the same value on the write shift register. So there is a small delay(~10ns) due to the routing (DRS->FPGA->DRS, page2). It seems SRIN signal is not stable around the falling edges of SRCLK, thus it could cause that unexpected values are written in write shifter register.

To understand the situation clearly, I'd like to know the answer to the above questions.

Thank you.

Best regards,

Seiya

|

|

|

|

804

|

Wed Oct 28 04:32:19 2020 |

Seiya Nozaki | Timing diagram of SROUT/SRIN signal to write/read a write shift register | Dear Stefan,

OK, it's good to hear! Thank you!

Best,

Seiya

| Stefan Ritt wrote: |

|

This is a static shift register, so you can make the clock as slow as you want. Actually I don't use a "clock", I just use a data pin I control via a state machine in the VHDL code. This way I have more control over the edges. I need several (internal) clock cycles to produce one SRCLK clock cycle, but that does not matter for the DRS.

Stefan

| Seiya Nozaki wrote: |

|

Dear Stefan,

Thank you for your reply.

SRIN is directly connected to SROUT via FPGA for now, but it is unstable for the timing between clock and SRIN depending on the firmware logic.

We want to make our system more robust, so we are thinking to use a clock with a lower frequency (let's say 16.6 MHz) or change the duty cycle of a clock to keep more time between the rising edge and falling edge of a clock. This change is just for reading/writing the write shift register, we will use a 33 MHz clock for the analog readout in any case.

If we change like above, are there any concerns from the DRS4 side?

Best,

Seiya

| Stefan Ritt wrote: |

|

Dear Seiya,

1) That's correct. SRIN is ampled at the falling edge. Pleae make sure to obey the hold-time as written in the datasheet. P.12, Fig. 11: SRIN must be stable before the falling edge of SRCLK and tH after the falling clock. tH is 5ns according to table 1.

2) The write shift register is a 8-bit shift register, with an input, output and clock. After the first clock pulse, the 7th bit is shown, after the second clock pulse the 6th bit and so on. You you need 8 clock pulses to read the whole register. At the same time you write to the register, so what ever is present at SRIN will replace the old 8 bits of that register.

3) No this is not possible. When you read the register, you write to it at the same time. One possibilty is to connect SROUT to SRIN during that (maybe via the FPGA). Then you have a circular register wich is the same after each 8 clock pulses.

For your reference, I posted a commercial D-Flip Flop (TI SNHCS72). The DRS4 write shift register is a simple array of 8 such registers, with no CLR or PRE, where SROUT is Q of the last Flip Flop.

Best,

Stefan

| Seiya Nozaki wrote: |

|

Dear Stefan,

I have questions about the timing diagram of SROUT/SRIN signal to write/read a write shift register.

1) Value of SRIN signal is saved at the falling edge of SRCLK, correct? (It is written in datasheet, page12, "Bits are latched into the shift register on the falling edge of SRCLK")

2) When are 8-bits of write shift register shown through SROUT? At ridging edges of SRCLK? and with additional delay(~10ns)? or falling edges?

3) In my understanding, when SRCLK is sent to DRS4, we can read and write the values in parallel, right? If so, is it possible just to read the registers without updating the registers?

[Background]

We have two modes to set the write shift register, the first one is to always reconnect to the first line and another one is to reconnect to the same line as when DWRITE goes to Low.

We can read/write the write shift register with the first mode (channel reset, page1). But we rarely face the problem of write shift register, unexpected values are written, with the second mode. With this mode, SROUT signal is sent back to DRS from FPGA as SRIN to write the same value on the write shift register. So there is a small delay(~10ns) due to the routing (DRS->FPGA->DRS, page2). It seems SRIN signal is not stable around the falling edges of SRCLK, thus it could cause that unexpected values are written in write shifter register.

To understand the situation clearly, I'd like to know the answer to the above questions.

Thank you.

Best regards,

Seiya

|

|

|

|

|

|

894

|

Mon Oct 17 16:29:37 2022 |

Sebastian Infante | DRS4 installation via tar in ubuntu not working | Hello i cant install any the last versions that i downloaded from the dropbox, i can untar the file called drs-5.0.6 and when i type "make" while inside the extracted folder that starts working properly till a point and i get an error, its worth mention that i installed wxWidgets and could make a simple hello world that worked properly in wxWidgets.

The error that i get is the next one:

inlined from ‘bool ResponseCalibration::ReadCalibrationV4(unsigned int)’ at src/DRS.cpp:7224:35:

/usr/include/x86_64-linux-gnu/bits/string_fortified.h:95:34: warning: ‘char* __builtin___strncpy_chk(char*, const char*, long unsigned int, long unsigned int)’ specified bound depends on the length of the source argument [-Wstringop-truncation]

95 | return __builtin___strncpy_chk (__dest, __src, __len,

| ~~~~~~~~~~~~~~~~~~~~~~~~^~~~~~~~~~~~~~~~~~~~~~

96 | __glibc_objsize (__dest));

| ~~~~~~~~~~~~~~~~~~~~~~~~~

src/DRS.cpp: In member function ‘bool ResponseCalibration::ReadCalibrationV4(unsigned int)’:

src/DRS.cpp:4767:11: note: length computed here

4767 | strncpy(calibrationDirectoryPath, fCalibDirectory, strlen(fCalibDirectory));

| ~~~~~~~^~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

In file included from /usr/include/string.h:535,

from /usr/local/include/wx-3.3/wx/string.h:30,

from /usr/local/include/wx-3.3/wx/memory.h:15,

from /usr/local/include/wx-3.3/wx/object.h:19,

from /usr/local/include/wx-3.3/wx/wx.h:15,

from src/DRS.cpp:15:

In function ‘char* strncpy(char*, const char*, size_t)’,

inlined from ‘void DRSBoard::GetCalibrationDirectory(char*)’ at src/DRS.cpp:4767:11,

inlined from ‘bool ResponseCalibration::ReadCalibrationV3(unsigned int)’ at src/DRS.cpp:7066:35:

/usr/include/x86_64-linux-gnu/bits/string_fortified.h:95:34: warning: ‘char* __builtin___strncpy_chk(char*, const char*, long unsigned int, long unsigned int)’ specified bound depends on the length of the source argument [-Wstringop-truncation]

95 | return __builtin___strncpy_chk (__dest, __src, __len,

| ~~~~~~~~~~~~~~~~~~~~~~~~^~~~~~~~~~~~~~~~~~~~~~

96 | __glibc_objsize (__dest));

| ~~~~~~~~~~~~~~~~~~~~~~~~~

src/DRS.cpp: In member function ‘bool ResponseCalibration::ReadCalibrationV3(unsigned int)’:

src/DRS.cpp:4767:11: note: length computed here

4767 | strncpy(calibrationDirectoryPath, fCalibDirectory, strlen(fCalibDirectory));

| ~~~~~~~^~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

g++ -g -O2 -Wall -Wuninitialized -fno-strict-aliasing -Iinclude -I/usr/local/include -DOS_LINUX -DHAVE_USB -DHAVE_LIBUSB10 -DUSE_DRS_MUTEX -I/usr/local/lib/wx/include/gtk3-unicode-3.3 -I/usr/local/include/wx-3.3 -D_FILE_OFFSET_BITS=64 -DWXUSINGDLL -D__WXGTK__ -pthread -c src/averager.cpp

g++ -g -O2 -Wall -Wuninitialized -fno-strict-aliasing -Iinclude -I/usr/local/include -DOS_LINUX -DHAVE_USB -DHAVE_LIBUSB10 -DUSE_DRS_MUTEX -I/usr/local/lib/wx/include/gtk3-unicode-3.3 -I/usr/local/include/wx-3.3 -D_FILE_OFFSET_BITS=64 -DWXUSINGDLL -D__WXGTK__ -pthread -c src/ConfigDialog.cpp

In file included from include/DRSOscInc.h:25,

from src/ConfigDialog.cpp:7:

include/DOFrame.h: In member function ‘bool DOFrame::GetRefclk()’:

include/DOFrame.h:111:46: error: ordered comparison of pointer with integer zero (‘bool*’ and ‘int’)

111 | bool GetRefclk() { return m_refClk > 0; }

| ~~~~~~~~~^~~

make: *** [Makefile:81: ConfigDialog.o] Error 1

|

|