| ID |

Date |

Author |

Subject |

|

689

|

Sun May 6 08:13:37 2018 |

chen wenjun | confusion about the description in drs.cpp | Hi Stefan:

I'm still confused that althought the 8 bits buffer is enough,the FPGA receive the command through the uc_data_i register which is 16 bits wides.As we can see in the firmware, the locbus_addr is 32 bits wides. Does it means the locbus_addr[31:8] are always '0' because the address in buffer is only 8 bits. Does it means the usrbus_status_sel and usrbus_ram_sel are also '0' all the time .

thanks!

chen

| Stefan Ritt wrote: |

|

The FPGA is very small, so it only has an address space of 256 bytes. Look at the definition in DRS.cpp

#define USB_CTRL_OFFSET 0x00 /* all registers 32 bit */

#define USB_STATUS_OFFSET 0x40

#define USB_RAM_OFFSET 0x80

The registers are 32 bits wide, but the addresses only run from 0 to 255, and thus a single byte is enough for addressing them.

| chen wenjun wrote: |

|

Hi,Stefan:

recently,whtn I study the drs.cpp code ,I found that the buffer[1] is char but the addr and the base_addr are all unsigned int,isn't there any problem that the addr may be cut off to 8 bits? Also ,I found that the data fpga recieved from the usb is 16 bits,so how can fpga get the true 32bits address from the PC.

|

|

|

|

533

|

Mon Aug 29 09:36:34 2016 |

benjamin legeyt | increment write config register on the fly? | Hello,

I have a question about using the write config register to enable/disable sampling on the fly. I am looking to instrument an experiment at EPFL where multiple short events need to be captured during a 20us period followed by an 80us quiet period during which we could read out the chip. Would it be possible to start an acquisition with all channels seeing the same signal and the write config register set to 111111111 and then shift a zero into the write config reg after each event is detected to freeze the channels in time one-by-one? In this way we could measure up to 8 different events during the active period and then read them all out together during the quiet period. I have read the posts about the simultaneous read-write mode and the issue with waveforms stopping at cell 767. not knowing the exact details of what causes this issue I wonder if it would effect this sort of operation? Also, I would like to know if dwrite must be de-asserted while the write config register is being updated or if it could be done while the sampling is active? The latter would obviously be preferable as we would not incur any dead-time during the active period.

Thanks in advance for the information,

Benjamin LeGeyt |

|

535

|

Mon Aug 29 12:18:49 2016 |

benjamin legeyt | increment write config register on the fly? | If I may trouble you for a little more information, the critical point then is that there should not be any zeroes in the write config register while the sampling is active? In case it was unclear I would only be reading out once sampling was stopped (dwrite = 0).

As for the readout, I know that I would have to read out all 1024 samples each time, and keep track of where each channel stopped in the FPGA. I would never know the exact cell where sampling stopped but I hoped that if I discard some number of cells on each side of the expected stopping point that I would be OK.

Thanks again

| Stefan Ritt wrote: |

|

The issue with "stopping at cell 767" would also affect this mode of operation. Furthermore, the DRS4 chip has only 10 bit register which records in which cell the event has occured, and where the readout must be started. If you record 8 separate events, you don't know where to start the readout.

The DRS5 chip will have all this possibilitied, but unfortunately it won't be ready before 2-3 years from now.

Stefan

| benjamin legeyt wrote: |

|

Hello,

I have a question about using the write config register to enable/disable sampling on the fly. I am looking to instrument an experiment at EPFL where multiple short events need to be captured during a 20us period followed by an 80us quiet period during which we could read out the chip. Would it be possible to start an acquisition with all channels seeing the same signal and the write config register set to 111111111 and then shift a zero into the write config reg after each event is detected to freeze the channels in time one-by-one? In this way we could measure up to 8 different events during the active period and then read them all out together during the quiet period. I have read the posts about the simultaneous read-write mode and the issue with waveforms stopping at cell 767. not knowing the exact details of what causes this issue I wonder if it would effect this sort of operation? Also, I would like to know if dwrite must be de-asserted while the write config register is being updated or if it could be done while the sampling is active? The latter would obviously be preferable as we would not incur any dead-time during the active period.

Thanks in advance for the information,

Benjamin LeGeyt

|

|

|

|

276

|

Tue Jul 23 22:31:08 2013 |

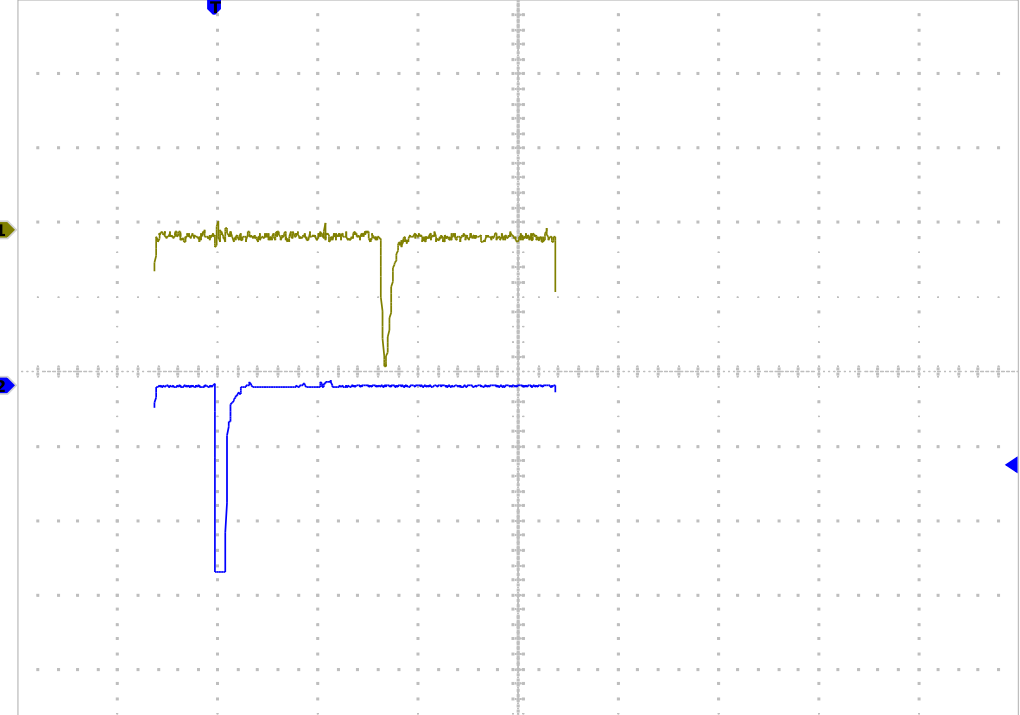

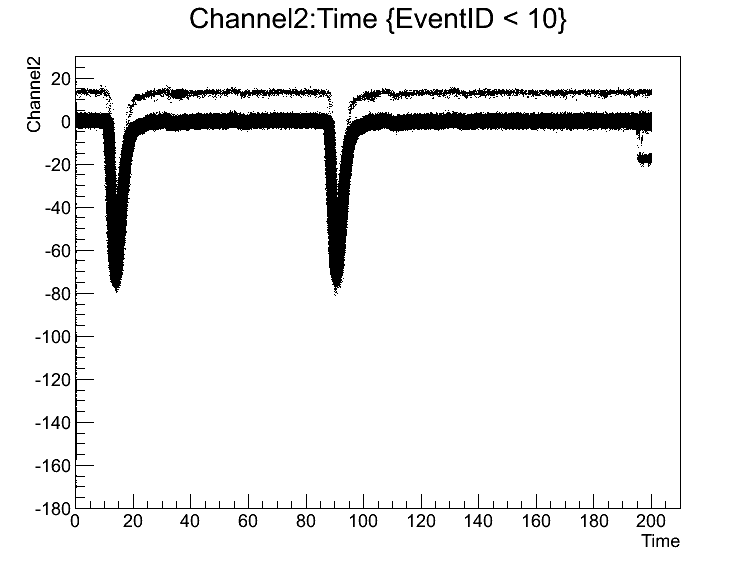

alonzi | Evaluation Board Behavior | Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion. |

| Attachment 1: Screenshot.png

|

|

| Attachment 2: data_problem.png

|

|

|

278

|

Tue Jul 23 22:42:31 2013 |

alonzi | Evaluation Board Behavior |

| Stefan Ritt wrote: |

|

| alonzi wrote: |

|

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion.

|

Actually the first and last sample are even more off the baseline, so I cut them out in software in the DRSOscilloscope. So actually the chip has only 1022 "usable" cells. It might happen in some rare cases that more cells are affected, although I have not yet seen this (maybe I did not look close enough). So I propose that you cut out one more bin at the beginning and the end, so a total of 1020 cells, and you should be fine.

/Stefan

|

Thanks for the quick reply. Our quick fix was to do just that. |

|

29

|

Wed Dec 30 14:28:33 2009 |

aliyilmaz | normal_mode_in_drs_exam.cpp | Dear Mr. S. Ritt

i am Ms. student , am working with your DRS4 board to calculate the time of flight of the cosmic particle which passes trough the hodoscope . i see the signals at scope , which is negative (i don't want to take positive side of the signal).

i am using your drs_exap.cpp file to take the data, i set the analog trigger source , threshold level is negative, like this(b->SetTriggerLevel(-30, true) ); but the exam file also registers the positive side of signal (i think that is spike or internal reflection), is it possible to eliminate this spike? Also i want to register the data just after the threshold value, but that is always triggered, i think that caused from the mode. Is it possible to set the trigger mode to normal in exam file?,and how can i do that?

Best regards.

Sincerely,

Ali YILMAZ (ali.yilmaz@roma1.infn.it)

|

|

136

|

Mon Oct 31 09:15:02 2011 |

Zhongwei Du | How to link PMT | I want to measure the signal from PMT . But it is a current signal, should i just put a series resistance, or use a amplifier to convert it to voltage signal before drs4?

Can you give me some advice ? |

|

151

|

Sat Feb 4 11:59:26 2012 |

Zhongwei Du | what sort of detectors for physical experiment the DRS4 used? | Hello.

We are designing a waveform sampling board for Si strip array detector ,whose rise time is less than 10 ns, which makes we doubt whether the DRS4 can do more accurate than traditional charge integral circuit for charge measuring.

So we need to know what sort of detectors for physical experiment the DRS4 has been used in?

Can you give me some information? For example, Si strip array detector or CsI scintillator r ball detector ? PMT or APD ? |

|

200

|

Tue Dec 4 09:24:22 2012 |

Zhongwei Du | Question of drs4 using | When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now. |

|

202

|

Tue Dec 4 09:50:11 2012 |

Zhongwei Du | Question of drs4 using |

| Stefan Ritt wrote: |

|

| Zhongwei Du wrote: |

|

When Denable and Dwrite is high , the voltage of PLLOUT is 0 V. And the Dtap is turn high with no delay when the Denable turns high.

After power up and configuration(the WSR,WCR,CR are all set to 11111111), the readout data is no change whenever the input analog signal and rofs,bias,oofs changes. I have test useing the DAC to supply the Dspeed voltage, and change a new DRS4 chip, but all is the same. The readout data is strange : the first about 100 cells is rise or fall and the last 900 cells is out of the range of ADC.

So how should I do for debugging the drs4 now.

|

The first thing to make work is to have DTAP oscillating with fsamp/2048. Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. If not, double check all supply voltages, and especially all soldering points. The QFN package is a bit hard to solder.

/Stefan

|

"Keep Denable and Dwrite low (required during power-on, see elog:10), set Dspeed to 2.5V, then rise Denable and Dwrite. You should see Dtap toggling at about 2.4 MHz. "

In this process , should i config any registers( WSR,WCR,CR ) ? |

|

175

|

Tue Aug 28 17:52:45 2012 |

Zach Miller | DRS-4.0.0 DOScreen.cpp | Hi,

I found an old thread regarding a fix for DOScreen.cpp for DRS-3.1.0, that fixes an "ambiguous overload problem." Currently when I attempt to build the drs-4.0.0, I get this similar error:

src/DOScreen.cpp:332:39: error: call of overloaded ‘Append(int)’ is ambiguous

This section of code is different than what the previous thread was correcting, and though I attempted to apply the logic of the old thread, I haven't fixed this yet.

The following is the code for that section:

-----

329 for (int i=0 ; i<5 ; i++)

330 if (tc & (1<<(i+8))) {

331 if (i < 4)

332 wxst1.Append(wxT('1'+i));

333 else

334 wxst1.Append(wxT('E'));

335 wxst1.Append(wxT('&'));

336 }

337 if (wxst1.Length() > 0)

338 wxst1 = wxst1.Left(wxst1.Length()-1);

339 wxst1.Append(wxT(')'));

------

I've attempted a few fixes, but unfortunately, my understanding of the code is not great, and I haven't managed to fix this yet. Any help would be appreciated.

Thanks,

Zach Miller |

|

177

|

Wed Aug 29 16:42:42 2012 |

Zach Miller | DRS-4.0.0 DOScreen.cpp |

| Stefan Ritt wrote: |

|

| Zach Miller wrote: |

|

Hi,

I found an old thread regarding a fix for DOScreen.cpp for DRS-3.1.0, that fixes an "ambiguous overload problem." Currently when I attempt to build the drs-4.0.0, I get this similar error:

src/DOScreen.cpp:332:39: error: call of overloaded ‘Append(int)’ is ambiguous

This section of code is different than what the previous thread was correcting, and though I attempted to apply the logic of the old thread, I haven't fixed this yet.

The following is the code for that section:

-----

329 for (int i=0 ; i<5 ; i++)

330 if (tc & (1<<(i+8))) {

331 if (i < 4)

332 wxst1.Append(wxT('1'+i));

333 else

334 wxst1.Append(wxT('E'));

335 wxst1.Append(wxT('&'));

336 }

337 if (wxst1.Length() > 0)

338 wxst1 = wxst1.Left(wxst1.Length()-1);

339 wxst1.Append(wxT(')'));

------

I've attempted a few fixes, but unfortunately, my understanding of the code is not great, and I haven't managed to fix this yet. Any help would be appreciated.

Thanks,

Zach Miller

|

Just put (char) in front of wxT(...), like

if (tc > 0) {

wxString wxst1, wxst2;

wxst1.Append((char)wxT('('));

for (int i=0 ; i<5 ; i++)

if (tc & (1<<i)) {

if (i < 4)

wxst1.Append((char) (wxT('1'+i)));

else

wxst1.Append((char) wxT('E'));

wxst1.Append((char) wxT('|'));

}

for (int i=0 ; i<5 ; i++)

if (tc & (1<<(i+8))) {

if (i < 4)

wxst1.Append((char) (wxT('1'+i)));

else

wxst1.Append((char) wxT('E'));

wxst1.Append((char) wxT('&'));

}

if (wxst1.Length() > 0)

wxst1 = wxst1.Left(wxst1.Length()-1);

wxst1.Append((char) wxT(')'));

|

Hi Stefan,

Thanks for the response. I have tried that and it fixes all the lines except the ones that have:

wxst1.Append((char) (wxT('1'+i)));

Those lines still don't compile for me. I've also tried: wxst1.Append((char) (wxT('1'+(char)i))); and wxst1.Append((char) (wxT((char)'1'+i))); as well as a few other combinations of (char) and Append.

I get the same error of: "Call of overloaded "Append(int)" is ambiguous."

Any other help would be greatly appreciated. Thanks!

-Zach |

|

179

|

Wed Aug 29 16:57:49 2012 |

Zach Miller | DRS-4.0.0 DOScreen.cpp |

| Stefan Ritt wrote: |

|

| Zach Miller wrote: |

|

| Stefan Ritt wrote: |

|

| Zach Miller wrote: |

|

Hi,

I found an old thread regarding a fix for DOScreen.cpp for DRS-3.1.0, that fixes an "ambiguous overload problem." Currently when I attempt to build the drs-4.0.0, I get this similar error:

src/DOScreen.cpp:332:39: error: call of overloaded ‘Append(int)’ is ambiguous

This section of code is different than what the previous thread was correcting, and though I attempted to apply the logic of the old thread, I haven't fixed this yet.

The following is the code for that section:

-----

329 for (int i=0 ; i<5 ; i++)

330 if (tc & (1<<(i+8))) {

331 if (i < 4)

332 wxst1.Append(wxT('1'+i));

333 else

334 wxst1.Append(wxT('E'));

335 wxst1.Append(wxT('&'));

336 }

337 if (wxst1.Length() > 0)

338 wxst1 = wxst1.Left(wxst1.Length()-1);

339 wxst1.Append(wxT(')'));

------

I've attempted a few fixes, but unfortunately, my understanding of the code is not great, and I haven't managed to fix this yet. Any help would be appreciated.

Thanks,

Zach Miller

|

Just put (char) in front of wxT(...), like

if (tc > 0) {

wxString wxst1, wxst2;

wxst1.Append((char)wxT('('));

for (int i=0 ; i<5 ; i++)

if (tc & (1<<i)) {

if (i < 4)

wxst1.Append((char) (wxT('1'+i)));

else

wxst1.Append((char) wxT('E'));

wxst1.Append((char) wxT('|'));

}

for (int i=0 ; i<5 ; i++)

if (tc & (1<<(i+8))) {

if (i < 4)

wxst1.Append((char) (wxT('1'+i)));

else

wxst1.Append((char) wxT('E'));

wxst1.Append((char) wxT('&'));

}

if (wxst1.Length() > 0)

wxst1 = wxst1.Left(wxst1.Length()-1);

wxst1.Append((char) wxT(')'));

|

Hi Stefan,

Thanks for the response. I have tried that and it fixes all the lines except the ones that have:

wxst1.Append((char) (wxT('1'+i)));

Those lines still don't compile for me. I've also tried: wxst1.Append((char) (wxT('1'+(char)i))); and wxst1.Append((char) (wxT((char)'1'+i))); as well as a few other combinations of (char) and Append.

I get the same error of: "Call of overloaded "Append(int)" is ambiguous."

Any other help would be greatly appreciated. Thanks!

-Zach

|

wxst1.Append((char) (wxT((char)('1'+i)))); maybe ???

|

Aha!

wxst1.Append((char) (wxT('1'+i)));

That one actually works as you initially thought, but you my editor was being picky of (char)wxt... instead of (char) (wxt....). For some reason, it has to have the extra set of parentheses around wxt(). Thank You! |

|

180

|

Thu Oct 4 20:50:36 2012 |

Zach Miller | DRS5 | Hi,

Our group had previously heard that a "DRS-5.0" might be on the horizon and that it may have ethernet capabilities as well as 16-input channels (we heard this when ordering the DRS-4). Is this still in the works and accurate information? If so, is there a rough estimate to the "release date?"

Thanks for your time,

Zach Miller |

|

182

|

Thu Oct 4 21:07:27 2012 |

Zach Miller | DRS5 |

| Stefan Ritt wrote: |

|

| Zach Miller wrote: |

|

Hi,

Our group had previously heard that a "DRS-5.0" might be on the horizon and that it may have ethernet capabilities as well as 16-input channels (we heard this when ordering the DRS-4). Is this still in the works and accurate information? If so, is there a rough estimate to the "release date?"

Thanks for your time,

Zach Miller

|

You mix up two things: The DRS5 chip is a new device with improved samling speed (10 GSPS) and lower dead time. This chip might come in 2-3 years. The 16-input board you mentioned is a DAQ board based on the DRS4 chip. This board well be operational beginning of 2013 as a prototype. It is not clear however at this point in which way this board will be made available for public. Maybe we will license this to industry. The design is however pretty much defined: 16 channels with gain 0.1-100, 1 GHz Bandwidth, Gigabit Ethernet output, and multi-board capabilities. Trigger on each channel with logical combinations. 80 MSPS continuous sampling (in addition to the DRS4 sampling). Each channel can be biased 0-210 V for SiPMT or APD power. A 19" 3 HE crate will host 16 boards with 256 channels.

/Stefan

|

Thanks, Stefan. That was the information we were looking for.

Cheers.

-Zach |

|

358

|

Mon Jul 14 19:03:05 2014 |

Yves Bianga | change cascading from 1024 to 2048 bins for each input channel | Hello,

I want to ask whether it is possible to modify a Evaluation Board 5.0 from 1024 to 2048 cells for each of the 4 input channels.

On the rev50 manual at page 31 I found an option to connect the 4 unused channels by setting 8 solder bridges.

The source code for controlling the board seems already prepared for 2048 bins, since version 5.0.2.

So my first question: Are there any implementations in the VHDL Code to control the write shift register in 2048 mode? / Is there a necessity for a newer/other VHDL Code or is it already implemented?

And the second: Are there any other modifications except the eight zero Ohm resistors and maybe changes in the FPGA code?

My board info output:

Mezz. Board index: 0

DRS type: DRS4

Board type: 9

Serial number: 2451

Firmware revision: 21260

Thanks a lot!

Yves Bianga |

|

628

|

Sun Aug 27 12:44:16 2017 |

Yuvaraj Elangovan | DRS4 version Support | Hi i am using DRS4 Eval Board V2, How to acquire data to a bin file using it. |

|

219

|

Fri Feb 22 11:46:17 2013 |

Yury Golod | DRS4 trigger, different polarity |

I need to synchronize two signals. These signals have a different polarity.

I can set triggers on different levels. But I can't set different polarity of triggers.

Now I can set (T1 and T2), I need to set (T1 and (not T2))

Is it possible?

d->SetTriggerLevel(-0.4,0.4,0.0,0.0,false);

d->EnableTrigger(1, 0); // Enable trigger

d->SetTriggerSource(1<<8 | 1<<9); // T1 and T2

file DRS.cpp:

int DRSBoard::SetTriggerLevel(double voltage1,double voltage2, double voltage3,double voltage4,bool negative)

{

…

SetDAC(fDAC_TLEVEL1, voltage1/2 + 0.8);

SetDAC(fDAC_TLEVEL2, voltage2/2 + 0.8);

…

|

|

153

|

Wed Feb 15 18:08:13 2012 |

Yuji Iwai | Evaluation Board v4 Trigger/Clock Connectors | Quick question - what type of connectors are used for the trigger and clock in/out on the v4 eval board? |

|

523

|

Thu May 12 05:18:47 2016 |

Yu | Problem For Software Download | Hi

I can't download the software for windows on this website 'www.psi.ch/drs/software-download', there is some mistake when i click on download.

If convenient, can you send the software Version 5.0.5 for windows to me? My E-mail address is 'yuhaiyang421@163.com'. Thank you!

Best Regards

Yu |

|