| ID |

Date |

Author |

Subject |

|

629

|

Wed Sep 27 16:11:03 2017 |

Yoni Sher | Event acquisition pace for irregular timing | Hi,

I'm running a LIDAR application that requires that every outgoing pulse be captured. My current setup firess sets of 20-50 pulses at 1 ms intervals, about 10 times a second, but only 10-20 pulses a second are captured.

When I fire at full speed (1KHz - one pulse every ms), about 500-600 pulses a second are captured.

At the moment, I'm triggering on channel 1 and captureing the data on channel 2. Would it help if I used the external trigger? Is there anything else I can do?

Yoni |

|

647

|

Wed Dec 20 15:30:38 2017 |

Yoni Sher | cascading -- DRS4 Osci.cpp & DRS.cpp | Hi,

I'm trying to do the same thing (get 1 channel with 8192 bins), but I'm having some trouble with it. When I call SetChannelConfig(0, 8, 1) as suggeted, I get output that looks like noise on all readouts. Could you please explain what is supposed to happen in this case?

I will happily write the code to combine the channels correctly (and debug it) if I can understand what needs to be done.

(I should mention that my primary concern is a MATLAB interface which I have already written and don't mind sharing when it's complete).

Yoni Sher

| Stefan Ritt wrote: |

|

| Jill Russek wrote: |

|

| Stefan Ritt wrote: |

|

| Jill Russek wrote: |

|

Stefan, thanks for your help so far. If I go with your plan A of just modifying drs_exam.cpp, is there a quick way to get it to save the data from the wave, like how osci.cpp spits out an xml file? (Ignoring the cascading aspect for now)

Thanks again :)

/Jill

|

Well, you have to learn C programming, I won't do it for you. drs_exam.cpp contains already code to write to the ASCII file data.txt, so you just can use that or modify it to your needs.

/Stefan

|

Ha! So then the answer is no, there isn't a ready made function/method to pull out the timing and voltage, like how it was done in osci.cpp. That's all I wanted to know. (Not whether you would write it for me! Only trying to save time!) Thanks!

/Jill

|

You misunderstood. The answer is yes. drs_exam.cpp contains already code to write to an ASCII file. If you actually look into the file, you see:

f = fopen("data.txt", "w");

...

b->GetTime(0, b->GetTriggerCell(0), time_array);

...

b->GetWave(0, 0, wave_array[0]);

...

fprintf(f, "%5.2f %6.2f\n", time_array[i], wave_array[0][i]);

which actually pulls out the timing and voltage and writes it to the file.

|

|

|

649

|

Wed Dec 20 16:30:45 2017 |

Yoni Sher | cascading -- DRS4 Osci.cpp & DRS.cpp | Hi,

The board is modified (and checks out with the DRSScope program). Could you please point me to the drs_exam_2048.cpp file? I can't seem to fine the most up-to-date git repository....

Thanks,

Yoni

| Stefan Ritt wrote: |

|

First you need a board which is modified in hardware to support channel cascading. Basically there are internal resistors which connect each input connector to two channels. You have to specify this when you order the board. Then you can use the new drs_exam_2048.cpp file contains in the git repository which correctly configures and reads out the board in two-channel cascading mode. Putting all 8 channels together is not supported by the evaluation boards.

Stefan

| Yoni Sher wrote: |

|

Hi,

I'm trying to do the same thing (get 1 channel with 8192 bins), but I'm having some trouble with it. When I call SetChannelConfig(0, 8, 1) as suggeted, I get output that looks like noise on all readouts. Could you please explain what is supposed to happen in this case?

I will happily write the code to combine the channels correctly (and debug it) if I can understand what needs to be done.

(I should mention that my primary concern is a MATLAB interface which I have already written and don't mind sharing when it's complete).

Yoni Sher

| Stefan Ritt wrote: |

|

| Jill Russek wrote: |

|

| Stefan Ritt wrote: |

|

| Jill Russek wrote: |

|

Stefan, thanks for your help so far. If I go with your plan A of just modifying drs_exam.cpp, is there a quick way to get it to save the data from the wave, like how osci.cpp spits out an xml file? (Ignoring the cascading aspect for now)

Thanks again :)

/Jill

|

Well, you have to learn C programming, I won't do it for you. drs_exam.cpp contains already code to write to the ASCII file data.txt, so you just can use that or modify it to your needs.

/Stefan

|

Ha! So then the answer is no, there isn't a ready made function/method to pull out the timing and voltage, like how it was done in osci.cpp. That's all I wanted to know. (Not whether you would write it for me! Only trying to save time!) Thanks!

/Jill

|

You misunderstood. The answer is yes. drs_exam.cpp contains already code to write to an ASCII file. If you actually look into the file, you see:

f = fopen("data.txt", "w");

...

b->GetTime(0, b->GetTriggerCell(0), time_array);

...

b->GetWave(0, 0, wave_array[0]);

...

fprintf(f, "%5.2f %6.2f\n", time_array[i], wave_array[0][i]);

which actually pulls out the timing and voltage and writes it to the file.

|

|

|

|

|

706

|

Thu Jun 28 19:55:45 2018 |

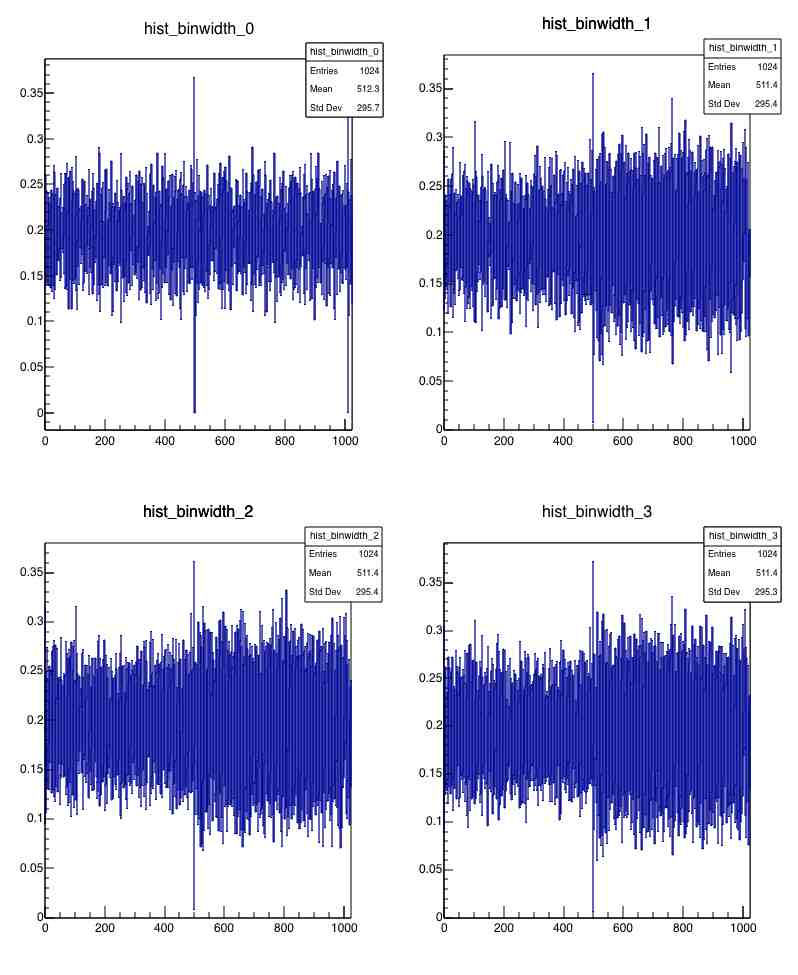

Woon-Seng Choong | Negative Bin Width | I am using a DRS4 Evaluation Board v5 and running the drsosc.exe version 5.06 on a Window 7 machine. I have performed the voltage and timing calibration.

With test pulses on channel 1 and 2, I collected binary data file with all 4 channels active sampling at 5GSPS.

Attached is a distribution of the bin_width vs. cell # for all the 4 channels. Note that there are few cells with bin_width < 10 ps.

Channel 1: bin_width[498] = -0.000348, bin_width[1010]= -0.000348

Channel 2: bin_width[498] = 0.007363

Channel 3: bin_width[498] = 0.007843

Channel 4: bin_width[498] = 0.005948

Is this normal? How can you get negative bin_width? What does negative bin_width means?

I have attached the binary data file for your verification.

|

| Attachment 1: bin_width_5gsps.jpg

|

|

| Attachment 2: test5gsps.dat

|

|

708

|

Mon Jul 16 19:39:35 2018 |

Woon-Seng Choong | Effect of interpolation on timing | Using a test pulse split into two channels of the DRS4 Evaluation Board v5, I looked at the time resolution using a leading edge threshold. The voltage and timing calibration was performed. One method (1) is to linearly interpolate between two points of the raw waveform that is above and below the threshold (this is exactly the algorithm given in read_binary.c in the drs4 source distribution); and another (2) is to use a cubic spline interpolation of the raw waveform. The results I obtained are:

Method 1: dt = 1.298 ns +/- 7.22 ps

Method 2: dt = 1.293 ns +/- 15.48 ps

I am really puzzled why the time resolution of the spline interpolation is about a factor 2 worse than the simple linear interpolation. Has anyone studied the time resolution using similar or other interpolation methods?

|

|

709

|

Fri Jul 20 00:44:13 2018 |

Woon-Seng Choong | Effect of interpolation on timing | Just a follow-up update.

It turns out that I was using a cubic spline interpolation with smoothing. If I required the cubic spline to go through the sampled points, then I obtained similar time resolution as the simple linear interpolation.

| Woon-Seng Choong wrote: |

|

Using a test pulse split into two channels of the DRS4 Evaluation Board v5, I looked at the time resolution using a leading edge threshold. The voltage and timing calibration was performed. One method (1) is to linearly interpolate between two points of the raw waveform that is above and below the threshold (this is exactly the algorithm given in read_binary.c in the drs4 source distribution); and another (2) is to use a cubic spline interpolation of the raw waveform. The results I obtained are:

Method 1: dt = 1.298 ns +/- 7.22 ps

Method 2: dt = 1.293 ns +/- 15.48 ps

I am really puzzled why the time resolution of the spline interpolation is about a factor 2 worse than the simple linear interpolation. Has anyone studied the time resolution using similar or other interpolation methods?

|

|

|

746

|

Wed Mar 6 10:09:01 2019 |

Willy Chang | drscl "no board found" in some Win7 or Win8.X PCs | Hi all,

When connecting the board and running the Zadig program, some Windows PCs may return "driver installation failed." I coudn't find the solution from their download website. So I started the drscl first. Apparently it shows: Successfully scanned, but no boards found. Therefore I checked the Device Manager. A breakdown warning triangle appears under the serial port...

The possible solution may be found here.

Infact, the WinUsb driver has been in existence in your PC. One can just follow the instructions here:

https://docs.microsoft.com/en-us/windows-hardware/drivers/usbcon/winusb-installation

- Plug in your device to the host system.

- Open Device Manager and locate the device.

- Right-click the device and select Update driver software... from the context menu.

- In the wizard, select Browse my computer for driver software.

- Select Let me pick from a list of device drivers on my computer.

- From the list of device classes, select Universal Serial Bus devices.

- The wizard displays WinUsb Device. Select it to load the driver.

In the wizard, somehow the default setting displays Microsoft Device on the Top of the list and replaced the WinUsb Device. You can easily re-load the WinUsb Device. Just ignore the WARNING from the device manager. The board should work fine now.

Willy |

|

447

|

Tue Nov 3 22:37:56 2015 |

Will Flanagan | Latest macro for DRS4 V5 | Hi DRS4 Experts,

I have an extremely naive question: Is there any official macro to unpack the DRS4 binary files? All I am looking to do is to plot a few of my waveforms and manipulate them in root. I am using OSX 10.10 and ROOT 5.34.

Thanks in advance,

Will |

|

448

|

Tue Nov 3 23:15:38 2015 |

Will Flanagan | Latest macro for DRS4 V5 | I should of course mention that I looked through the DRS4 website and didn't see anything obvious: https://www.psi.ch/drs/evaluation-board

Thanks,

Will

| Will Flanagan wrote: |

|

Hi DRS4 Experts,

I have an extremely naive question: Is there any official macro to unpack the DRS4 binary files? All I am looking to do is to plot a few of my waveforms and manipulate them in root. I am using OSX 10.10 and ROOT 5.34.

Thanks in advance,

Will

|

|

|

450

|

Thu Nov 5 00:18:42 2015 |

Will Flanagan | Latest macro for DRS4 V5 | Hi Stefan,

This is absolutely perfect.

Thanks,

Will

| Stefan Ritt wrote: |

|

Have a look here: elog:361

| Will Flanagan wrote: |

|

Hi DRS4 Experts,

I have an extremely naive question: Is there any official macro to unpack the DRS4 binary files? All I am looking to do is to plot a few of my waveforms and manipulate them in root. I am using OSX 10.10 and ROOT 5.34.

Thanks in advance,

Will

|

|

|

|

539

|

Wed Oct 5 22:43:29 2016 |

Will Flanagan | Timestamp for each DRS4 waveform | Hi DRS4 Experts,

I have been analyzing DRS4 binary data with scripts based on Stefan's (very helpful!) macro:

https://midas.psi.ch/elogs/DRS4+Forum/361

I would now like to look at the stability of my waveforms over a long period of time. In order to do this, I would need a timestamp encoded with each waveform. Are there timestamps within default DRS4 binary data? If so, does anyone have sample code for extracting them?

Best Regards,

Will |

|

541

|

Thu Oct 6 15:23:18 2016 |

Will Flanagan | | Hi Stefan,

That is exactly what I'm looking for. Thanks again!

Will |

|

668

|

Wed Mar 14 00:38:15 2018 |

Will Flanagan | sub-ms precision timestamps? | Dear DRS4 community,

Is there a way to extract timestamps with sub-ms precision? The milliseconds of an event is clearly given when unpacking the header. I would like to determine how far apart events are when they are within the same millisecond.

Thanks,

Will |

|

336

|

Wed Apr 16 03:22:43 2014 |

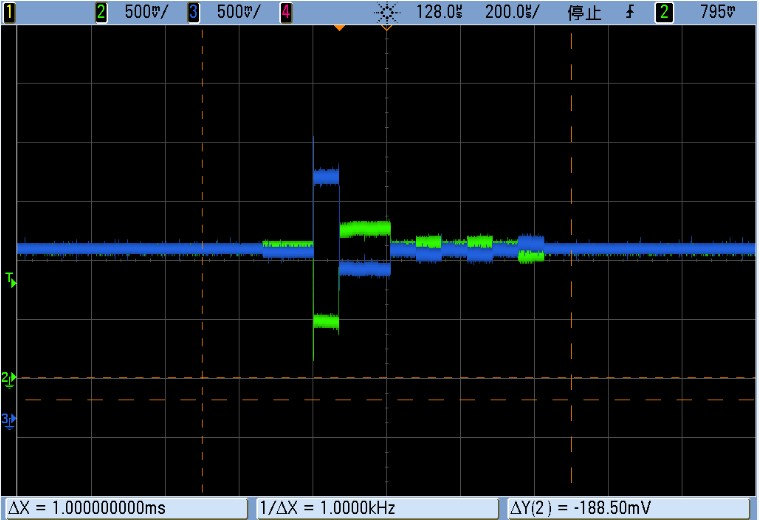

Wang | why is the first channel output error? | Hi,

The diagram below is DRS4 output. Green is the output8+, blue is the output8-. Output8+ of the first channel is below the baseline. It is not right.

Others channel is suitable. I check the circuit , Hardware is no problem, so I want to konw where the FPGA code is wrong. what reason is caused? Thanks! |

| Attachment 1: QQ??20140416090124.jpg

|

|

|

340

|

Thu Apr 17 12:02:28 2014 |

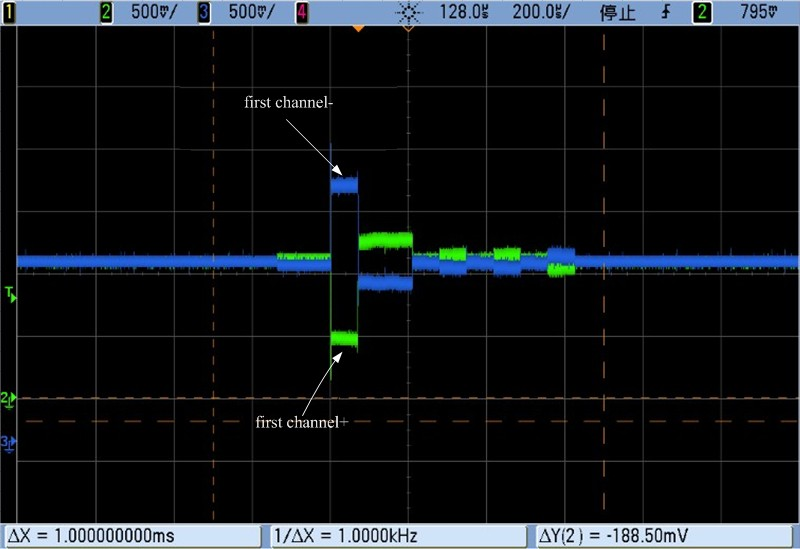

Wang | The first channel is wrong. | Hi,

I want to describe this phenomenon again. The diagram below is DRS4 output. There is no input signal. Green is the output8+, blue is the output8-. Output8+ of the first channel is below the baseline. The output is saturation when input ADC. It is not right, and what is it in front of the first channel? It seemed there are two channels. Others channel is suitable. I check the circuit , Hardware is no problem, so I want to konw where the FPGA code is wrong. What reason is caused? Can anyone help me to solve the problem? Thanks! |

| Attachment 1: QQ??20140417174309.jpg

|

|

|

625

|

Thu Jul 20 13:00:44 2017 |

Volodymyr Rodin | Driver installation on Windows 10 | Dear Laura

You need to disable driver signature enforcement. Then try again with path option.

It helped me.

http://www.drivethelife.com/windows-drivers/how-to-disable-driver-signature-enforcement-on-windows-10-8-7-xp-vista.html

Best regards,

Volodymyr

| Laura Gonella wrote: |

|

Hello,

I am trying to get a DRS4 board to run on Windows 10. I am having problems with the driver installation. I am getting the follwoing message

"There is no driver selected for the device information set or element"

I had specified the path to look for the driver as C:\ProgramFilesx86\DRS\driver\. I also tried the option to look online for the driver. None works. Can anyone help?

Thanks,

Laura

|

|

|

626

|

Fri Jul 21 09:16:02 2017 |

Volodymyr Rodin | Time output | Hello Stefan

I tried to convert binary to a simple txt file and found next problem - strange time output.

Here is output from little modification for read_binary.cpp (Its last output line also is strange: dT = -1.#IOns +- -1.$ps)

Found data for board #0

Found timing calibration for channel #1

Found boards# 1

event channel waveform time point

1 0 -0.000092 0.000000 0

1 0 0.030548 0.000000 1

1 0 0.059418 0.000000 2

1 0 0.080200 0.000000 3

1 0 0.094223 0.000000 4

1 0 0.097702 0.000000 5

1 0 0.094055 0.000000 6

1 0 0.079117 0.000000 7

1 0 0.060364 0.000000 8

1 0 0.030960 0.000000 9

1 0 0.000504 0.000000 10

1 0 -0.031555 0.000000 11

1 0 -0.057465 0.000000 12

1 0 -0.080536 0.000000 13

1 0 -0.095413 0.000000 14

1 0 -0.099365 0.000000 15

I used output string in the following places, but it didn't help:

// reach channel data

:for (i=0 ; i<1024 ; i++) {

// convert data to volts

waveform[0][chn_index][i] = (voltage[i] / 65536. + eh.range/1000.0 - 0.5);

// calculate time for this cell

for (j=0,time[b][chn_index][i]=0 ; j<i ; j++)

time[b][chn_index][i] += bin_width[b][chn_index][(j+tch.trigger_cell) % 1024];

printf("%10d %10d %10f %10f %10d\n", eh.event_serial_number , chn_index , waveform[0][chn_index][i] , time[0][chn_index][i] , i);

And after alignment procedure:

t1 = time[b][0][(1024-tch.trigger_cell) % 1024];

for (chn=1 ; chn<4 ; chn++) {

t2 = time[b][chn][(1024-tch.trigger_cell) % 1024];

dt = t1 - t2;

for (i=0 ; i<1024 ; i++)

time[b][chn][i] += dt;

printf("%10d %10d %10f %10f %10d\n", eh.event_serial_number , chn_index , waveform[0][chn_index][i] , time[0][chn][i] , i);

}

Does it caused by some software or drivers changes?

Best regards,

Volodymyr

|

|

627

|

Tue Jul 25 14:47:05 2017 |

Volodymyr Rodin | Time output | Hi again.

Okay, it works with 5.05 version very good and it is enough for me.

Besides,

What do I need to fix in this code for 2048 board?

Best wishes,

Volodymyr

| Volodymyr Rodin wrote: |

|

Hello Stefan

I tried to convert binary to a simple txt file and found next problem - strange time output.

Here is output from little modification for read_binary.cpp (Its last output line also is strange: dT = -1.#IOns +- -1.$ps)

Found data for board #0

Found timing calibration for channel #1

Found boards# 1

event channel waveform time point

1 0 -0.000092 0.000000 0

1 0 0.030548 0.000000 1

1 0 0.059418 0.000000 2

1 0 0.080200 0.000000 3

1 0 0.094223 0.000000 4

1 0 0.097702 0.000000 5

1 0 0.094055 0.000000 6

1 0 0.079117 0.000000 7

1 0 0.060364 0.000000 8

1 0 0.030960 0.000000 9

1 0 0.000504 0.000000 10

1 0 -0.031555 0.000000 11

1 0 -0.057465 0.000000 12

1 0 -0.080536 0.000000 13

1 0 -0.095413 0.000000 14

1 0 -0.099365 0.000000 15

I used output string in the following places, but it didn't help:

// reach channel data

:for (i=0 ; i<1024 ; i++) {

// convert data to volts

waveform[0][chn_index][i] = (voltage[i] / 65536. + eh.range/1000.0 - 0.5);

// calculate time for this cell

for (j=0,time[b][chn_index][i]=0 ; j<i ; j++)

time[b][chn_index][i] += bin_width[b][chn_index][(j+tch.trigger_cell) % 1024];

printf("%10d %10d %10f %10f %10d\n", eh.event_serial_number , chn_index , waveform[0][chn_index][i] , time[0][chn_index][i] , i);

And after alignment procedure:

t1 = time[b][0][(1024-tch.trigger_cell) % 1024];

for (chn=1 ; chn<4 ; chn++) {

t2 = time[b][chn][(1024-tch.trigger_cell) % 1024];

dt = t1 - t2;

for (i=0 ; i<1024 ; i++)

time[b][chn][i] += dt;

printf("%10d %10d %10f %10f %10d\n", eh.event_serial_number , chn_index , waveform[0][chn_index][i] , time[0][chn][i] , i);

}

Does it caused by some software or drivers changes?

Best regards,

Volodymyr

|

|

|

633

|

Tue Oct 17 14:58:58 2017 |

Vadym Denysenko | Time offset | Hello.

I have a simple question, can I set SetTriggerDelayNs() more than 1631 ns?

I need to set this delay to about 5 us... Can I do this?

Thank you in advance!

With best regards,

Vadym |

|

635

|

Wed Oct 18 11:48:14 2017 |

Vadym Denysenko | Time offset | Thank you for your reply!

| Stefan Ritt wrote: |

|

No this is not possible. But you can delay your signal externally (like with a delay cable or electronically) and then send the dealyed signal to the evaluation board for triggering.

Stefan

| Vadym Denysenko wrote: |

|

Hello.

I have a simple question, can I set SetTriggerDelayNs() more than 1631 ns?

I need to set this delay to about 5 us... Can I do this?

Thank you in advance!

With best regards,

Vadym

|

|

|

|