| ID |

Date |

Author |

Subject |

|

51

|

Wed Mar 10 10:07:28 2010 |

Stefan Ritt | Serial Interface Frequency of the DRS Chip |

| Hao Huan wrote: |

|

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

|

The reason for the 16.5 MHz is the following:

After each block of 32 bins, the DRS4 chip switches an internal segment, which causes some small spike at the analog output of the chip. This spike is a bit wider than 30ns, so if everything is digitized with 33 MHz, then you see small spiked each 32 cells. The appropriate solution would be to modify the firmware to digitize all cells with 30ns (33 MHz) and all cells with the spike with ~50 ns (20 MHz). If you do the ROI readout mode, you don't know for the first 10 cells if one of them belong to this class, since the cell address takes 10 cycles to be read out. So you would first have to read 10 cells, and then if you realize that one of them is one of the problematic ones (cell number modulo 32 is zero), you have to re-read the first 10 cells, and digitize the problematic cell with a longer settling time. Now this is a bit complicated to implement in the firmware, so I was just too lazy to do it and decided to digitize everything with 16.5 MHz. But if you are worried about the dead time, you should consider implementing the mentioned algorithm. |

|

50

|

Tue Mar 9 23:28:45 2010 |

Hao Huan | Serial Interface Frequency of the DRS Chip | Hi Stefan,

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

Thanks!

|

|

49

|

Fri Mar 5 23:29:04 2010 |

Hao Huan | Readout of DRS Data |

| Hao Huan wrote: |

|

Hi Stefan,

thanks to your help I can now successfully keep the Domino wave running at a stable frequency and maintain the channel cascading information in the Write Shift Register. (Since you told me WSR always reads and writes at the same time, I think I need to rewrite the information back every time after reading out from WSR to decide from which channel my data come, don't I?)

However I'm still having difficulty in reading out from the DRS cells. I use the ROI readout mode and assume as long as I give a pulse on RSRLOAD the data will come out one by one. However, what I get is just a constant with some noise, which seems I'm always reading from the same cell. Actually I'm not very clear about how it works. What's the mechanism for RSRLOAD and do I have to initialize the Read Shift Register to use the ROI mode? Also I read in the datasheet that WSROUT will give RSR output when DWRITE is low. Sometimes I see some random bits from this output and sometimes I see all zero's. What is the reasonable output I should see from WSROUT, say, when I'm running in the transparent mode with DWRITE low?

Thank you very much!

|

Hi Stefan,

I tried again and confirmed the problem... In the full readout mode I could successfully read out all the data, but in the ROI mode if I naively apply a pulse at RSRLOAD the results are not right. Is there anything I should be careful about in the ROI readout mode?

Thanks!

|

|

48

|

Thu Mar 4 19:14:10 2010 |

Hao Huan | Readout of DRS Data | Hi Stefan,

thanks to your help I can now successfully keep the Domino wave running at a stable frequency and maintain the channel cascading information in the Write Shift Register. (Since you told me WSR always reads and writes at the same time, I think I need to rewrite the information back every time after reading out from WSR to decide from which channel my data come, don't I?)

However I'm still having difficulty in reading out from the DRS cells. I use the ROI readout mode and assume as long as I give a pulse on RSRLOAD the data will come out one by one. However, what I get is just a constant with some noise, which seems I'm always reading from the same cell. Actually I'm not very clear about how it works. What's the mechanism for RSRLOAD and do I have to initialize the Read Shift Register to use the ROI mode? Also I read in the datasheet that WSROUT will give RSR output when DWRITE is low. Sometimes I see some random bits from this output and sometimes I see all zero's. What is the reasonable output I should see from WSROUT, say, when I'm running in the transparent mode with DWRITE low?

Thank you very much!

|

|

47

|

Wed Mar 3 17:49:30 2010 |

Stefan Ritt | Initialization of the Domino Circuit |

| Hao Huan wrote: |

|

Hi Stefan,

I read in the datasheet that every time after power up the Domino wave in DRS4 needs to be started and stopped once to initialize the Domino circuit. However in your firmware it seems the chip immediately goes into the idle state after reset. Is that Domino circuit initialization really necessary?

Also an aside question: in your firmware the readout process has the SRCLK sent to DRS4 only about 200ns later after RSRLOAD gets asserted instead of immediately following RSRLOAD. Is there any reason for that?

Thanks a lot!

|

The start/stop requirement is obsolete and has been replaced by elog:10. I need to update this in the datasheet. The delay between the RSRLOAD and the SRCLK has the following reason: On the RSRLOAD the first sampling cell is output to the chip and to the ADC. This can sometimes be a rather high swing, which needs some time to settle, and some warm-up for the output driver. But actually I never really measured it, so it's there just as a safety margin. But I would encourage you to try to reduce this time and see it the first few bins of the readout change in offset. |

|

46

|

Wed Mar 3 17:36:31 2010 |

Hao Huan | Initialization of the Domino Circuit | Hi Stefan,

I read in the datasheet that every time after power up the Domino wave in DRS4 needs to be started and stopped once to initialize the Domino circuit. However in your firmware it seems the chip immediately goes into the idle state after reset. Is that Domino circuit initialization really necessary?

Also an aside question: in your firmware the readout process has the SRCLK sent to DRS4 only about 200ns later after RSRLOAD gets asserted instead of immediately following RSRLOAD. Is there any reason for that?

Thanks a lot!

|

|

45

|

Wed Mar 3 14:37:40 2010 |

Stefan Ritt | PLLLCK signal of DRS4 |

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior?

|

If the WSRin is fed internally to WSROUT, then the level of the WSRIN pin does not matter, it's just disconnected. You can leave the pin open without problem. WSROUT is however active, so you can observe the internal state of the write shift register. In the default configuration (8x1024 sampling cells), all 8 channels are active all the time, so the WSR is loaded with ones. The inverter at the output then makes all zeros from this. If you configure the chip as 4x2048 cells, then you will observe switching bits at WSROUT.

|

Sorry; WSROUT also has an inverter? Actually I have one more stupid question about the shift registers: when we assert the address bits to operate on one shift register, e.g. WSR, we use SRIN to give input and SROUT to read output; but how does the shift register know whether we're reading or writing? Or it will just receive input from SRIN and give output at SROUT at the same time?

|

Actually I double checked the schematics, WSROUT has NO inverter at the output. So the output should be always one in a 8x1024 channel configuration.

Concerning the read/write you are right. On each clock cycle, SRIN will be shifted into the first bit, and the last bit will be visible at SROUT. |

|

44

|

Mon Feb 22 17:23:59 2010 |

Hao Huan | PLLLCK signal of DRS4 |

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior?

|

If the WSRin is fed internally to WSROUT, then the level of the WSRIN pin does not matter, it's just disconnected. You can leave the pin open without problem. WSROUT is however active, so you can observe the internal state of the write shift register. In the default configuration (8x1024 sampling cells), all 8 channels are active all the time, so the WSR is loaded with ones. The inverter at the output then makes all zeros from this. If you configure the chip as 4x2048 cells, then you will observe switching bits at WSROUT.

|

Sorry; WSROUT also has an inverter? Actually I have one more stupid question about the shift registers: when we assert the address bits to operate on one shift register, e.g. WSR, we use SRIN to give input and SROUT to read output; but how does the shift register know whether we're reading or writing? Or it will just receive input from SRIN and give output at SROUT at the same time?

Thank you so much! |

|

43

|

Sun Feb 21 20:33:57 2010 |

Stefan Ritt | PLLLCK signal of DRS4 |

| Hao Huan wrote: |

|

By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior?

|

If the WSRin is fed internally to WSROUT, then the level of the WSRIN pin does not matter, it's just disconnected. You can leave the pin open without problem. WSROUT is however active, so you can observe the internal state of the write shift register. In the default configuration (8x1024 sampling cells), all 8 channels are active all the time, so the WSR is loaded with ones. The inverter at the output then makes all zeros from this. If you configure the chip as 4x2048 cells, then you will observe switching bits at WSROUT. |

|

42

|

Sun Feb 21 20:27:46 2010 |

Hao Huan | PLLLCK signal of DRS4 |

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Thanks! I see. The capacitor is important. However I'm a little confused... If PLLLCK=DTAP XOR REFCLK, shouldn't it integrate to low instead of high when the two clocks are in phase? I must have some misunderstanding here. So if we ignore any realistic complexity and assume DTAP is perfectly locked with REFCLK, will PLLLCK be always low or high? I'm sorry I do not know how the DRS internal PLL and its input/output work...

|

Actually the XOR is followed by an inverter, so it will integrate to high if the two clocks are in phase.

|

Got it. Thank you! By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior? |

|

41

|

Sun Feb 21 13:47:03 2010 |

Stefan Ritt | PLLLCK signal of DRS4 |

| Hao Huan wrote: |

|

Thanks! I see. The capacitor is important. However I'm a little confused... If PLLLCK=DTAP XOR REFCLK, shouldn't it integrate to low instead of high when the two clocks are in phase? I must have some misunderstanding here. So if we ignore any realistic complexity and assume DTAP is perfectly locked with REFCLK, will PLLLCK be always low or high? I'm sorry I do not know how the DRS internal PLL and its input/output work...

|

Actually the XOR is followed by an inverter, so it will integrate to high if the two clocks are in phase. |

|

40

|

Sun Feb 21 13:41:35 2010 |

Stefan Ritt | Real Time Conference 2010 | Hello,

may I draw your attention to the upcoming Real Time Conference 2010, taking place in Lisbon, Portugal, May 23rd to May 28th, 2010.

http://rt2010.ipfn.ist.utl.pt/

Several groups which are developing DRS4 electronics will come to this conference and present their work, so it will be a good opportunity to exchange ideas and experiences. There will also be a short course on digital pulse shape processing, which is highly relevant for our field.

Looking forward to see you in Lisbon,

Stefan |

|

39

|

Sun Feb 21 00:46:01 2010 |

Hao Huan | PLLLCK signal of DRS4 |

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

in the latest DRS4 datasheet I only saw your data of the DRS4 PLL locking time for 6GSPS sampling speed, with other rows "TBD". Have you tried those lower frequencies? According to the datasheet I think the PLLLCK should be stabily low when the PLL is locked; am I right? However when I try my design with the DRS4 chip and feed the reference clock signal at 0.5MHz or 2MHz, the PLLLCK I get can never stabilize. There could be some problem in the PCB circuit connection, but I want to confirm with you since I'm confused with those "TBD" blanks.

Thanks a lot!

|

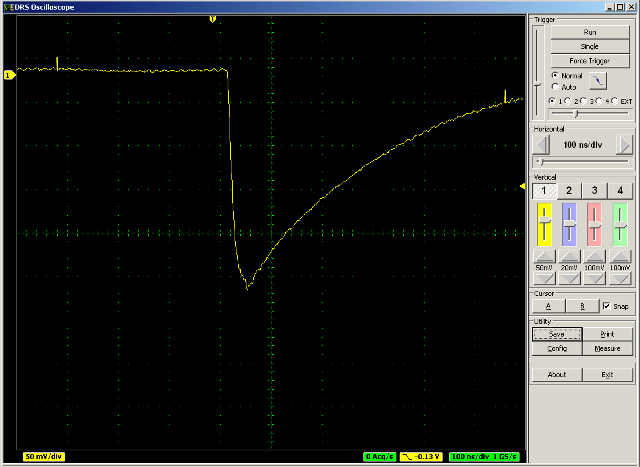

The locking time is typically 20-30 cycles of the external reference clock, I will update the numbers in the datasheet soon. I attached a screenshot of the chip when starting up at 1 GHz (0.5 MHz REFCLK), so you can see the behaviour. The upper curver is the DTAP signal, the lower curve the PLLLCK signal. As you can see, the PLLLCK signal is not purely digital. Actually it's a simple XOR between the REFCLK and the DTAP signal, so you need an external 4.7nF capacitor to "integrate" this signal. Without this capacitor, you would see small negative spikes whenever there is s small phase shift between the DTAP and the REFCLK signal. Have a look at your DTAP signal, is it in phase with the REFCLK?

|

Thanks! I see. The capacitor is important. However I'm a little confused... If PLLLCK=DTAP XOR REFCLK, shouldn't it integrate to low instead of high when the two clocks are in phase? I must have some misunderstanding here. So if we ignore any realistic complexity and assume DTAP is perfectly locked with REFCLK, will PLLLCK be always low or high? I'm sorry I do not know how the DRS internal PLL and its input/output work... |

|

38

|

Sat Feb 20 09:54:48 2010 |

Stefan Ritt | PLLLCK signal of DRS4 |

| Hao Huan wrote: |

|

Hi Stefan,

in the latest DRS4 datasheet I only saw your data of the DRS4 PLL locking time for 6GSPS sampling speed, with other rows "TBD". Have you tried those lower frequencies? According to the datasheet I think the PLLLCK should be stabily low when the PLL is locked; am I right? However when I try my design with the DRS4 chip and feed the reference clock signal at 0.5MHz or 2MHz, the PLLLCK I get can never stabilize. There could be some problem in the PCB circuit connection, but I want to confirm with you since I'm confused with those "TBD" blanks.

Thanks a lot!

|

The locking time is typically 20-30 cycles of the external reference clock, I will update the numbers in the datasheet soon. I attached a screenshot of the chip when starting up at 1 GHz (0.5 MHz REFCLK), so you can see the behaviour. The upper curver is the DTAP signal, the lower curve the PLLLCK signal. As you can see, the PLLLCK signal is not purely digital. Actually it's a simple XOR between the REFCLK and the DTAP signal, so you need an external 4.7nF capacitor to "integrate" this signal. Without this capacitor, you would see small negative spikes whenever there is s small phase shift between the DTAP and the REFCLK signal. Have a look at your DTAP signal, is it in phase with the REFCLK? |

|

37

|

Sat Feb 20 01:56:05 2010 |

Hao Huan | PLLLCK signal of DRS4 | Hi Stefan,

in the latest DRS4 datasheet I only saw your data of the DRS4 PLL locking time for 6GSPS sampling speed, with other rows "TBD". Have you tried those lower frequencies? According to the datasheet I think the PLLLCK should be stabily low when the PLL is locked; am I right? However when I try my design with the DRS4 chip and feed the reference clock signal at 0.5MHz or 2MHz, the PLLLCK I get can never stabilize. There could be some problem in the PCB circuit connection, but I want to confirm with you since I'm confused with those "TBD" blanks.

Thanks a lot!

|

|

36

|

Tue Feb 16 09:38:59 2010 |

Stefan Ritt | Problem reading oscilloscope binary waveform output |

| Ron Grazioso wrote: |

|

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

|

Yes, but you have to recompile the oscilloscope application. Find following line in the source file DOFrame.cpp:

m_WFfd = open(filename.char_str(), O_RDWR | O_CREAT | O_TRUNC | O_TEXT, 0644);

and replace it with

m_WFfd = open(filename.char_str(), O_RDWR | O_CREAT | O_TRUNC | O_BINARY, 0644);

that fixes the problem. To compile the program, you need MS Visual C++ and you have to install the vxWidgets library. Let me know if you have any problem with that.

Anyhow I plan a major software update soon (weeks), which not only fixes this problem, but also reduces the noise considerably by doing a kind of two-fold calibration.

- Stefan |

|

35

|

Mon Feb 15 19:43:34 2010 |

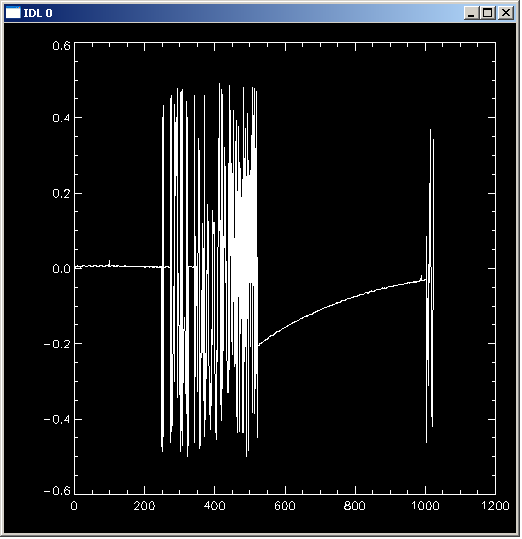

Ron Grazioso | Problem reading oscilloscope binary waveform output | I have saved some waveforms using the oscilloscope application in both binary and xml. I can see that the xml file gives me proper data values but when I try to read the binary file using IDL, it does not seem correct. This is a screen shot of the pulse I saved:

But when I open the binary file in IDL using:

data = uintarr(1024) ;unsigned integer array

readu,lun1,data

free_lun,lun1

close,lun1

;Convert bits to Volts

data=data*0.000015259-0.5

window,0,xs=512,ys=512

plot,data[*]

I get: I get:

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

Thanks, Ron

|

|

34

|

Wed Feb 10 15:35:09 2010 |

Stefan Ritt | Hello |

| pepe sanchez lopez wrote: |

|

hello i am an student and i want to do my final project with drs4 board and i really can´t find how to open waveform file and how can i save or opened many of them quickly.

if you can tell me how i will be very grateful.

thanks,

kind regards.

|

There is no built-in possibility to open waveform files, you have to write your own programs to do that. |

|

33

|

Wed Feb 10 02:57:55 2010 |

pepe sanchez lopez | Hello | hello i am an student and i want to do my final project with drs4 board and i really can´t find how to open waveform file and how can i save or opened many of them quickly.

if you can tell me how i will be very grateful.

thanks,

kind regards. |

|

32

|

Mon Feb 1 08:30:42 2010 |

Stefan Ritt | Failure In Flashing Xilinx PROM |

| Hao Huan wrote: |

|

Hi Stefan,

I have an old-version DRS4 evaluation board which doesn't have the latest firmware. I tried to flash the drs_eval1.ipf boundary scan chain into the XCF02S PROM with Xilinx IMPACT, and the firmware seemed to go through into the PROM. However, when I started the DRS command line interface to test the firmware it kept on reporting errors like

musb_write: requested 10, wrote -116, errno 0 (No error)

musb_read error -116

musb_write: requested 10, wrote -22, error 0 (No error)

musb_read error -116

and so on. Finally the program made a dumb recognition of the board as

Found mezz. board 0 on USB, serial #0, firmware revision 0

Do you have any idea which caused this problem? Thanks!

|

A firmware update requires a power cycle of the evaluation board. Have you tried that? I attached for you reference the current drs_eval1.mcs file, which is meant to go into the XCF02S PROM. There were recent changes also in the DRS library, and I'm not sure if yous if recent enough. So I put also the current C files which go with the firmware. They contain also some improvements which should reduce the intrinsic noise of the board. |

|