| ID |

Date |

Author |

Subject |

|

786

|

Fri May 22 12:53:33 2020 |

Stefan Ritt | DRS4 Evaluation board control tool 'drscl' with macro file | There is an example program in the distribution under software/drscl/drs_exam.cpp which is a stand-alone program to do what you need. It uses the C library coming with the distribution. It configureres the board, defines a trigger, and then writes a few waveforms into a file. You can use it as a starting point for your development. If you need any other language, you have to develop bindings to the C library.

Stefan

| Keita Mizukoshi wrote: |

|

Dear experts,

I would like to use DRS4 evaluation board as DAQ system for small, table-top experiment.

I need waveforms capture as binary file on some trigger based on command line without GUI.

I found `drscl` tool in official software, but it require interactive command. I'd rather use static macro or so on to control DAQ as same behaviour in each time.

I guess, experts are thinking users should develop DAQ code by themselves for their experiment specifically, but my request is very common so someone has already developed these tool.

Best regards,

Keita

|

|

|

785

|

Thu May 21 07:38:05 2020 |

Keita Mizukoshi | Type check at DOFrame.h in official software | Hi,

I've failured to compile official software. The cause is the following line.

DOFrame.h L.111 bool GetRefclk() { return m_refClk > 0; }

m_refClk is pointer to bool. I guess these line is for null-check of the pointer.

Can I replace the following line as

bool GetRefclk() { return m_refClk != nullptr; }

?

The latest compilers may not accept C-style check.

My compiler version is

Apple clang version 11.0.3 (clang-1103.0.32.59)

Target: x86_64-apple-darwin19.4.0

Thread model: posix

InstalledDir: /Applications/Xcode.app/Contents/Developer/Toolchains/XcodeDefault.xctoolchain/usr/bin

Best regards,

Keita |

|

784

|

Thu May 21 07:18:48 2020 |

Keita Mizukoshi | DRS4 Evaluation board control tool 'drscl' with macro file | Dear experts,

I would like to use DRS4 evaluation board as DAQ system for small, table-top experiment.

I need waveforms capture as binary file on some trigger based on command line without GUI.

I found `drscl` tool in official software, but it require interactive command. I'd rather use static macro or so on to control DAQ as same behaviour in each time.

I guess, experts are thinking users should develop DAQ code by themselves for their experiment specifically, but my request is very common so someone has already developed these tool.

Best regards,

Keita |

|

783

|

Mon Mar 23 15:03:28 2020 |

Ajay Krishnamurthy | USB trigger issue | Hello,

I had forgotten to disable the turn off the power to the USB drive on Windows and DRS4 stopped triggering. Now, we are all on quarantine and I am unable to reset the board to normal function. Are there any commands to reset the board remotely. I tried all of the default Windows based solutions such as disable USB port etc., but I am unable to do this. Only thing that has worked in the past is manually replugging the USB but I do not have the option to do that currently. Please help.

Thanks,

Ajay |

|

782

|

Fri Oct 25 16:39:07 2019 |

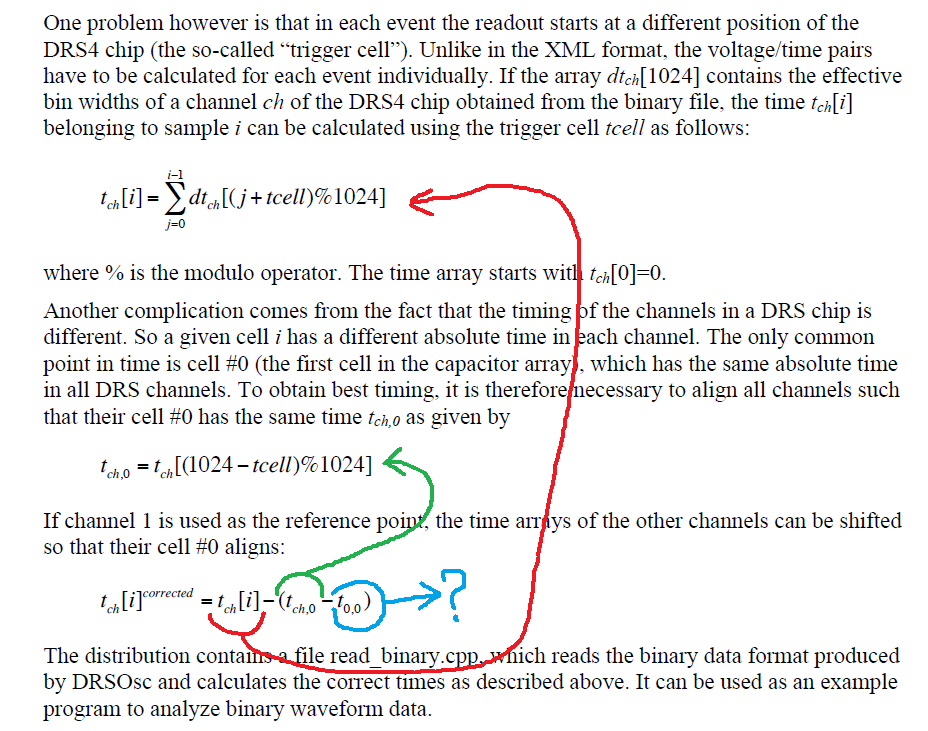

Stefan Ritt | Computing corrected time from binary data...what is t_0,0? | t0,0 refers to the time of cell #0 of channel #0. So basically you keep channel 0 fixed, calculate the difference of each channel's cell #0 in respect to channel 0, and align all channels except channel 0 so that their cell #0 has the same value. There is an inconsistency between the channel numbering. The formula uses 0...3 and the manual says "channel 1" but it means actually the first channel, which uses index "0".

Stefan

| John Jendzurski wrote: |

|

In the equations for computing the corrected time for channels other than channel 1, does anyone know what the term t0,0 refers to? This is the last term in the last equation on page 24 of DRS4 Evaluation Board User’s Manual, Board Revision 5 as of January 2014, Last revised: April 27, 2016.

Screenshot from User's Manual is attached below.

Thank you!

|

|

|

781

|

Wed Oct 23 17:56:26 2019 |

John Jendzurski | Computing corrected time from binary data...what is t_0,0? | In the equations for computing the corrected time for channels other than channel 1, does anyone know what the term t0,0 refers to? This is the last term in the last equation on page 24 of DRS4 Evaluation Board User’s Manual, Board Revision 5 as of January 2014, Last revised: April 27, 2016.

Screenshot from User's Manual is attached below.

Thank you! |

| Attachment 1: Screenshot.png

|

|

|

780

|

Tue Oct 15 08:14:17 2019 |

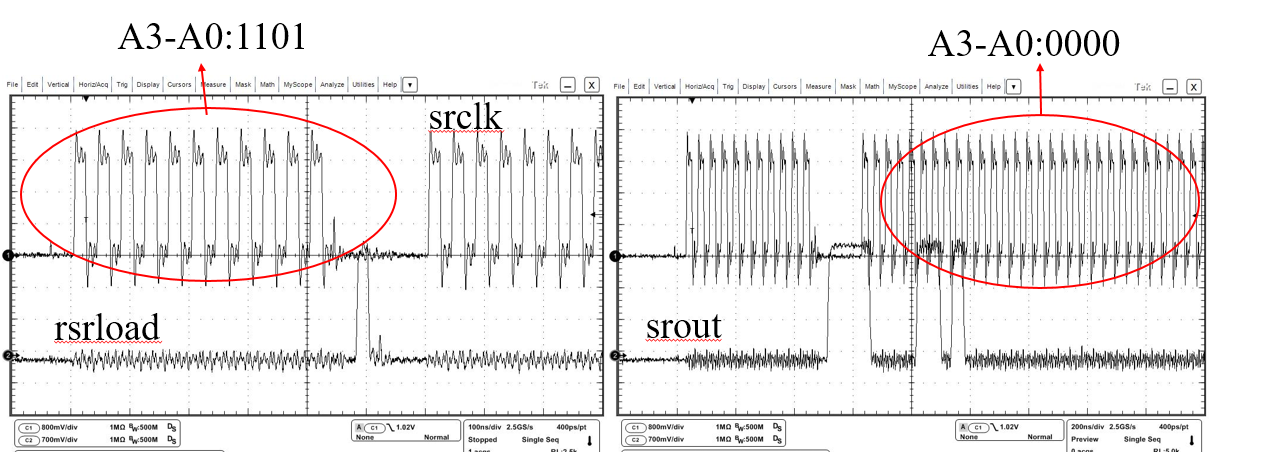

Danyang | how to acquire the stop position with channel cascading | Thanks a lot. The problem is solved when A3-A0 is set 1101 and srclk keeps low.

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

If you configure the Write Shift Register with 01010101b, then all you have to do after a trigger is to set A3-A0 to 1101. The WSROUT pin shows you then either ther state 01010101b or 10101010b, you the pin should be 1 or 0, and that's all you need. The Write Shift Register is NOT routed to the SROUT pin, you only see it at the WSROUT pin.

Stefan

| Danyang wrote: |

|

Yes, firstly I configured the chip with 4x2048 bins by setting the Write Shift Register to 01010101b, A3-A0 keeps 1101----> secondly I enabled the domino wave, wait some time for stable, A3-A0 keeps 1111 ---->thirdly stops the domino wave when the trigger comes, A3-A0 keeps 1101 (or 1010, 0000)----> forthly send the clock pulse to the srclk pin, A3-A0 keeps 1101, srout pin keeps low----> fifthly enable rsrload, A3-A0 (0000-1000), srout pin reacts nomally. I think the cascading is worked when I checked the waveform on the oscilloscope. Is there any step I missed?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

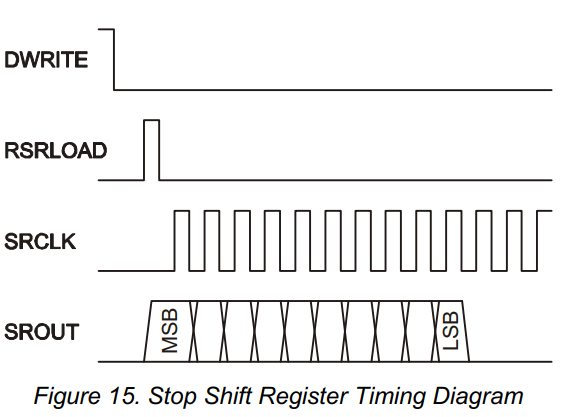

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

|

|

|

779

|

Mon Oct 14 15:27:09 2019 |

Stefan Ritt | how to acquire the stop position with channel cascading | If you configure the Write Shift Register with 01010101b, then all you have to do after a trigger is to set A3-A0 to 1101. The WSROUT pin shows you then either ther state 01010101b or 10101010b, you the pin should be 1 or 0, and that's all you need. The Write Shift Register is NOT routed to the SROUT pin, you only see it at the WSROUT pin.

Stefan

| Danyang wrote: |

|

Yes, firstly I configured the chip with 4x2048 bins by setting the Write Shift Register to 01010101b, A3-A0 keeps 1101----> secondly I enabled the domino wave, wait some time for stable, A3-A0 keeps 1111 ---->thirdly stops the domino wave when the trigger comes, A3-A0 keeps 1101 (or 1010, 0000)----> forthly send the clock pulse to the srclk pin, A3-A0 keeps 1101, srout pin keeps low----> fifthly enable rsrload, A3-A0 (0000-1000), srout pin reacts nomally. I think the cascading is worked when I checked the waveform on the oscilloscope. Is there any step I missed?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

|

|

778

|

Mon Oct 14 13:44:26 2019 |

Danyang | how to acquire the stop position with channel cascading | Yes, firstly I configured the chip with 4x2048 bins by setting the Write Shift Register to 01010101b, A3-A0 keeps 1101----> secondly I enabled the domino wave, wait some time for stable, A3-A0 keeps 1111 ---->thirdly stops the domino wave when the trigger comes, A3-A0 keeps 1101 (or 1010, 0000)----> forthly send the clock pulse to the srclk pin, A3-A0 keeps 1101, srout pin keeps low----> fifthly enable rsrload, A3-A0 (0000-1000), srout pin reacts nomally. I think the cascading is worked when I checked the waveform on the oscilloscope. Is there any step I missed?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

|

777

|

Mon Oct 14 12:56:13 2019 |

Stefan Ritt | how to acquire the stop position with channel cascading | Note that you have to read out the Write Shift Register only if you do channel cascading, e.g. configuring the chip with 4x2048 bins by setting the Write Shift Register to 01010101b. Then the Write Shift Register tells you in which 1024-bin segment the Domino Wave has been stopped. If you use the normal 8x1024 bin mode, you don't have to read out the Write Shift Register since it continas only 1's.

Stefan

| Danyang wrote: |

|

I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

|

|

776

|

Mon Oct 14 11:45:06 2019 |

Danyang | how to acquire the stop position with channel cascading | I tried the logic in my designed board. The results are shown in the picture: Srout keeps low when A3-A0 is set to 1101 and srclk is set as you mentioned. And the drs4 chip does not output sine wave in such configuration.

Srout signal only reacts after the rsrload signal is pulled high and A3-A0 is not 1101.

The number of srclk is not enough? Is there any recommended time to configure the command?

Best Regards,

Danyang

| Stefan Ritt wrote: |

|

You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

| Attachment 1: Capture.PNG

|

|

|

775

|

Mon Oct 14 10:14:46 2019 |

Stefan Ritt | how to acquire the stop position with channel cascading | You first set A3-A0, on the next clock cycle you issue pulses on srclk, and about 10ns after each clock pulse the output shows up at srout. Best is to verity this with an oscilloscope.

The radout of the shift register is independent of the readout mode, so you can use with with MUXOUT as well.

Stefan

| Danyang wrote: |

|

Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn)

|

|

|

774

|

Mon Oct 14 09:32:33 2019 |

Danyang | how to acquire the stop position with channel cascading | Hi Steffan,

In DSR4 DATASHEET Rev.0.9 Page13, there is a paragraph "If the DRS4 is configured for channel cascading or daisy chaining, it is necessary to know which the current channel is where the sampling has been stopped. This can be

determined by addressing the Write Shift Register withA3-A0 = 1101b and by applying clock pulses to the SRCLK input ...".

My question is the timing details about srclk, srout, A3-A0 in the above control and its timing relation with stop shift register (Figure 15). And can this configuration be used in the full readout mode with output MUXOUT?

Best Regards,

Danyang (sun2222@mail.ustc.edu.cn) |

| Attachment 1: Capture.PNG

|

|

|

773

|

Fri Sep 13 15:27:41 2019 |

Arseny Rybnikov | Scaler / How to modify the firmware to change the scaler integration time | Hello,

We want to use the inner DRS4 counter(scaler) within more than the 100ms integration time. We guess that we need to modify the original firmware around this point:

-- Reference clock used for frequency counter

proc_1hzclk: process(I_RESET, I_CLK33)

begin

if (I_RESET = '1') then

drs_1hz_counter(31 downto 0) <= (others => '0');

drs_1hz_clock <= '0';

scaler_reset <= (others => '1');

scaler_ff_reset <= (others => '1');

elsif rising_edge(I_CLK33) then

drs_1hz_counter <= drs_1hz_counter - 1; -- count down

scaler_reset <= (others => '0');

scaler_ff_reset <= (others => '0');

-- toggle refclk if timer expires

if (drs_1hz_counter(drs_1hz_counter'high) = '1') then

drs_1hz_clock <= not drs_1hz_clock;

drs_1hz_counter(31 downto 0) <= X"0016E35F"; -- 1499999, I_CLK33 is actually a 30 MHz clock

scaler_ff_reset <= (others => '1'); -- reset scaler_ff once every 100ms cycle

loop_scaler_reset : for i in 0 to 5 loop

if (scaler_ff(i) = '0') then -- no activity since last cycle?

scaler_reset(i) <= '1'; -- force clear scaler register

end if;

end loop;

if (scaler_ff(0) = '0') then -- no activity since last cycle?

scaler_reset(0) <= '1'; -- force clear scaler register

end if;

end if;

end if;

end process;

Could you please tell us how to modify the firmware to increse the time up to 5 seconds for instance?

Thanks in advance, Arseny |

|

772

|

Tue Aug 27 09:14:03 2019 |

Stefan Ritt | DRS4 | Is a 5 GSPS oscilloscope suitable for use with Silicon surface barier detectors?

| chinmay basu wrote: |

|

Is DRS4 suitable for use with Silicon surface barrier detectors?

|

|

|

771

|

Tue Aug 27 08:33:22 2019 |

chinmay basu | DRS4 | Is DRS4 suitable for use with Silicon surface barrier detectors? |

|

770

|

Tue Aug 20 16:05:21 2019 |

Bill Ashmanskas | should one deassert DENABLE while writing the write-shift register? | Aha -- many thanks. I think what tripped up my test logic is that the "done" state in drs4_eval5_app.vhd that executes post-readout sets DWRITE back to 1 (drs_write_set). If one then writes to FPGA register 5 while the FSM is in the "idle" state, the conf_strobe and wsr_strobe states occur with DWRITE and DENABLE both asserted. This is if one sets the "dactive" bit in the FPGA app code, which is probably not the usual use case. Maybe using the real DRS.cpp avoids this situation. (I was simulating your FPGA code to test my understanding of what our FPGA code should do.)

Anyway, our own use case is fine: as you suggest, we leave DENABLE asserted, but we deassert DWRITE while reading out or while changing DRS4 register values.

Thanks again,

Bill

| Stefan Ritt wrote: |

|

Hi Bill,

you keep DENABLE active all the time to keep the Domino Wave running, but you deassert DWRITE if you change any register via SRCLK. There is no shadow register, just a simple shift register, but with DWRITE being low, the domino circuitry does not touch it.

Best,

Stefan

| Bill Ashmanskas wrote: |

|

Hi Stefan,

We have for some time now been using custom firmware on a custom board to read waveforms out of DRS4 chips. Now we are working on cascaded readout mode, 4 channels @ 2048 samples, WSREG=0x55, in order to allow for longer trigger latency.

Doing a testbench simulation of the FPGA code raised a question for me: Do I need to deassert DENABLE while I shift a new 8-bit value into the write-shift register? What happens if, during the few-hundred nanoseconds it takes to shift 8 bits into the register, the domino wave crosses cell 768, thereby shifting the write-shift register left by one bit? Is this shifting suppressed when A=0b1101? Or does the update of the actual write-shift register occur only once, after the 8th SRCLK cycle? (Maybe one is really shifting bits into a shadow register that is copied all at once into the actual register?)

I notice in simulating your drs4_eval5_app.vhd that if one sets bit 27 ("drs_ctl_dactive") of register 0 (do not deassert DENABLE on trigger), then starts the domino wave (set bit 0 of register 0), then issues a software trigger, then later writes to register 5 (config register, wsreg, etc.), DENABLE is not in fact deasserted during the time when A=0b1100 (conf_setup, conf_strobe) or when A=0b1101 (wsr_setup, wsr_strobe).

But my simulation testbench includes a simplified Verilog model of my interpretation of the DRS4 data sheet, and my simulated DRS4 happened to cause the write-shift register to shift (256 samples before DTAP toggled) during your "wsr_strobe" FSM state, thus corrupting the value that was being shifted into the WSREG via SRIN and SRCLK.

So I'm curious: to be safe, should one deassert DENABLE before updating the write-shift register, or is it safe to update it even while the domino wave is active and looping? It seems easy enough to be safe, since we should only need to write to the WSREG once during the setup phase and then let it loop forever.

Many thanks,

Bill

|

|

|

|

769

|

Tue Aug 20 10:44:45 2019 |

Stefan Ritt | should one deassert DENABLE while writing the write-shift register? | Hi Bill,

you keep DENABLE active all the time to keep the Domino Wave running, but you deassert DWRITE if you change any register via SRCLK. There is no shadow register, just a simple shift register, but with DWRITE being low, the domino circuitry does not touch it.

Best,

Stefan

| Bill Ashmanskas wrote: |

|

Hi Stefan,

We have for some time now been using custom firmware on a custom board to read waveforms out of DRS4 chips. Now we are working on cascaded readout mode, 4 channels @ 2048 samples, WSREG=0x55, in order to allow for longer trigger latency.

Doing a testbench simulation of the FPGA code raised a question for me: Do I need to deassert DENABLE while I shift a new 8-bit value into the write-shift register? What happens if, during the few-hundred nanoseconds it takes to shift 8 bits into the register, the domino wave crosses cell 768, thereby shifting the write-shift register left by one bit? Is this shifting suppressed when A=0b1101? Or does the update of the actual write-shift register occur only once, after the 8th SRCLK cycle? (Maybe one is really shifting bits into a shadow register that is copied all at once into the actual register?)

I notice in simulating your drs4_eval5_app.vhd that if one sets bit 27 ("drs_ctl_dactive") of register 0 (do not deassert DENABLE on trigger), then starts the domino wave (set bit 0 of register 0), then issues a software trigger, then later writes to register 5 (config register, wsreg, etc.), DENABLE is not in fact deasserted during the time when A=0b1100 (conf_setup, conf_strobe) or when A=0b1101 (wsr_setup, wsr_strobe).

But my simulation testbench includes a simplified Verilog model of my interpretation of the DRS4 data sheet, and my simulated DRS4 happened to cause the write-shift register to shift (256 samples before DTAP toggled) during your "wsr_strobe" FSM state, thus corrupting the value that was being shifted into the WSREG via SRIN and SRCLK.

So I'm curious: to be safe, should one deassert DENABLE before updating the write-shift register, or is it safe to update it even while the domino wave is active and looping? It seems easy enough to be safe, since we should only need to write to the WSREG once during the setup phase and then let it loop forever.

Many thanks,

Bill

|

|

|

768

|

Mon Aug 19 23:01:22 2019 |

Bill Ashmanskas | should one deassert DENABLE while writing the write-shift register? | Hi Stefan,

We have for some time now been using custom firmware on a custom board to read waveforms out of DRS4 chips. Now we are working on cascaded readout mode, 4 channels @ 2048 samples, WSREG=0x55, in order to allow for longer trigger latency.

Doing a testbench simulation of the FPGA code raised a question for me: Do I need to deassert DENABLE while I shift a new 8-bit value into the write-shift register? What happens if, during the few-hundred nanoseconds it takes to shift 8 bits into the register, the domino wave crosses cell 768, thereby shifting the write-shift register left by one bit? Is this shifting suppressed when A=0b1101? Or does the update of the actual write-shift register occur only once, after the 8th SRCLK cycle? (Maybe one is really shifting bits into a shadow register that is copied all at once into the actual register?)

I notice in simulating your drs4_eval5_app.vhd that if one sets bit 27 ("drs_ctl_dactive") of register 0 (do not deassert DENABLE on trigger), then starts the domino wave (set bit 0 of register 0), then issues a software trigger, then later writes to register 5 (config register, wsreg, etc.), DENABLE is not in fact deasserted during the time when A=0b1100 (conf_setup, conf_strobe) or when A=0b1101 (wsr_setup, wsr_strobe).

But my simulation testbench includes a simplified Verilog model of my interpretation of the DRS4 data sheet, and my simulated DRS4 happened to cause the write-shift register to shift (256 samples before DTAP toggled) during your "wsr_strobe" FSM state, thus corrupting the value that was being shifted into the WSREG via SRIN and SRCLK.

So I'm curious: to be safe, should one deassert DENABLE before updating the write-shift register, or is it safe to update it even while the domino wave is active and looping? It seems easy enough to be safe, since we should only need to write to the WSREG once during the setup phase and then let it loop forever.

Many thanks,

Bill

|

|

767

|

Sat Jul 20 12:28:14 2019 |

Stefan Ritt | Trace Impedance | The DRS4 input is high impedance. So if you like you can terminate it with 100 Ohm differentially and route it with 100 Ohm. But if you keep the lines short, the reflection is negligible. That’s what we made on the evaluation board.

| Ismael Garcia wrote: |

|

When you're refering to laying a 50 Ohm trace, you're referring to the SMA input and not the interface between the output of the Op-AMP(THS4508) buffer

and the inputs of the DRS4(IN0-IN8). Is there a recommended diffential impedance for IN0-IN8?

Ismael

| Stefan Ritt wrote: |

|

The requiremnet is the same as for any high speed analog board, there is othing special with the DRS4. If you want to terminate your line with 50 Ohms and you want a matched impedance layout, you route all lines with 50 Ohms impedance. Truth is however that nothing is perfect. The SMA connector is not exactly 50 Ohm, the PCB gets a 10-20% variation depending on the manufacturer. So even if you try hard, you will never have a 50 Ohm matched impedance. On the evaluation board we made some compromises as you have seen, but for us the board works satisfactory even with this compromises, and you can test it yourself with real hardware (namely the evaluation board). If you can do a better job, try it. But usually these compromises have only little influence on the signal quality.

Stefan

| Ismael Garcia wrote: |

|

Hi Steffan,

I'm an engineer at UCLA developing a board with the DRS4 chip. Our team has a question on what might be the required trace impedence for the analog inputs. Can that information be provided?

Best Regards,

Ismael Garcia

|

|

|

|

|