Wed Aug 1 00:49:30 2018, Sean Quinn, Optimal readout speed Wed Aug 1 00:49:30 2018, Sean Quinn, Optimal readout speed

|

Dear DRS4 team,

On page 3 of the data sheet, Table 1. for readout speed a typical value of 10 MHz is specified, but in the comment column it notes optimal performance achieved at 33 MHz.

I see the V5.1 eval board runs at 16 MHz. I'd like to understand the rationale for this using speed, instead of 33 MHz. Is there an SNR issue for the ADC at the higher speed, even though this is optimal for the DRS4?

Very best,

Sean |

Mon Nov 5 17:17:08 2018, Sean Quinn, Pi attenuator on eval board inputs? Mon Nov 5 17:17:08 2018, Sean Quinn, Pi attenuator on eval board inputs?

|

Dear DRS4 team,

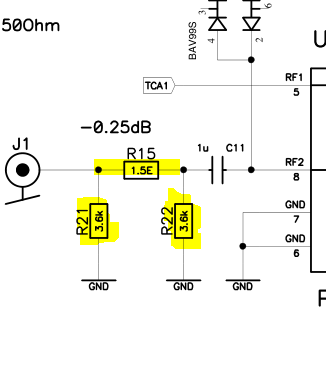

I am curious about this part of the circuit:

What is the purpose of this? |

Wed Apr 7 03:29:39 2021, Sean Quinn, Unexpected noise in muxout: t_samp related? Wed Apr 7 03:29:39 2021, Sean Quinn, Unexpected noise in muxout: t_samp related?

|

Dear DRS4 team,

I'm experiencing some issues that seem to be isolated to the ASIC, and would like to understand if we are doing something wrong. There are several items to address in the post.

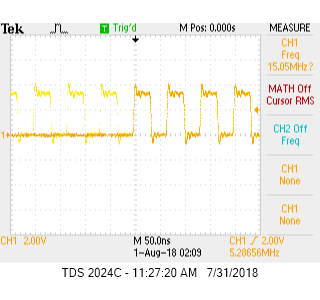

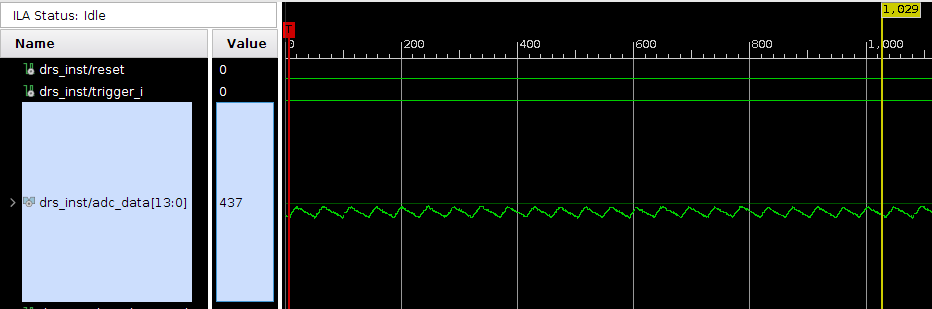

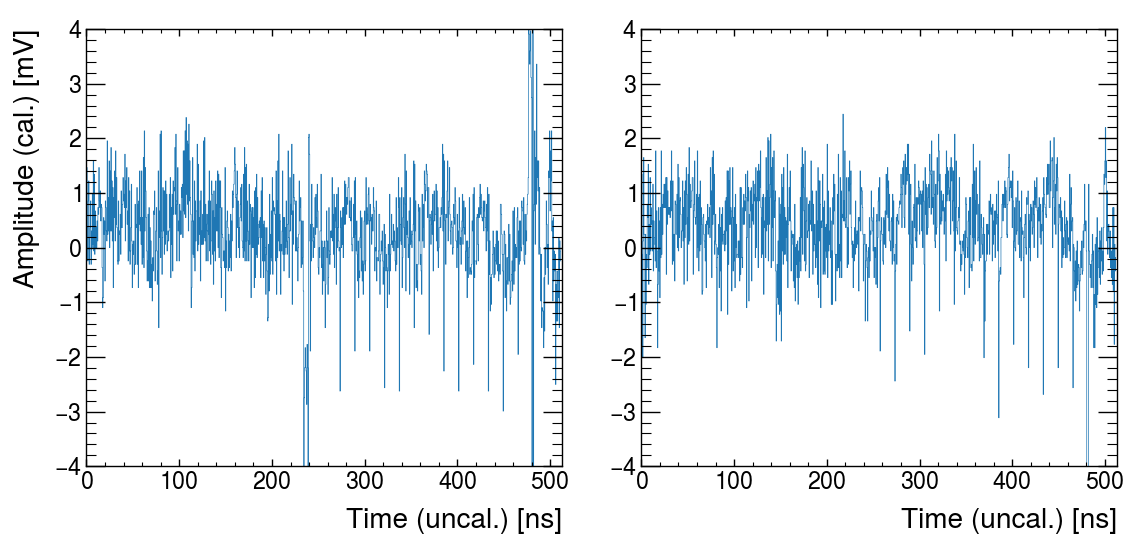

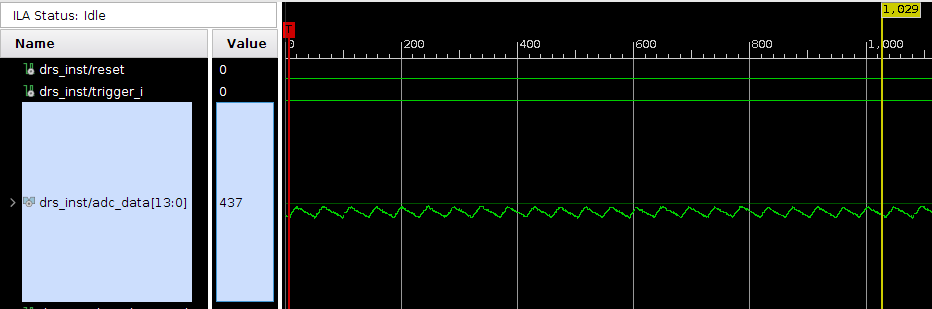

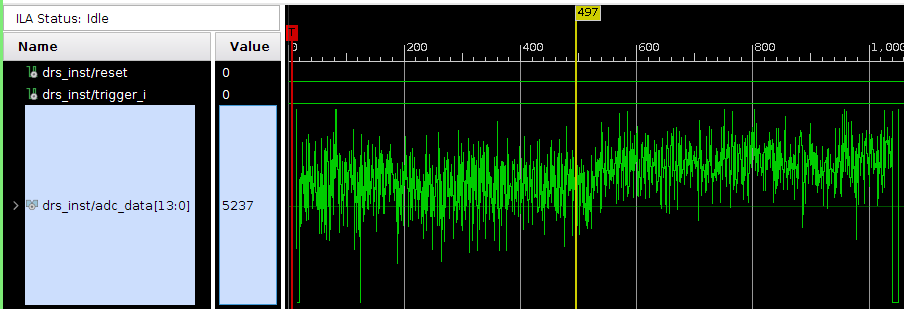

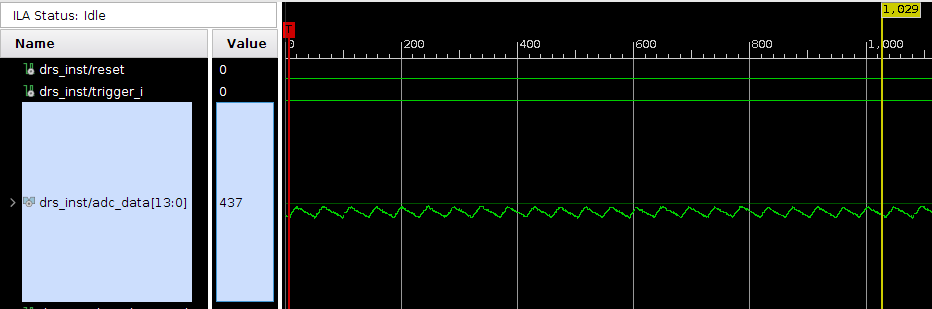

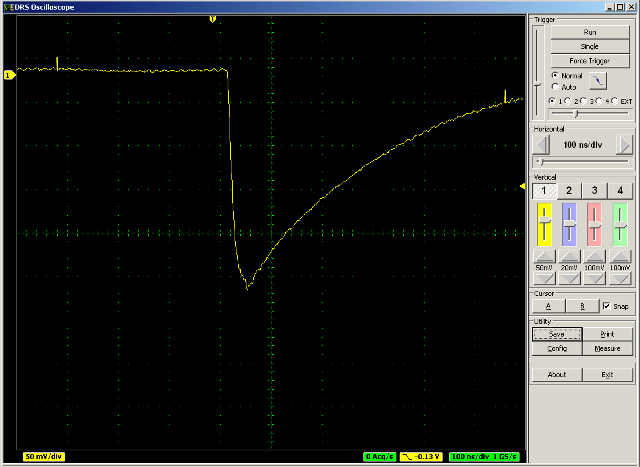

First, I do not think the noise observed is being injected from elsewhere on the board. If I run the DRS in transparent mode, the baseline noise is low, on order 3.5 mV (60 ADU), perhaps radiated from a clock. See below image. The scale is 0 to 1000 ADU with LSB = 6 uV (same AD9245 as eval board.). The DRS is in RUNNING state, I have forced a trigger in the ILA. This is for a single channel, CH0, 1024 cells.

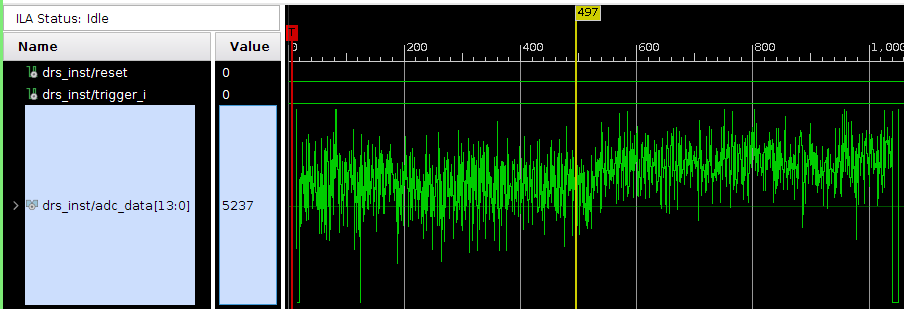

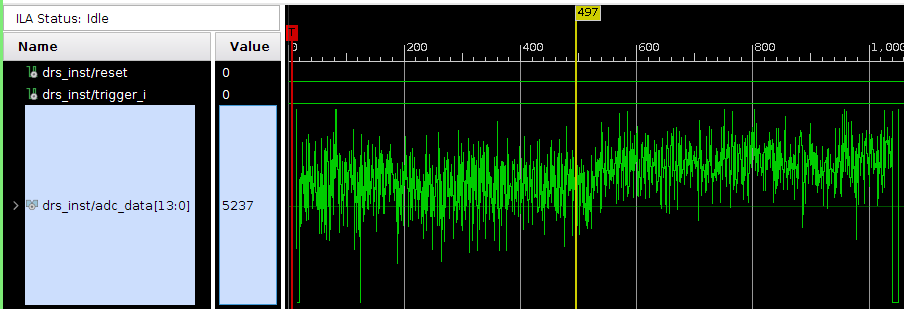

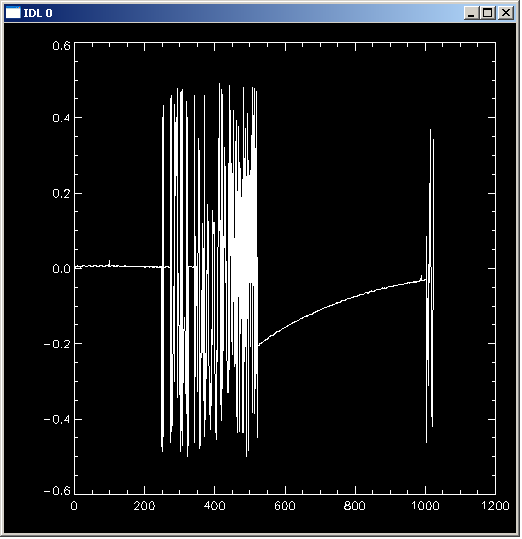

In the next image, I show the waveform obtained from a full readout. This corresponds to ADC_READOUT state, and the plot uses the same 1000 ADU scale. Noise seems around 350 ADU now, many factors worse than before.

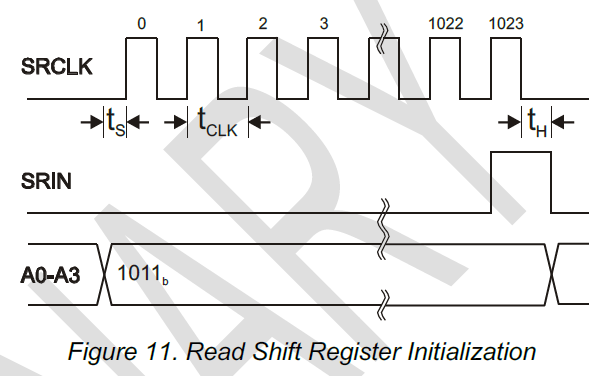

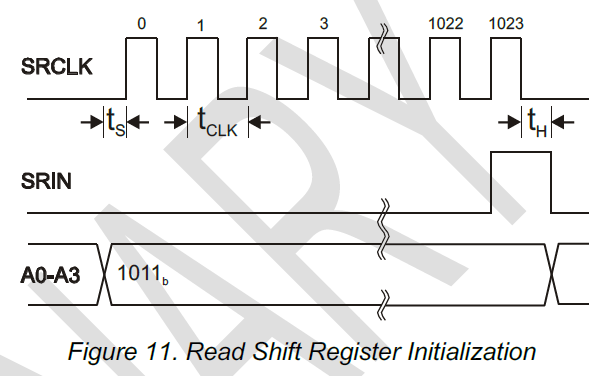

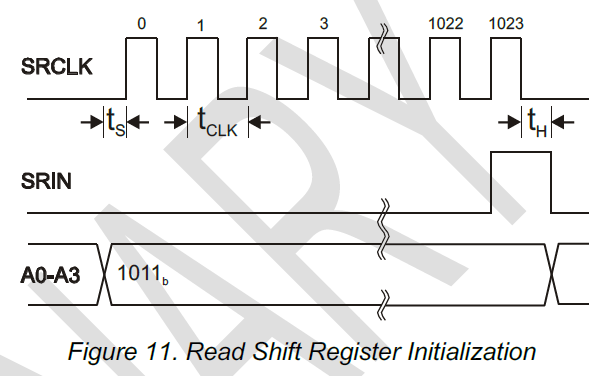

We've spent a lot of time trying to understand what's happening. One area that would be helpful to get some guidance on is the "t_samp" parameter. In Fig. 11 of the data sheet, should there be a t_samp label between t_s and t_clk? It just has arrows there with some width.

In our current firmware I believe R1 is simply one clock after R0 (for both ROI and full readout mode). Would this lead to the added noise observed in muxout?

This leads to the next question on what to actually use for t_samp. In the data sheet, page 4 "Timing Characteristics" it says to use t_samp = t0 + t_clk. Additionally, t0= 10 ns from that table. Fair enough.

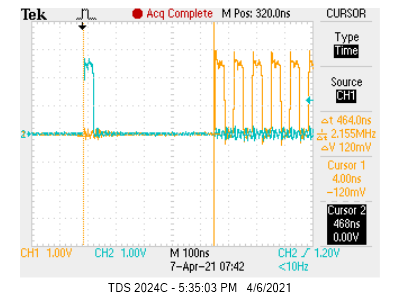

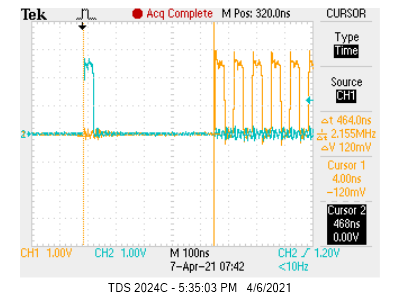

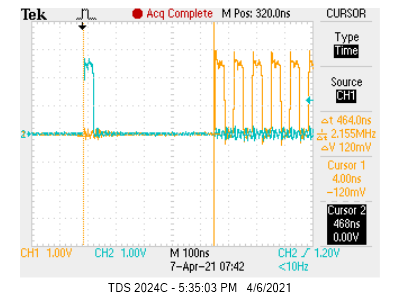

But if I check this against the eval board timing, I see very different values. Here the clock is 15 MHz so t_clk=67 ns (I note another post about this topic https://elog.psi.ch/elogs/DRS4+Forum/713), so I expect t_samp = 77 ns. But in practice it looks like the R0 to R1 delay is ~465 ns? (cyan=RSRLOAD, yellow=SRCLK)

Given this, is t_samp a value that should be tuned by the user?

Best regards,

Sean

|

Fri Apr 9 20:22:13 2021, Sean Quinn, Unexpected noise in muxout: t_samp related? Fri Apr 9 20:22:13 2021, Sean Quinn, Unexpected noise in muxout: t_samp related?

|

Hi Stefan,

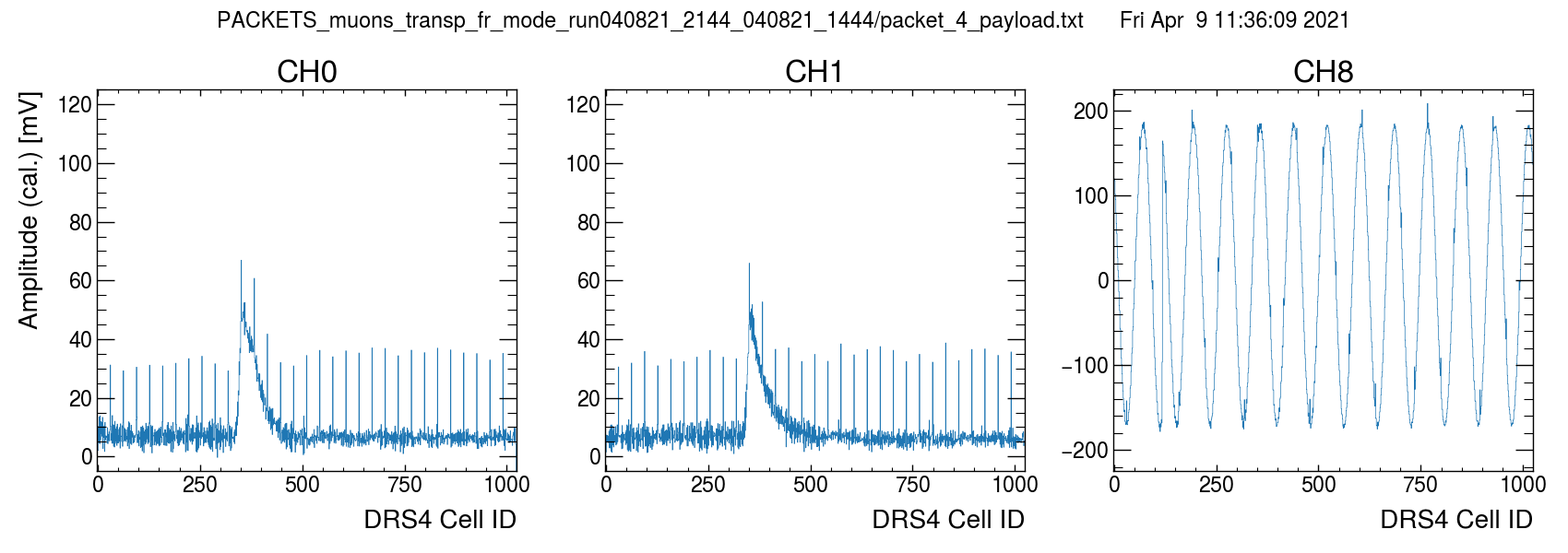

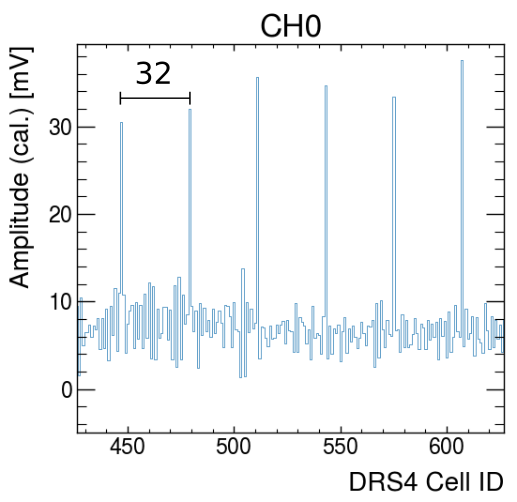

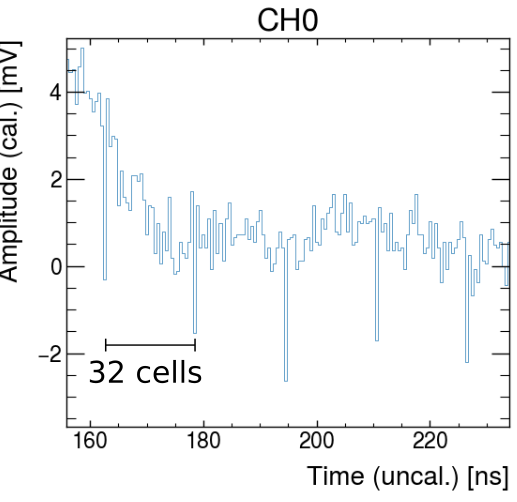

Thanks much for the quick reply. Ok, yes, things do seem ok after the offset calibration. I am running into some other issues I could use your advice on but will make a separate thread. As a preview, you can see hints in this waveform (periodic negative spikes).

This one should be considered resolved.

| Stefan Ritt wrote: |

|

Dear Sean,

noise in transparent mode comes from some coupling to your system clock. But 3.5 mV RMS seems rather hight to me. You should get it to below 1 mV if the DRS4 input is clean (try to short it).

The noise in the readout is expected. It looks exactly as Plot3 from the data sheet. You have to calibrate it away with a fixed offset for each cell as described in this paper: https://arxiv.org/abs/1405.4975 (paragraph IV. A. Voltage Calibration).

Concerning t_samp: Fig 11 in the datasheet just tells you that the rising edge of the SRCLK should come later than t_s after the address change. t_s is the setup time and 5 ns. Fig 12 tells you that the ADC should sample the analog output of the DRS t_samp after the address change A0-A3 and t_samp after the rising edge of SRCLK.

The digitizing speed of the evaluation board is indeed 15 MHz instead of the maximum 30 MHz, because this was easier to program in the FPGA. The t_samp has to be there so that the analog output signal of the DRS4 settles to its final value after each SRCLK pulse. If you sample "too early", you sample with the ADC the output when it is sill moving. So you have to wait until the analog is settled, but just before the next DRS sample becomes visible at the output. You can fine tune this with a differential probe at the DRS4 analog output (on a single ended probe you might drown in noise) on one channel of yoru scope and the ADC sample clock on the other channel of your scope. Note that the ADC sample clock cannot be derived straight from your FPGA clock, but you need some clock manager to fine-adjust its phase in 1ns steps.

But again, looking at your output, everything seems fine. You see the 5mV rms noise indicated in the datasheet table 1, which translates to about 20 mV peak-to-peak. If you do the offset calibration, this should go down to below 1 mV.

Best,

Stefan

| Sean Quinn wrote: |

|

Dear DRS4 team,

I'm experiencing some issues that seem to be isolated to the ASIC, and would like to understand if we are doing something wrong. There are several items to address in the post.

First, I do not think the noise observed is being injected from elsewhere on the board. If I run the DRS in transparent mode, the baseline noise is low, on order 3.5 mV (60 ADU), perhaps radiated from a clock. See below image. The scale is 0 to 1000 ADU with LSB = 6 uV (same AD9245 as eval board.). The DRS is in RUNNING state, I have forced a trigger in the ILA. This is for a single channel, CH0, 1024 cells.

In the next image, I show the waveform obtained from a full readout. This corresponds to ADC_READOUT state, and the plot uses the same 1000 ADU scale. Noise seems around 350 ADU now, many factors worse than before.

We've spent a lot of time trying to understand what's happening. One area that would be helpful to get some guidance on is the "t_samp" parameter. In Fig. 11 of the data sheet, should there be a t_samp label between t_s and t_clk? It just has arrows there with some width.

In our current firmware I believe R1 is simply one clock after R0 (for both ROI and full readout mode). Would this lead to the added noise observed in muxout?

This leads to the next question on what to actually use for t_samp. In the data sheet, page 4 "Timing Characteristics" it says to use t_samp = t0 + t_clk. Additionally, t0= 10 ns from that table. Fair enough.

But if I check this against the eval board timing, I see very different values. Here the clock is 15 MHz so t_clk=67 ns (I note another post about this topic https://elog.psi.ch/elogs/DRS4+Forum/713), so I expect t_samp = 77 ns. But in practice it looks like the R0 to R1 delay is ~465 ns? (cyan=RSRLOAD, yellow=SRCLK)

Given this, is t_samp a value that should be tuned by the user?

Best regards,

Sean

|

|

|

Fri Apr 9 20:29:45 2021, Sean Quinn, Spikes/noise sensitive to clock settings? Fri Apr 9 20:29:45 2021, Sean Quinn, Spikes/noise sensitive to clock settings?

|

Dear DRS4 team,

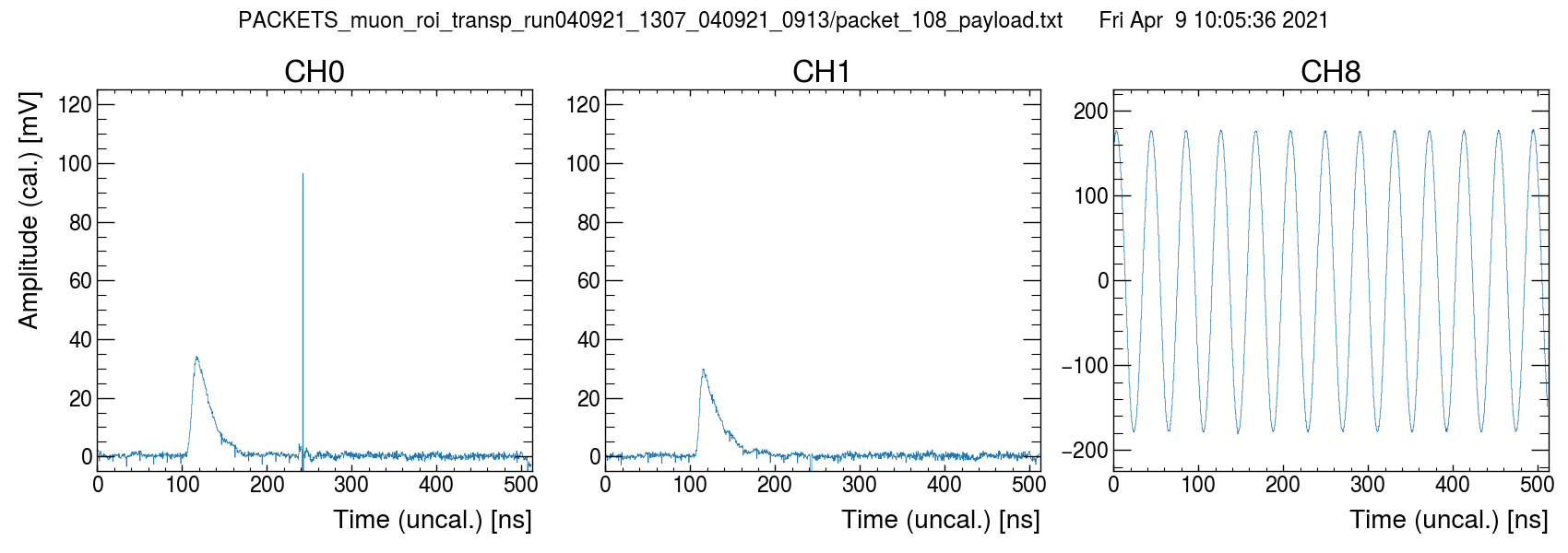

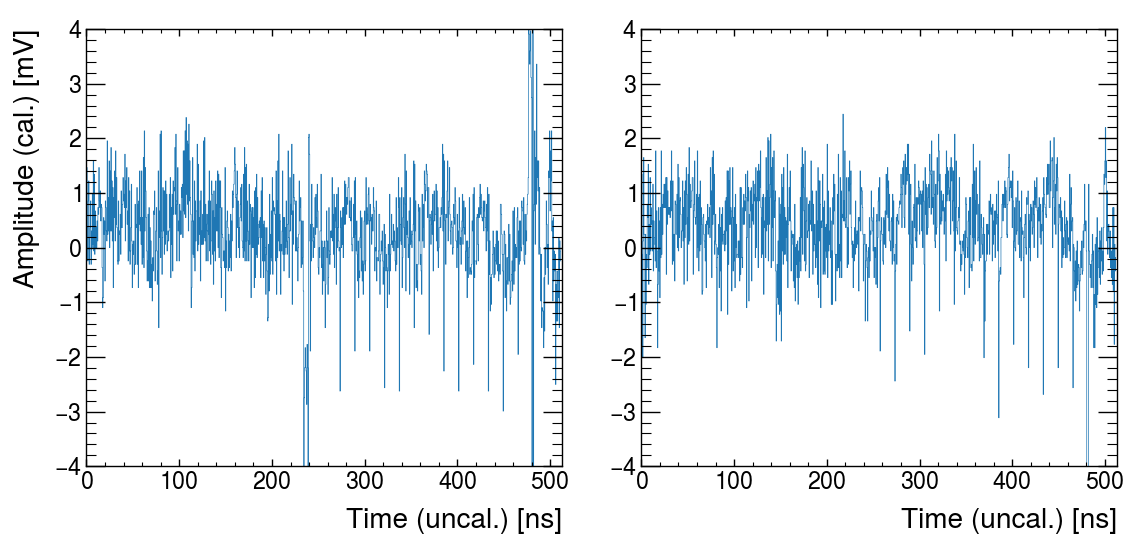

I'm trying to troubleshoot some odd spike behavior. If I run the ADC and SR CLK at 16 MHz (behavior also seen at 33 MHz) we get very noisy data (post-calibration) with periodic spikes.

In the below plot

- CH0 & CH1 are muon pulses from a scintillator + SiPM detector

- CH8 is a 25 MHz sinewave (in phase with all generated board clocks)

- Transparent mode = ON

- ROI = OFF, "full readout mode", first sample = cell 0

- DRS REFCLK = 1 MHz (2 GS/s)

- ADC & SR CLK = 16 MHz, 0 deg. offset

After I modify some clock settings, things seem to improve dramatically, and the spike behavior changes

- ADC and SR CLK = 15 MHz, 0 deg. offset

- Transparent mode = ON

- ROI = ON (just for testing purposes)

- Add 1.064 ns skew to DRS REF CLK

- NOTE: Unfortunately due to a design mishap, the ADC and FPGA clock use a phase-locked output pair on our clock synthesis chip, so we cannot fine-tune the skew for it.

Observed differences

- Spike polarity seems inverted

- Spikes limited to smaller number of cells now?

- Spike amplitude reduced

- Overall baseline variance seems better

- New large positive spike artifact on CH0 that seems inverted on CH1

- CH8 seems unaffected by large spikes?

Artifacts seem related to clock configuration, but I am sort of in the dark on what might be happening from a first-principles point of view. Any tips?

Warm regards,

Sean |

Fri Apr 9 21:56:54 2021, Sean Quinn, Unexpected noise in muxout: t_samp related? Fri Apr 9 21:56:54 2021, Sean Quinn, Unexpected noise in muxout: t_samp related?

|

Yes, there is some systematic board noise on this prototype, unfortunately

Ok, then it seems the other post I made might still belong in this thread after all.

Thanks for confirming negative spike behavior, we now have a mitigation plan going forward.

Cheers,

| Stefan Ritt wrote: |

|

If you do the cell calibration correctly, your noise should be ~0.4 mV. You seem to be 2-3x larger. The periodic negative spikes come if you dont' sample at the right time. Adjust t_samp until they are gone.

Stefan

| Sean Quinn wrote: |

|

Hi Stefan,

Thanks much for the quick reply. Ok, yes, things do seem ok after the offset calibration. I am running into some other issues I could use your advice on but will make a separate thread. As a preview, you can see hints in this waveform (periodic negative spikes).

This one should be considered resolved.

| Stefan Ritt wrote: |

|

Dear Sean,

noise in transparent mode comes from some coupling to your system clock. But 3.5 mV RMS seems rather hight to me. You should get it to below 1 mV if the DRS4 input is clean (try to short it).

The noise in the readout is expected. It looks exactly as Plot3 from the data sheet. You have to calibrate it away with a fixed offset for each cell as described in this paper: https://arxiv.org/abs/1405.4975 (paragraph IV. A. Voltage Calibration).

Concerning t_samp: Fig 11 in the datasheet just tells you that the rising edge of the SRCLK should come later than t_s after the address change. t_s is the setup time and 5 ns. Fig 12 tells you that the ADC should sample the analog output of the DRS t_samp after the address change A0-A3 and t_samp after the rising edge of SRCLK.

The digitizing speed of the evaluation board is indeed 15 MHz instead of the maximum 30 MHz, because this was easier to program in the FPGA. The t_samp has to be there so that the analog output signal of the DRS4 settles to its final value after each SRCLK pulse. If you sample "too early", you sample with the ADC the output when it is sill moving. So you have to wait until the analog is settled, but just before the next DRS sample becomes visible at the output. You can fine tune this with a differential probe at the DRS4 analog output (on a single ended probe you might drown in noise) on one channel of yoru scope and the ADC sample clock on the other channel of your scope. Note that the ADC sample clock cannot be derived straight from your FPGA clock, but you need some clock manager to fine-adjust its phase in 1ns steps.

But again, looking at your output, everything seems fine. You see the 5mV rms noise indicated in the datasheet table 1, which translates to about 20 mV peak-to-peak. If you do the offset calibration, this should go down to below 1 mV.

Best,

Stefan

| Sean Quinn wrote: |

|

Dear DRS4 team,

I'm experiencing some issues that seem to be isolated to the ASIC, and would like to understand if we are doing something wrong. There are several items to address in the post.

First, I do not think the noise observed is being injected from elsewhere on the board. If I run the DRS in transparent mode, the baseline noise is low, on order 3.5 mV (60 ADU), perhaps radiated from a clock. See below image. The scale is 0 to 1000 ADU with LSB = 6 uV (same AD9245 as eval board.). The DRS is in RUNNING state, I have forced a trigger in the ILA. This is for a single channel, CH0, 1024 cells.

In the next image, I show the waveform obtained from a full readout. This corresponds to ADC_READOUT state, and the plot uses the same 1000 ADU scale. Noise seems around 350 ADU now, many factors worse than before.

We've spent a lot of time trying to understand what's happening. One area that would be helpful to get some guidance on is the "t_samp" parameter. In Fig. 11 of the data sheet, should there be a t_samp label between t_s and t_clk? It just has arrows there with some width.

In our current firmware I believe R1 is simply one clock after R0 (for both ROI and full readout mode). Would this lead to the added noise observed in muxout?

This leads to the next question on what to actually use for t_samp. In the data sheet, page 4 "Timing Characteristics" it says to use t_samp = t0 + t_clk. Additionally, t0= 10 ns from that table. Fair enough.

But if I check this against the eval board timing, I see very different values. Here the clock is 15 MHz so t_clk=67 ns (I note another post about this topic https://elog.psi.ch/elogs/DRS4+Forum/713), so I expect t_samp = 77 ns. But in practice it looks like the R0 to R1 delay is ~465 ns? (cyan=RSRLOAD, yellow=SRCLK)

Given this, is t_samp a value that should be tuned by the user?

Best regards,

Sean

|

|

|

|

|

Thu Nov 14 11:39:06 2013, Schablo, Cascading of channels Thu Nov 14 11:39:06 2013, Schablo, Cascading of channels

|

Hello, I want use cascading of channels for 2048 cell - SetChannelConfig(0,8,4), but i can't understand how . Please, help me. Where i can dowload 2048_mode.ppt. (I found information about this file in DRS.cpp (3445 line "/ combine two halfs correctly, see 2048_mode.ppt")

Best regards,

Schablo Kostya |

Thu Nov 21 14:35:57 2013, Schablo, Cascading of channels Thu Nov 21 14:35:57 2013, Schablo, Cascading of channels

|

| Stefan Ritt wrote: |

|

| Schablo wrote: |

|

Hello, I want use cascading of channels for 2048 cell - SetChannelConfig(0,8,4), but i can't understand how . Please, help me. Where i can dowload 2048_mode.ppt. (I found information about this file in DRS.cpp (3445 line "/ combine two halfs correctly, see 2048_mode.ppt")

Best regards,

Schablo Kostya

|

You have to combine two channels into one, and depending on where the domino wave stopped, things get a bit complicated. I attach 2048_mode.ppt for your reference, but am not sure if this will really help.

/Stefan

|

Sorry for my question.

I'm trying change "drs_exam.cpp" for read 2048 cell.

I'm using SetChannnelConfig(0,8,4) and this code in "drs_exam.cpp" :

...

float arrX[2048];

float arrY[2048];

....

b->GetTime(0, b->GetTriggerCell(0), arrX);

b->GetWave(0, 0, arr.Y);

....

Return 2048 values in arrX[2048] - correct values, but in arrY[2048] - not correct values.

I can't understand what values return "GetWave" function. Please, say me how make, that GetWave function return correct values. " not - correct values "(i mean that i give signal in drs bord and values not true.)

Best regards,

Schablo Kostya

|

Wed Jan 30 06:51:37 2019, Saurabh Neema, DRS4 domino wave stability study Wed Jan 30 06:51:37 2019, Saurabh Neema, DRS4 domino wave stability study

|

We have been using DRS4 IC in our design for quite some time and it is giving good performance.

Till now we were using Domino wave frequency as 1 GSPS by use of reference clock to DRS4 and internal PLL of DRS4. Recently we tried to use 4GSPS by modifying the reference clock.

What I have found that DRS4 domino wave is more stable at 4 GSPS as compared to 1 GSPS by doing the timing jitter analysis. I am not sure if it is the property of DRS4 IC to be having more stable domino wave at higher frequency (by design) or it is due to some external effects like PLL loop filter or any other on board parasitic effects.

Please share if anyone has done any study of DRS4 Domino wave stability at different sampling frequencies.

Thanks,

|

Wed May 11 15:48:57 2016, SANDJONG Saturnin Orly, Probl�me de Calibration de la DRS4 Wed May 11 15:48:57 2016, SANDJONG Saturnin Orly, Probl�me de Calibration de la DRS4

|

Bonjour, Je suis en stage dans un laboratoire ou on utilise pour echantillonnage des données, une cartes DRS4 5GSPS avec 1024 cell, mon probléme réside dans la partie Calibration en tension selon l'article "Novel Calibration Method for Switched Capacitor Arrays Enables Time Measurements with Sub-Picosecond Resolution".

En fait je ne comprends pas précisément ces 3 parties de la calibration en tension. Quelqu'un pourras t-il s'il vous plait m'expliquer assez clairement avec des exemples comment il faut s'y prendre?

Merci et bien Cordialement. |

Sat Feb 19 17:25:29 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards Sat Feb 19 17:25:29 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya |

Mon Feb 21 12:42:33 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards Mon Feb 21 12:42:33 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards

|

| Stefan Ritt wrote: |

|

| Stefan Ritt wrote: |

|

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board.

|

Well, one thing you can do is to generate an external trigger and send it to the external trigger input of both cards. Then you can determine the time in respect to the trigger point in both boards. But since the trigger cell jitters by 2-3 cells in each chip, the accuracy is limited to about 1-2 ns when running at 2 GS/s.

|

Dear Stefan,

Thanks for the second suggestion. I wanted to do feasibility study of DRS4 application to our requirement in the experiment

Thank you again sir,

Upadhya |

Mon Feb 15 19:43:34 2010, Ron Grazioso, Problem reading oscilloscope binary waveform output Mon Feb 15 19:43:34 2010, Ron Grazioso, Problem reading oscilloscope binary waveform output

|

I have saved some waveforms using the oscilloscope application in both binary and xml. I can see that the xml file gives me proper data values but when I try to read the binary file using IDL, it does not seem correct. This is a screen shot of the pulse I saved:

But when I open the binary file in IDL using:

data = uintarr(1024) ;unsigned integer array

readu,lun1,data

free_lun,lun1

close,lun1

;Convert bits to Volts

data=data*0.000015259-0.5

window,0,xs=512,ys=512

plot,data[*]

I get: I get:

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

Thanks, Ron

|

Thu Apr 10 14:45:12 2014, Roman Gredig, DRS4 Evalboard V5 with Windows7Pro64bit Thu Apr 10 14:45:12 2014, Roman Gredig, DRS4 Evalboard V5 with Windows7Pro64bit

|

Dear Stefan

I am trying to use the DRS4 eval board on a Windows7 machine. Unfortunately I get an error message saying "No DRS

board found". But I can see the DRS board in the device manager with the proper driver loaded. Is there any known

problem with win7?

I am using windows7 professional (SP1) with the drs software 5.0.1.

Cheers,

Roman

PS: Everything is working on my mac. But not under windows7. |

Thu Jun 12 12:40:03 2014, Roman Gredig, DRS eval bord v5 Timing Thu Jun 12 12:40:03 2014, Roman Gredig, DRS eval bord v5 Timing

|

Dear Stefan

I have two questions concerning the best time resolution with the DRS V5 eval board.

a) Calibration:

I am using 4 boards daisy chained. To achieve optimal time resolution I did first a voltage calibration and right afterwards a time calibration. For all

boards after the master I am not sure how to do it.

After setting the flag "Configure multi-board daisy-chain" in the config menu, all the slave boards set the flag "use external reference clock". By

hitting the voltage calibration button, the slave boards unset this flag. Is it true, that I have to re-set this before doing the time-calibration right

afterwards?

b) getting the right times in binary format:

To get the time out of the time width (i.e. the t_ch[i]) you sum up in your documentation from j=0 to j=i (see attachment). In your example code

read_binary.cpp (line 113) you sum from j=0 to j=i-1. Since you get the the bin with in the binary file, I guess that the example code is correct one?

Thank you very much,

Cheers,

Roman |

Wed Aug 13 20:17:19 2014, Roman Gredig, binary files time calibration header in drs-5.0.2 Wed Aug 13 20:17:19 2014, Roman Gredig, binary files time calibration header in drs-5.0.2

|

Dear Stefan

I have a problem considering binary data files.

Usually binary files start with TIME... (the time calibration header). But I observed the following reproducible problem.

1. Start to save a binary file (e.g. 001.dat) with 1000000 events.

2. Hit the close button before this limit has reached. (so far the binary files seems to be ok)

3. Start to save again a file with the SAME filename (and agree to replace the already existing it)

If I do it like this, the file has no time information anymore and starts directly with EHDR.

could it be that the m_evSerial counter is not reset in this specific situation?

Cheers,

Roman |

Tue Aug 26 14:16:26 2014, Roman Gredig, binary files with more than 4 drs board ver. 5.0.2 Tue Aug 26 14:16:26 2014, Roman Gredig, binary files with more than 4 drs board ver. 5.0.2

|

Dear Stefan

after having some problems with writing binary files with more than 4 drs boards (in multiboard-mode) I might

have found the solution.

In the file src/Osci.cpp at line 838 is:

unsigned char buffer[100000];

If I understand the binary format right, this works only with up to four boards. With the maximum number of

boards in your specification (16 boards) and all channels switched on on all boards this array needs to have

about 400000 entries (for the first event, where the time information is written too).

Could you please cross-check that?

Thank you very much!

Cheers,

Roman |

Wed Mar 7 22:49:38 2018, Rodrigo Trindade de Menezes, Running drs_example.cpp Wed Mar 7 22:49:38 2018, Rodrigo Trindade de Menezes, Running drs_example.cpp

|

Hello,

We have been using the DRS4 evaluation board (S/N 2636) that works with the scope application. However we are trying to run the DRS4 evaluation board remotely by modifying the drs_exam.cpp to acquire and store data continuously.

We compiled the DRS_example.cpp without the wxWidgets but when we try to run the program, it appears to trigger on nonsense. The program appears to not be sensitive to the trigger threshold (although for very large trigger threshold it gets stuck in a waiting mode). Is there a way to ensure that the "normal" trigger mode is set? We are worried that the auto mode is running. Otherwise, not sure why the program is triggering on nonsense. By the way, it does not work with the wxWidgets compiled either so we are worried that there is an additional flag that needs to be set. The routine does not appear to conduct a calibration -- is this not necessary?

Another issue that we are having is with the data set stored on the .txt file looks incorrect. The time channel stops at 200 (but we think it should go up to 1024). In addition, the voltage channel appears to hover around small values near zero (as if triggering on noise). The output file appears this way even when we change the threshold to much higher values. It suggests that the trigger threshold is not actually being set? There are events where the output voltage appears to oscillate through huge negative and positive values too. So not sure what's going on.

Thanks!

Rodrigo |

Thu Mar 8 22:54:20 2018, Rodrigo Trindade de Menezes, Running drs_example.cpp Thu Mar 8 22:54:20 2018, Rodrigo Trindade de Menezes, Running drs_example.cpp

|

We found a way to solve the previous problem, but right now when we try to set the input range only -0.5 to 0.5 is working. When we set the function "SetInputRange(0.5)" for 0 to 1V the output is all zeros and with "SetInputRange(0.45)" we just get all the outputs -49.9mV. What does that means? How to fix?

| odrigo Trindade de Menezes wrote: |

|

Hello,

We have been using the DRS4 evaluation board (S/N 2636) that works with the scope application. However we are trying to run the DRS4 evaluation board remotely by modifying the drs_exam.cpp to acquire and store data continuously.

We compiled the DRS_example.cpp without the wxWidgets but when we try to run the program, it appears to trigger on nonsense. The program appears to not be sensitive to the trigger threshold (although for very large trigger threshold it gets stuck in a waiting mode). Is there a way to ensure that the "normal" trigger mode is set? We are worried that the auto mode is running. Otherwise, not sure why the program is triggering on nonsense. By the way, it does not work with the wxWidgets compiled either so we are worried that there is an additional flag that needs to be set. The routine does not appear to conduct a calibration -- is this not necessary?

Another issue that we are having is with the data set stored on the .txt file looks incorrect. The time channel stops at 200 (but we think it should go up to 1024). In addition, the voltage channel appears to hover around small values near zero (as if triggering on noise). The output file appears this way even when we change the threshold to much higher values. It suggests that the trigger threshold is not actually being set? There are events where the output voltage appears to oscillate through huge negative and positive values too. So not sure what's going on.

Thanks!

Rodrigo

|

|

Thu Feb 22 01:21:11 2024, Rod McInnis, Simulation of FPGA Thu Feb 22 01:21:11 2024, Rod McInnis, Simulation of FPGA

|

Hello:

A bit of background: I am working on a project that is utilizing the DRS4 Evaluation board as a prototype platform for a dedicated, special use capture. We will only be utilizing one channel of the ADC capture, and the 1024 samples is more than enough.

What I will need to do, however, is do some preprocessing on the incoming ADC data, running some calculation on the fly, possibly some filtering and other transformations before putting the data into the FPGA block memory for transfer to the host via the Cypress USB interface. I will be modifying the "drs4_eval5" VHDL file and doing a new FPGA build.

It will be essential that I be able to simulate this, from the ADC input to the data flow to the Cypress chip. I have "eval board files" which includes the VHDL source files, Xilinxe ISE project files and some very basic simulation testbenches.

Unfortunately, the simulation testbenches call out a "drs4_eval1" module while the Xilinx project uses a "drs4_eval5" module, and the module ports are a little different. I think I can work around that, however. I have run the simulatilon "drs4_eval1_tb", which does a simple write to a Control Register. I need to expand this simulation so that it will initiate a full capture and then transfer the data from the RAM to the Cypress chip.

What I am most confused about is how the Cypress chip sucks out the data from the FPGA block ram. I would expect it to use a burst mode data transfer rather than the cumbersom CSR read/write, but I haven't found any documentation on how this interface works.

Q1: Is there a simulation testbench file available that does the 1024 sample data transfer?

Q2: Is there a waveform diagram that shows the protocol / signal handshake between the FPGA and Cypress chip for this data transfer?

Thank you

Rod McInnis

|

|