| ID |

Date |

Author |

Subject |

|

763

|

Mon Jul 15 19:34:25 2019 |

Brendan Posehn | Evaluation Board Test Functionality |

Hello Stefan,

Thanks for the quick reply. The issue was a faulty SMA connector, should have checked this first. Signal looks good now.

Thanks for your time,

Brendan

| Stefan Ritt wrote: |

|

Have you set the trigger correctly to the channel with your signal, polarity and level? Do you undersand the difference between normal and auto trigger? Why don't you post a screendump. Are you ABSOLUTELY SURE that you have a signal on your cable? Have you tried with another oscilloscope? Are you sure that your SMA connector is good?

Stefan

| Brendan Posehn wrote: |

|

Hello,

I have recently obtained a DRS4 Evaluation Board (V5), but I am unable to register signals when using the DRS Oscilloscope application. There seems to be some difference in noise when I have an input connected to a signal or not, but I am unable to view a simple, 0.2V amplitude square wave or other small signals. The only way I have been able to view a waveform is when connecting the reference clock to all channels. When running 'info' in the DRS Command Line Interface I am shown correct information. I was wondering if there is any way for me to test the functionality of the board (specifially ability to read signals on Ch 1-4) to ensure that it is indeed working as expected?

Thanks,

Brendan

|

|

|

|

276

|

Tue Jul 23 22:31:08 2013 |

alonzi | Evaluation Board Behavior |

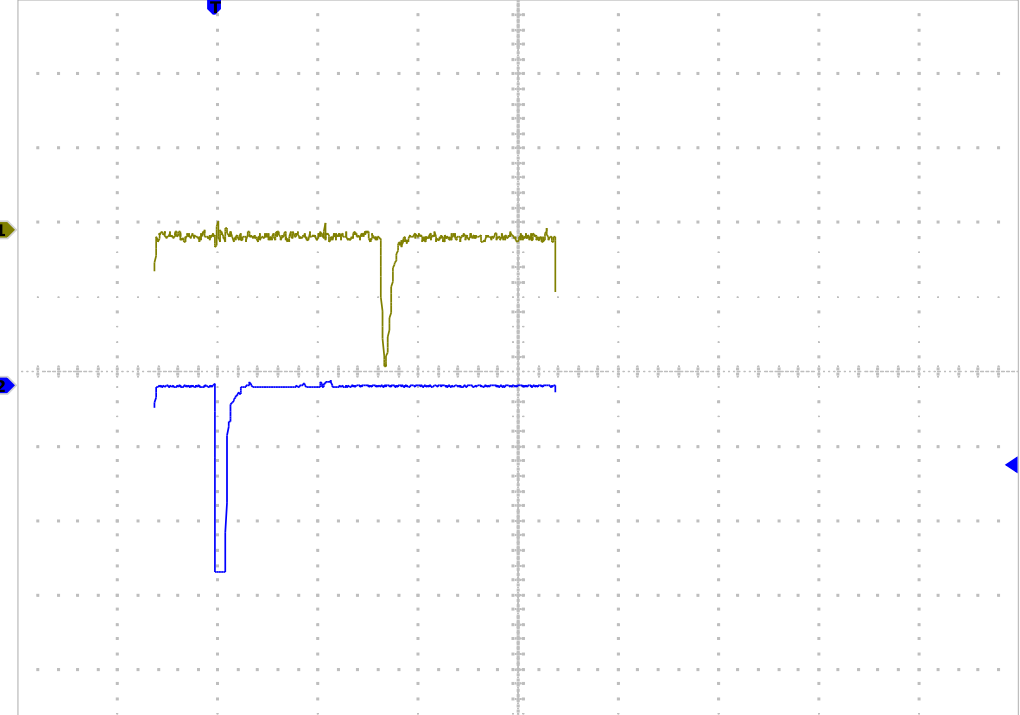

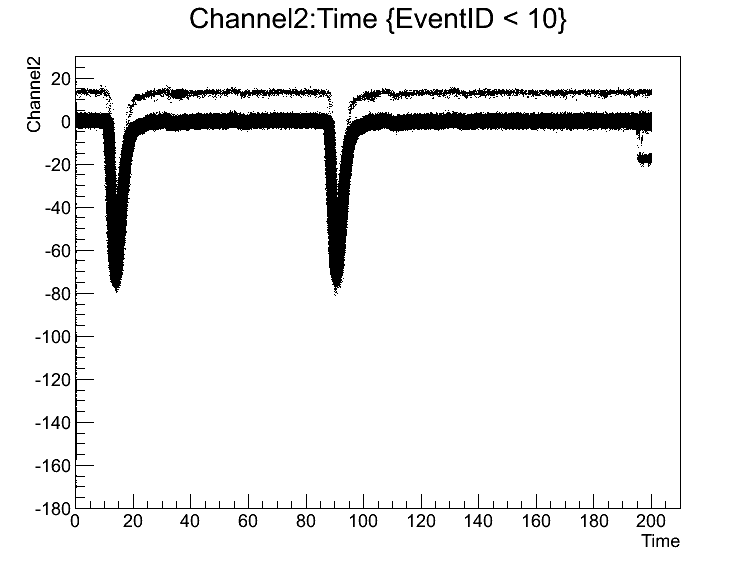

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion. |

| Attachment 1: Screenshot.png

|

|

| Attachment 2: data_problem.png

|

|

|

277

|

Tue Jul 23 22:35:08 2013 |

Stefan Ritt | Evaluation Board Behavior |

| alonzi wrote: |

|

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion.

|

Actually the first and last sample are even more off the baseline, so I cut them out in software in the DRSOscilloscope. So actually the chip has only 1022 "usable" cells. It might happen in some rare cases that more cells are affected, although I have not yet seen this (maybe I did not look close enough). So I propose that you cut out one more bin at the beginning and the end, so a total of 1020 cells, and you should be fine.

/Stefan |

|

278

|

Tue Jul 23 22:42:31 2013 |

alonzi | Evaluation Board Behavior |

| Stefan Ritt wrote: |

|

| alonzi wrote: |

|

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion.

|

Actually the first and last sample are even more off the baseline, so I cut them out in software in the DRSOscilloscope. So actually the chip has only 1022 "usable" cells. It might happen in some rare cases that more cells are affected, although I have not yet seen this (maybe I did not look close enough). So I propose that you cut out one more bin at the beginning and the end, so a total of 1020 cells, and you should be fine.

/Stefan

|

Thanks for the quick reply. Our quick fix was to do just that. |

|

279

|

Thu Jul 25 01:31:29 2013 |

Andrey Kuznetsov | Evaluation Board Behavior |

| alonzi wrote: |

|

| Stefan Ritt wrote: |

|

| alonzi wrote: |

|

Working with the DRS evaluation board we noticed some funny behavior: See attatchment 1. In about 1% of scope traces we see the first and last bin take on a value substantially different from the baseline, note the small spikes on the end of the traces. These spikes occur across all channels and either appear in all channels or in none. Attachment two shows what several thousand scope traces look like. You can clearly see that some of the traces are offset from the normal base line. Has anyone observed this behavior before? Any ideas?

see https://muon.npl.washington.edu/elog/g2/Detectors/550 for full discussion.

|

Actually the first and last sample are even more off the baseline, so I cut them out in software in the DRSOscilloscope. So actually the chip has only 1022 "usable" cells. It might happen in some rare cases that more cells are affected, although I have not yet seen this (maybe I did not look close enough). So I propose that you cut out one more bin at the beginning and the end, so a total of 1020 cells, and you should be fine.

/Stefan

|

Thanks for the quick reply. Our quick fix was to do just that.

|

We've encountered similar issues with board v2.0. Cell #2 across all channels would occasionally go full negative amplitude (0 I guess).

I don't remember if calibration fixed the problem, might have. |

|

908

|

Tue May 21 18:13:08 2024 |

Rebecca Hicks | Error when running drsosc |

Hi, I'm a student trying to figure out the DRS4 board. I cloned the github repo, but when I run drsosc, I get an error: Gtk-Message: 10:06:38.376: Failed to load module "canberra-gtk-module". I'm not sure what that means. The oscilloscope window does open up for me though. Thanks for any help! |

|

909

|

Fri Jun 28 23:33:51 2024 |

Patricia Lecomti | Error when running drsosc |

Salut !

Je vois que tu rencontres un petit problème avec ton installation. Le message "Gtk-Message: Failed to load module 'canberra-gtk-module'" indique que ton système essaie de charger un module GTK spécifique qui n'est pas installé. Heureusement, ce n'est pas un problème majeur et cela n'empêche pas le fonctionnement de l'application, comme tu as pu le constater.

Pour résoudre ce message d'erreur, tu peux installer le module manquant. Si tu es sur Ubuntu ou une distribution Debian-based, essaie cette commande dans ton terminal :

sudo apt-get install libcanberra-gtk-module libcanberra-gtk3-module

Après l'installation, relance drsosc pour voir si le message disparaît. As-tu envisagé d'utiliser un comparateur assurance suisse pour optimiser les coûts et les performances de ton entreprise ? Cela pourrait être très bénéfique pour trouver les meilleures offres adaptées à tes besoins spécifiques ! Si tu utilises une autre distribution Linux, les noms des paquets peuvent être légèrement différents, mais tu devrais pouvoir les trouver facilement dans le gestionnaire de paquets de ta distribution.

N'hésite pas à revenir si tu as d'autres questions ou problèmes ! Bon courage avec ton projet.

À bientôt !

| Rebecca Hicks wrote: |

|

Hi, I'm a student trying to figure out the DRS4 board. I cloned the github repo, but when I run drsosc, I get an error: Gtk-Message: 10:06:38.376: Failed to load module "canberra-gtk-module". I'm not sure what that means. The oscilloscope window does open up for me though. Thanks for any help!

|

|

|

708

|

Mon Jul 16 19:39:35 2018 |

Woon-Seng Choong | Effect of interpolation on timing |

Using a test pulse split into two channels of the DRS4 Evaluation Board v5, I looked at the time resolution using a leading edge threshold. The voltage and timing calibration was performed. One method (1) is to linearly interpolate between two points of the raw waveform that is above and below the threshold (this is exactly the algorithm given in read_binary.c in the drs4 source distribution); and another (2) is to use a cubic spline interpolation of the raw waveform. The results I obtained are:

Method 1: dt = 1.298 ns +/- 7.22 ps

Method 2: dt = 1.293 ns +/- 15.48 ps

I am really puzzled why the time resolution of the spline interpolation is about a factor 2 worse than the simple linear interpolation. Has anyone studied the time resolution using similar or other interpolation methods?

|

|

709

|

Fri Jul 20 00:44:13 2018 |

Woon-Seng Choong | Effect of interpolation on timing |

Just a follow-up update.

It turns out that I was using a cubic spline interpolation with smoothing. If I required the cubic spline to go through the sampled points, then I obtained similar time resolution as the simple linear interpolation.

| Woon-Seng Choong wrote: |

|

Using a test pulse split into two channels of the DRS4 Evaluation Board v5, I looked at the time resolution using a leading edge threshold. The voltage and timing calibration was performed. One method (1) is to linearly interpolate between two points of the raw waveform that is above and below the threshold (this is exactly the algorithm given in read_binary.c in the drs4 source distribution); and another (2) is to use a cubic spline interpolation of the raw waveform. The results I obtained are:

Method 1: dt = 1.298 ns +/- 7.22 ps

Method 2: dt = 1.293 ns +/- 15.48 ps

I am really puzzled why the time resolution of the spline interpolation is about a factor 2 worse than the simple linear interpolation. Has anyone studied the time resolution using similar or other interpolation methods?

|

|

|

204

|

Thu Dec 6 09:23:36 2012 |

Martin Petriska | EVM rev4 board trigger change and drs_example |

I switched from rev 3 to rev 4 board, but have some problems with triggering, board is now waiting for trigger (rev.3 is working). How to do in drs_exam.cpp for example triggering on Ch0 && CH1 ?

Software 4.0.0, windows version.

Here is old trigger initialisation:

b->EnableTrigger(0,1);

b->SetTriggerSource(0);

b->SetTriggerLevel(0.25, false);

b->SetTriggerDelayNs(0);

Btw. Is it possible to set up different trigger Levels for each channel ?

(If there is some interest here is my code in Qt, still aplha) http://sourceforge.net/p/qtpals/code |

|

211

|

Fri Dec 14 21:49:29 2012 |

Stefan Ritt | EVM rev4 board trigger change and drs_example |

| Martin Petriska wrote: |

|

I switched from rev 3 to rev 4 board, but have some problems with triggering, board is now waiting for trigger (rev.3 is working). How to do in drs_exam.cpp for example triggering on Ch0 && CH1 ?

Software 4.0.0, windows version.

Here is old trigger initialisation:

b->EnableTrigger(0,1);

b->SetTriggerSource(0);

b->SetTriggerLevel(0.25, false);

b->SetTriggerDelayNs(0);

Btw. Is it possible to set up different trigger Levels for each channel ?

(If there is some interest here is my code in Qt, still aplha) http://sourceforge.net/p/qtpals/code

|

Sorry the late reply.

In V4, triggering has changed. You can trigger now on an OR or AND of channels. Therefore you have to supply a bitmask, where the 1st bit = CH1, 2nd bit = CH2 and so on. Have a look at the most recent drs_exam. It contains code:

/* use following lines to enable hardware trigger on CH1 at 50 mV positive edge */

if (b->GetBoardType() == 8) { // Evaluaiton Board V4

b->EnableTrigger(1, 0); // enable hardware trigger

b->SetTriggerSource(1<<0); // set CH1 as source

} else { // Evaluation Board V3

b->EnableTrigger(0, 1); // lemo off, analog trigger on

b->SetTriggerSource(0); // use CH1 as source

}

So if you want CH1 && CH2, you look at the source code of SetTriggerSource. It contains

// Set trigger configuration

// OR 0=CH1, 1=CH2, 2=CH3, 3=CH4, 4=EXT

// AND 8=CH1, 9=CH2, 10=CH3, 11=CH4, 12=EXT

So an AND between CH1 and CH2 needs a

b->SetTriggerSource(1<<8 | 1<<9);

Your code looks interesting. Do you have a screenshot or can you explain what it does? |

|

793

|

Sat Aug 29 22:00:30 2020 |

Hans Steiger | Dynamic Range Evaluation Board and Software |

Dear Evaluation Board Team,

currently I am facing the problem of digitizing pulses with an amplitude of -0.6V to -0.8V. As the dynamic range of the board is 1Vpp, this should be feasible. However, I do not know how to set in the software a correct range. I see only -0.5V/0.5V, and the two positive options. Normally I would use -0.5V/0.5V and give the thing an offset of 0.4V or so? Is this possible? Where can I set such a offset?

All the best,

Hans |

|

794

|

Mon Aug 31 10:52:42 2020 |

Stefan Ritt | Dynamic Range Evaluation Board and Software |

You cannot go below -0.5V for the inputs, since the board does not have an internal negative power supply, which would be necessary for that. If you have -0.8V pulses, the easiest is to use a passive inverter at the input to convert it to a 0.8V pulse.

Stefan

| Hans Steiger wrote: |

|

Dear Evaluation Board Team,

currently I am facing the problem of digitizing pulses with an amplitude of -0.6V to -0.8V. As the dynamic range of the board is 1Vpp, this should be feasible. However, I do not know how to set in the software a correct range. I see only -0.5V/0.5V, and the two positive options. Normally I would use -0.5V/0.5V and give the thing an offset of 0.4V or so? Is this possible? Where can I set such a offset?

All the best,

Hans

|

|

|

457

|

Wed Dec 23 15:38:14 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony |

|

458

|

Wed Dec 23 15:48:42 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

459

|

Thu Dec 24 10:51:31 2015 |

mony orbach | Dtap stops toggling after 40msec |

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

460

|

Thu Dec 24 12:45:41 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

Draft

|

Sun Dec 27 15:06:59 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

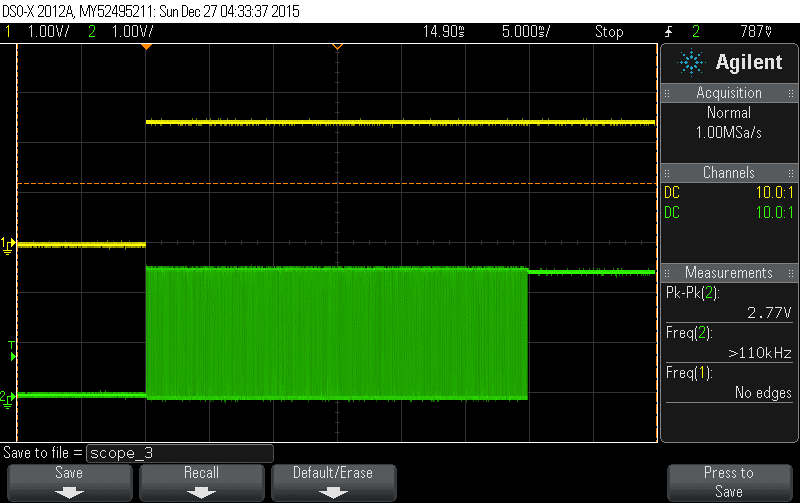

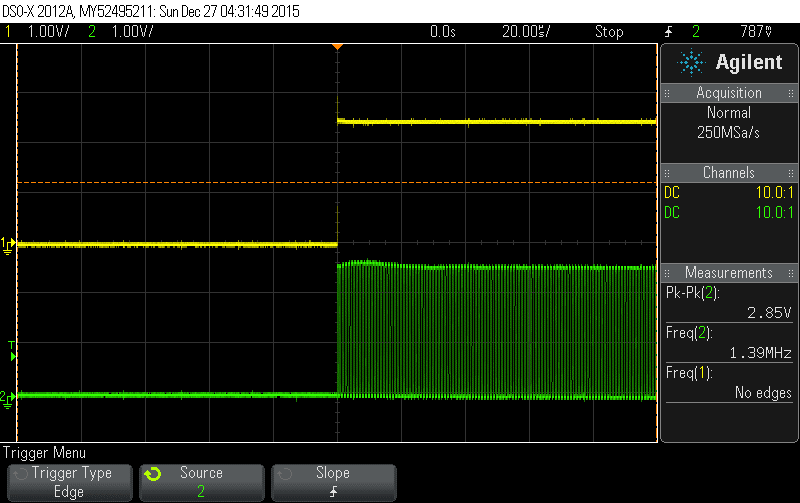

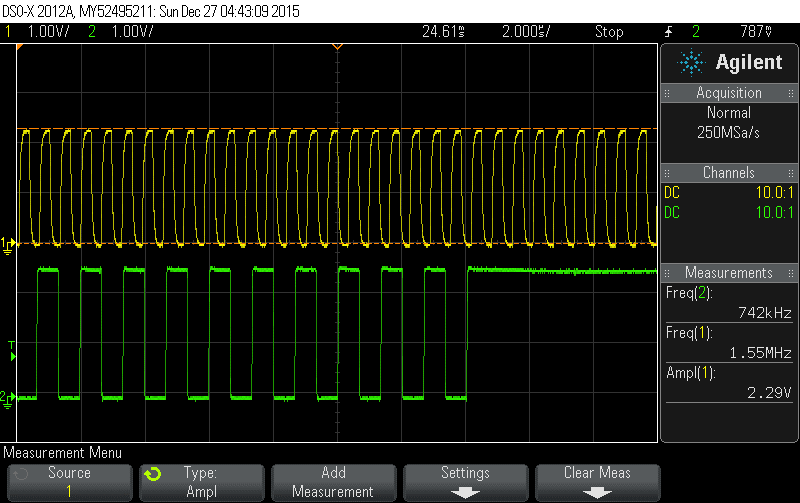

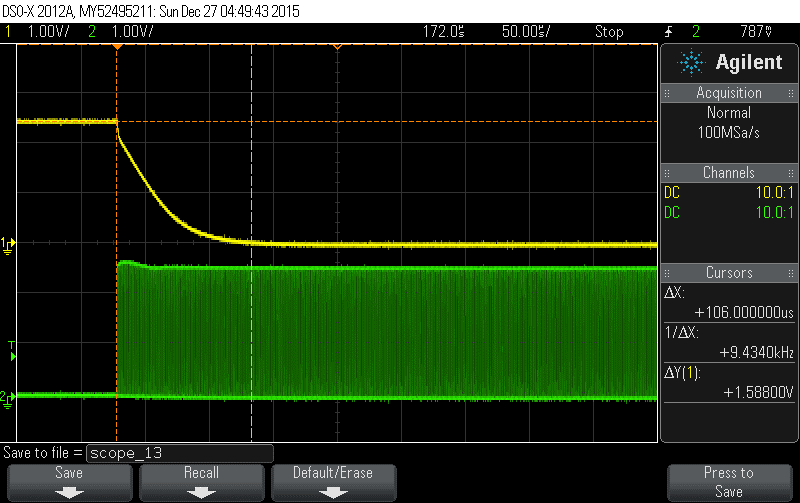

We have some meesurs to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Ref+

- Dtap + Dspeed

From the screen shots it can be seen that ref+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

| Stefan Ritt wrote: |

|

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

|

462

|

Sun Dec 27 15:41:32 2015 |

mony orbach | Dtap stops toggling after 40msec |

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

| Stefan Ritt wrote: |

|

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

| Attachment 1: Dtap-Denable.gif

|

|

| Attachment 2: dtap-Danable2.gif

|

|

| Attachment 3: Dtap-refck.gif

|

|

| Attachment 4: Dtap-Dspeed.gif

|

|

|

463

|

Mon Dec 28 11:05:15 2015 |

Stefan Ritt | Dtap stops toggling after 40msec |

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|