| ID |

Date |

Author |

Subject |

|

93

|

Sat Jun 19 10:09:18 2010 |

Jinhong Wang | DVDD Problem of DRS 4 |

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan

I designed the evaluation board for our experiment. On our boards, I encountered the similar problem when working on the PLL of DRS4. I compared the following two configuration process, which on with PLL locked, the other not,

Process1:

step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set DEnable high, thus do nothing but wait

I found DRS4 PLL working and locked.

Process 2:

Step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set Config. Register( "11111111" .of course, this step was not necessary, just to see whether SPI was working properly from DTAP when set to "11111110")

Step4: Set The read shift Register ( full read out mode)

Step5: Set DEnable high,

Step6: Set DWrite high , thus low it , and prepare to read the waveform.

Well, I found in this case, the PLL was not locked, I am sure there was no problem with my SPI configuration process of DRS4.

toggle from DTAP could be viewed, but not stable.

Any Suggestions ?

thanks.

|

So the main difference, if I understand correctly, is the setting of the Config Register. Actually I never tried that, I always went with the default settings (all "1"). What happens if you write "00000000"? You know Bit1 controls the PLL, maybe there is a bug and the signal needs to be inverted.

|

Hi, Stefan,

The problem was fixed by setting Reg_addr "1001" instead of "1111" when in idle state, I was confused. |

|

92

|

Fri Jun 18 11:45:18 2010 |

Stefan Ritt | DVDD Problem of DRS 4 |

| Jinhong Wang wrote: |

|

Hi Stefan

I designed the evaluation board for our experiment. On our boards, I encountered the similar problem when working on the PLL of DRS4. I compared the following two configuration process, which on with PLL locked, the other not,

Process1:

step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set DEnable high, thus do nothing but wait

I found DRS4 PLL working and locked.

Process 2:

Step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set Config. Register( "11111111" .of course, this step was not necessary, just to see whether SPI was working properly from DTAP when set to "11111110")

Step4: Set The read shift Register ( full read out mode)

Step5: Set DEnable high,

Step6: Set DWrite high , thus low it , and prepare to read the waveform.

Well, I found in this case, the PLL was not locked, I am sure there was no problem with my SPI configuration process of DRS4.

toggle from DTAP could be viewed, but not stable.

Any Suggestions ?

thanks.

|

So the main difference, if I understand correctly, is the setting of the Config Register. Actually I never tried that, I always went with the default settings (all "1"). What happens if you write "00000000"? You know Bit1 controls the PLL, maybe there is a bug and the signal needs to be inverted. |

|

91

|

Fri Jun 18 11:31:20 2010 |

Jinhong Wang | DVDD Problem of DRS 4 |

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence?

|

Yes; I used RSRLOAD to trigger readout of all channels in parallel so the asymmetry between channels of the same chip is really a big puzzle. Also during reset DSPEED indeed goes to 2.5V, but after reset the PLL will not try to lock with the external reference clock and lower DSPEED. Instead the Domino circuit just oscillates at the highest frequency by itself.

A more confusing discovery is that the SRIN level before starting the Domino wave could affect the behavior of the PLL. I mean the level of SRIN when the chip is at A="1111" or "1010". Is SRIN supposed to influence the chip even in these standby or transparent modes?

|

Just some ideas:

- Is DENABLE really kept high all the time?

- Is DRESET only applied once during initialization, after that it should stay high

- Does REFCLK+/REFCLK- really toggle at the required sampling speed / 2048?

- Is the REFCLK really a good differential signal? Note that it must be biased properly since the DRS4 inputs are high impedance

- Is the Bit1 in the Config Register really at "1" to enable the PLL?

The only way the SRIN level could affect the PLL is if you address the Config Register (A="1100") and you clock in a few bits with SRCLK.

Have you thought about 'crazy' things such as:

- Defining the DRS4 chip wronly in your CAD software so that the pins are different from what you think?

- Some soldering problem of the DRS4 chips (we had this in the past) so that some pins are not connected at all and others have shorts

I guess you checked most of the things, so I'm just wildly guessing in order to stimulate some thoughts.

The ultimate check would be to get one of the evaluation boards (I sent a few to Jean-Francois Genat some time ago...) and compare the DRS4 signals pin by pin.

|

Hi Stefan

I designed the evaluation board for our experiment. On our boards, I encountered the similar problem when working on the PLL of DRS4. I compared the following two configuration process, which on with PLL locked, the other not,

Process1:

step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set DEnable high, thus do nothing but wait

I found DRS4 PLL working and locked.

Process 2:

Step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set Config. Register( "11111111" .of course, this step was not necessary, just to see whether SPI was working properly from DTAP when set to "11111110")

Step4: Set The read shift Register ( full read out mode)

Step5: Set DEnable high,

Step6: Set DWrite high , thus low it , and prepare to read the waveform.

Well, I found in this case, the PLL was not locked, I am sure there was no problem with my SPI configuration process of DRS4.

toggle from DTAP could be viewed, but not stable.

Any Suggestions ?

thanks. |

|

88

|

Tue Jun 1 13:36:18 2010 |

Stefan Ritt | High Frequency Input for DRS |

| Hao Huan wrote: |

|

Hi Stefan,

I read in the DRS datasheet that the bandwidth for the transparent mode OUT+ is only 200MHz which I think cannot be improved by any active input buffer; so if you want to operate the chip for really high frequency input, would it be better to feed on-board discriminators not from the output of DRS but from the input end?

Thanks!

|

First, the 200 MHz is not correct. Table 1 clearly states ANALOG OUTPUTS - Bandwidth (-3dB): 50 MHz. This is also shown in plot 11 (revision 0.9). But that does not necessarily mean that you have to drive your discriminators from the input of the DRS4 chip. If you use this for triggering, a 1-2 ns timing jitter does not matter, since stopping the domino wave anyhow has a 3-4 cell jitter. If you send a very fast signal though a 50 MHz low pass filter, the timing anyhow doe not change, only the slope of your signal gets lower, so you are more sensitive to noise, which in turn causes the 1-2 ns timing jitter. But I personally would not worry about that too much. Putting any signal splitting components in the input path would reduce the input bandwidth, which would be much more of an issue. |

|

87

|

Wed May 26 19:18:09 2010 |

Hao Huan | High Frequency Input for DRS | Hi Stefan,

I read in the DRS datasheet that the bandwidth for the transparent mode OUT+ is only 200MHz which I think cannot be improved by any active input buffer; so if you want to operate the chip for really high frequency input, would it be better to feed on-board discriminators not from the output of DRS but from the input end?

Thanks!

|

|

86

|

Wed May 19 09:16:02 2010 |

Stefan Ritt | DVDD Problem of DRS 4 |

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence?

|

Yes; I used RSRLOAD to trigger readout of all channels in parallel so the asymmetry between channels of the same chip is really a big puzzle. Also during reset DSPEED indeed goes to 2.5V, but after reset the PLL will not try to lock with the external reference clock and lower DSPEED. Instead the Domino circuit just oscillates at the highest frequency by itself.

A more confusing discovery is that the SRIN level before starting the Domino wave could affect the behavior of the PLL. I mean the level of SRIN when the chip is at A="1111" or "1010". Is SRIN supposed to influence the chip even in these standby or transparent modes?

|

Just some ideas:

- Is DENABLE really kept high all the time?

- Is DRESET only applied once during initialization, after that it should stay high

- Does REFCLK+/REFCLK- really toggle at the required sampling speed / 2048?

- Is the REFCLK really a good differential signal? Note that it must be biased properly since the DRS4 inputs are high impedance

- Is the Bit1 in the Config Register really at "1" to enable the PLL?

The only way the SRIN level could affect the PLL is if you address the Config Register (A="1100") and you clock in a few bits with SRCLK.

Have you thought about 'crazy' things such as:

- Defining the DRS4 chip wronly in your CAD software so that the pins are different from what you think?

- Some soldering problem of the DRS4 chips (we had this in the past) so that some pins are not connected at all and others have shorts

I guess you checked most of the things, so I'm just wildly guessing in order to stimulate some thoughts.

The ultimate check would be to get one of the evaluation boards (I sent a few to Jean-Francois Genat some time ago...) and compare the DRS4 signals pin by pin. |

|

85

|

Wed May 19 02:24:12 2010 |

Hao Huan | DVDD Problem of DRS 4 |

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence?

|

Yes; I used RSRLOAD to trigger readout of all channels in parallel so the asymmetry between channels of the same chip is really a big puzzle. Also during reset DSPEED indeed goes to 2.5V, but after reset the PLL will not try to lock with the external reference clock and lower DSPEED. Instead the Domino circuit just oscillates at the highest frequency by itself.

A more confusing discovery is that the SRIN level before starting the Domino wave could affect the behavior of the PLL. I mean the level of SRIN when the chip is at A="1111" or "1010". Is SRIN supposed to influence the chip even in these standby or transparent modes? |

|

84

|

Tue May 18 09:24:02 2010 |

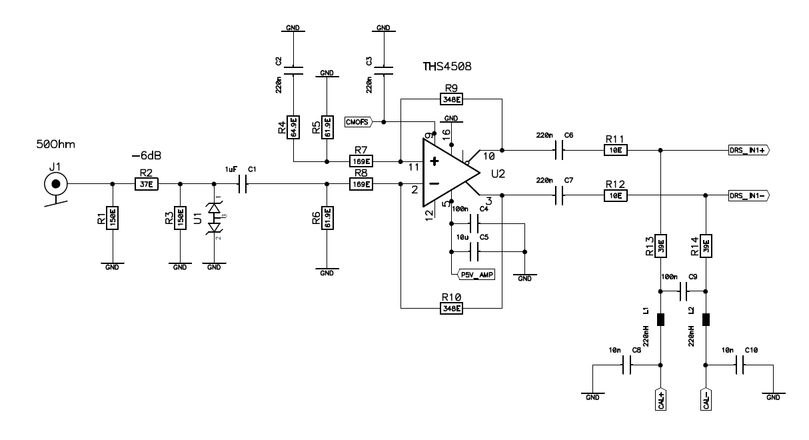

Stefan Ritt | Reference design for DRS4 active input buffer | The design of high frequency differential input stages with the DRS4 is a challenge, since the chip draws quite some current at the input (up to 1 mA at 5 GSPS), which must be sourced by the input buffer. A simple transformer as used in the DRS4 Evaluation Board 2.0 limits the bandwidth to 220 MHz. In meantime two active input stages have been worked out and successfully been tested, both utilizing the THS4508 differential amplifier. The first design is AC-coupled and uses less power, the second design is DC-coupled and uses more power with the benefit of delivering a higher bandwidth.

Both designs use a clamping diode at the input as a protection against high voltage spikes at the input. We used a RCLAMP0502B diode from SEMTECH, but any fast voltage suppressor diode will do the job.

The CMOFS input to the THS4508 set the common mode of the differential amplifier. In the AC version the level is set to mid-rail (2.5V), in the DC version it's set to 1.8V to match the input range of the DRS4.

The CAL+ and CAL- signals are used to bias the inputs to a well-defined DC level and can also be used to calibrate the chip. For bipolar inputs, they are both set to 0.8V. A positive 0.5V input pulse then drives DRS_IN+ to (0.8+0.25)V = 1.05V and DRS_IN- to (0.8-0.25)V = 0.55V. A negative 0.5V pulse then drives then DRS_IN+ to 0.55V and DRS_IN- to 1.05V. With ROFS=1.6V, the full dynamic range of the DRS4 is then used. Note that the THS4508 has a gain of 2, and the input has a -6dB voltage divider to compensate for that. To use other input ranges, such as -1V...0V, the CAL+ and CAL- signals can be adjusted accordingly. Note that the inputs of the DRS4 must always be between 0.1V and 1.5V.

AC-coupled version

(click to enlarge)

Power supply: +5 V 40 mA

Bandwidth (-3dB): 600 MHz

CMOFS: 2.5 V

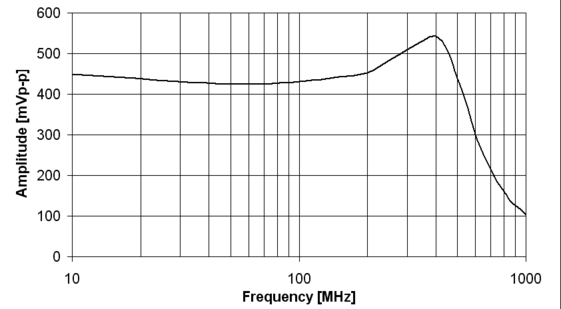

Transfer function:

(click to enlarge)

The transfer function was measured by applying a fixed amplitude sine wave to the input, and measuring the peak-to-peak value of the read out waveform with the DRSOsc application.

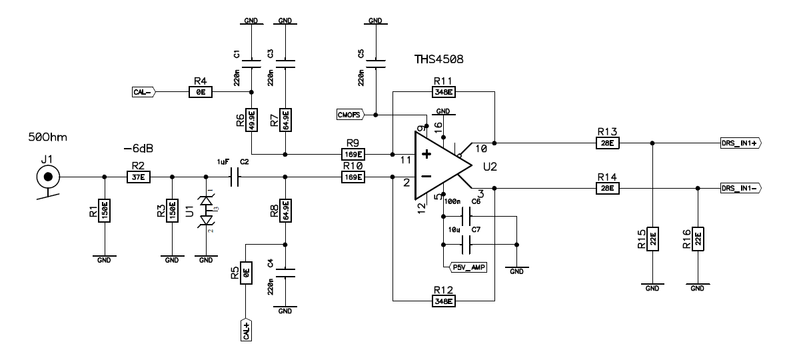

DC-coupled Version

The DC-coupled version has a slightly higher power consumption since there is a constant current flowing through the output into the DRS4 chip. On the other hand, the bandwidth is a bit higher and the peaking around 400 MHz is a bit smaller. The input is still AC-coupled, so both positive and negative pulses can be accepted.

(click to enlarge)

Power supply: +5 V 115 mA

Bandwidth (-3dB): 800 MHz

CMOFS: 1.8 V

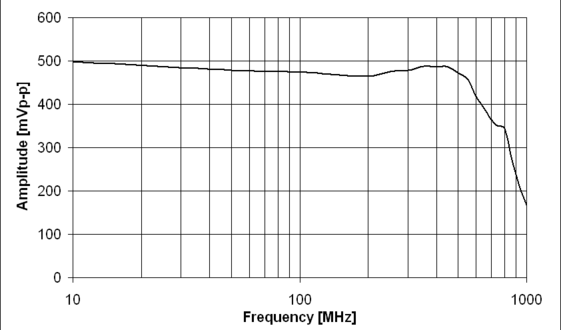

Transfer function:

(click to enlarge)

Achievable performance

With the active input stage, much faster rise- and fall times can be achieved. Following picture shows a signal from a external clock having a fall time of about 300 ps being recorded with the AC-coupled version of the active input stage. The fall time of the recorded signal is about 800 ps, which is about the minimum which can be achieved with the AC-coupled version. The DC-coupled version achieves about 700ps.

|

|

83

|

Tue May 18 08:23:07 2010 |

Stefan Ritt | DVDD Problem of DRS 4 |

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence? |

|

82

|

Tue May 18 01:47:59 2010 |

Hao Huan | DVDD Problem of DRS 4 |

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit? |

|

81

|

Fri May 14 08:40:14 2010 |

Stefan Ritt | DVDD Problem of DRS 4 |

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely. |

|

80

|

Thu May 13 19:14:27 2010 |

Hao Huan | DVDD Problem of DRS 4 | Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot! |

|

79

|

Wed May 12 16:26:12 2010 |

Stefan Ritt | DRS4 chip model |

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

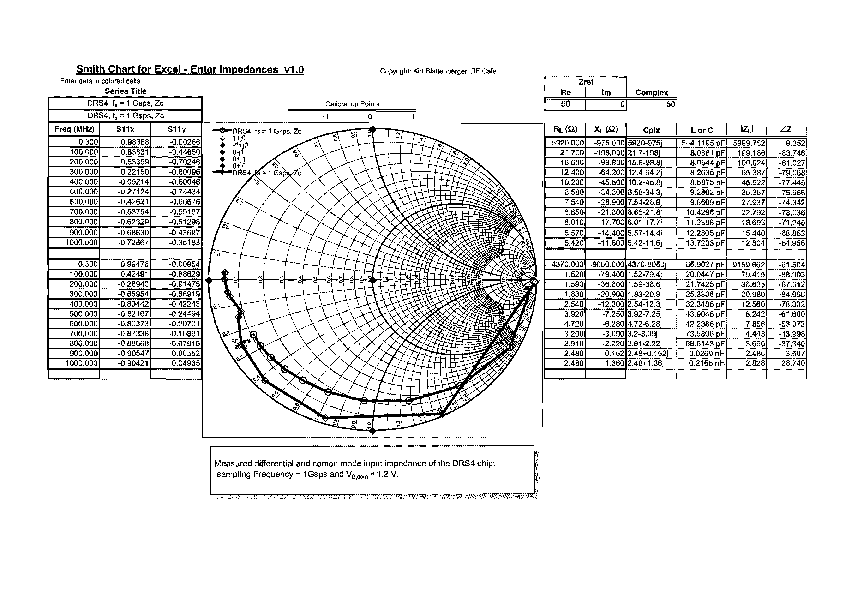

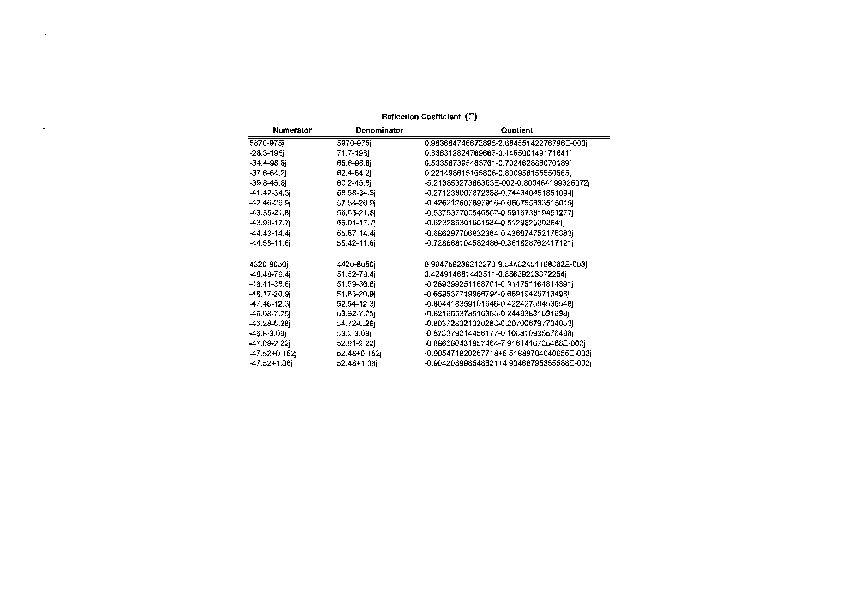

Please find attached the S-parameters.

|

Hi, we plan to do a time interpolating among the eight channels on a single chip to obtain a maximum 40 GSPS (or, maybe 30 GSPS ) sampling rate. Hence RF behavior of the anlog input is very important for us.

Will you give us some advice on the modeling of the anlog input circuit of the chip? Perhaps just the Spice model of the analog input?

The attached S parameters I found here is for fs =1 GSPS, what about fs=5GSPS?

thanks in advance,

Jinhong Wang (wangjinh@mail.ustc.edu.cn ; alleyor.wang@gmail.com)

|

To be honest, we never really succeeded to do any good simulation above let's say 500 MHz. We carefully tried to simulate the bond wire of the chip, the parasitic capacitances of the traces of the chip etc. but we always were off by a factor or two or so. Other groups reported the same problems. Some even did some 3D simulation model, without success. So our conclusion is that if you are interested in anything precise above 500 MHz, do a measurement.

So our current best design is with the THS4508. There is an AC coupled version going to 600 MHz, and a DC coupled version (uses more power) going to 800 MHz (-3dB). If you use passive inputs with a transformer for example, you can't go above 220 MHz. Next week I will publish both designs in this forum. |

|

78

|

Wed May 12 11:47:39 2010 |

Jinhong Wang | DRS4 chip model |

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters.

|

Hi, we plan to do a time interpolating among the eight channels on a single chip to obtain a maximum 40 GSPS (or, maybe 30 GSPS ) sampling rate. Hence RF behavior of the anlog input is very important for us.

Will you give us some advice on the modeling of the anlog input circuit of the chip? Perhaps just the Spice model of the analog input?

The attached S parameters I found here is for fs =1 GSPS, what about fs=5GSPS?

thanks in advance,

Jinhong Wang (wangjinh@mail.ustc.edu.cn ; alleyor.wang@gmail.com) |

|

77

|

Thu May 6 08:15:39 2010 |

Stefan Ritt | Random noise spec in datasheet |

| Ignacio Diéguez Estremera wrote: |

|

Hi,

According to DRS4's datasheet, the random noise is 0.35mVrms. Is this the input equivalent noise voltage? It is computed over the 0-950MHz frequency band?

Regards.

|

You cannot compare the DRS4 noise directly with an amplifier for example. The noise mainly comes from variations of the charge injection into the storage cells, and some noise during the readout process, which happens in a completely different frequency domain than the sampling.

So what I did is to keep the inputs open, measure a 1024-bin waveform, and compute the RMS of this waveform. So I believe that this is kind of equivalent noise voltage from 1-950 MHz. It does not start from zero since very low frequency noise (like 50 Hz) just causes a baseline shift and does not influence the RMS, but this is not so important since in most applications people do an event-by-event baseline subtraction to get rid of low frequency noise in their apparatus. The 0.35 mV RMS also depend on the electronics around the chip. On our USB evaluation board the noise it typically smaller (0.31 mV RMS), while in some VME board we measure 0.42 mV RMS. If you do the perfect analog design around the chip, you can maybe push this maybe even lower. |

|

76

|

Wed May 5 22:30:50 2010 |

Ignacio Di�guez Estremera | Random noise spec in datasheet | Hi,

According to DRS4's datasheet, the random noise is 0.35mVrms. Is this the input equivalent noise voltage? It is computed over the 0-950MHz frequency band?

Regards. |

|

75

|

Tue May 4 16:23:16 2010 |

Ignacio Di�guez Estremera | DRS4 chip model |

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters.

|

Thanks :-) |

|

74

|

Tue May 4 11:26:21 2010 |

Stefan Ritt | DRS4 chip model |

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters. |

| Attachment 1: DRS4_S-Parameter.pdf

|

|

|

73

|

Mon May 3 23:21:55 2010 |

Ignacio Di�guez Estremera | DRS4 chip model |

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards.

|

I just checked and realized that we are not allowed to give out the "huge" model since it contains parameters from the chip manufacturer's library which are confidentially.

|

Thank you for the effort anyway.

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-) |

|

72

|

Mon May 3 17:10:29 2010 |

Stefan Ritt | DRS4 chip model |

| Ignacio Diéguez Estremera wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards.

|

I just checked and realized that we are not allowed to give out the "huge" model since it contains parameters from the chip manufacturer's library which are confidentially. |

|