Wed May 11 15:48:57 2016, SANDJONG Saturnin Orly, Probléme de Calibration de la DRS4 Wed May 11 15:48:57 2016, SANDJONG Saturnin Orly, Probléme de Calibration de la DRS4

|

Bonjour, Je suis en stage dans un laboratoire ou on utilise pour echantillonnage des données, une cartes DRS4 5GSPS avec 1024 cell, mon probléme réside dans la partie Calibration en tension selon l'article "Novel Calibration Method for Switched Capacitor Arrays Enables Time Measurements with Sub-Picosecond Resolution".

En fait je ne comprends pas précisément ces 3 parties de la calibration en tension. Quelqu'un pourras t-il s'il vous plait m'expliquer assez clairement avec des exemples comment il faut s'y prendre?

Merci et bien Cordialement. |

Mon Feb 29 13:33:06 2016, Dmitry Hits, two DRS4 boards configuration with 2048 samples each Mon Feb 29 13:33:06 2016, Dmitry Hits, two DRS4 boards configuration with 2048 samples each

|

Dear Stefan,

I daisy-chained two boards (master sn#: 2514 - slave sn#: 2513) each with 2048 samples. However, when I use drsosc and put check mark in "configure multi-board daisy-chain" I see only 1024 samples. Namely, the first 1024 samples, the last part is missing. When I remove this check mark, I see all 2048 samples. Is there a simple software fix for this or is it a more involved firmware limitation?

Other parameters: software version: 5.0.4, firmware version 21305, configured for 0.7 GSPS, display at 500 ns/div

Thank you,

Dmitry Hits. |

Mon Feb 29 14:09:21 2016, Stefan Ritt, two DRS4 boards configuration with 2048 samples each Mon Feb 29 14:09:21 2016, Stefan Ritt, two DRS4 boards configuration with 2048 samples each

|

The multi-board mode has never been tested with 2048 samples, so is very likely not to work. I don't know yet how much work this will be to fix, but I'm on a business trip the next three weeks and probably will only have time to look at it when I return.

Stefan

| Dmitry Hits wrote: |

|

Dear Stefan,

I daisy-chained two boards (master sn#: 2514 - slave sn#: 2513) each with 2048 samples. However, when I use drsosc and put check mark in "configure multi-board daisy-chain" I see only 1024 samples. Namely, the first 1024 samples, the last part is missing. When I remove this check mark, I see all 2048 samples. Is there a simple software fix for this or is it a more involved firmware limitation?

Other parameters: software version: 5.0.4, firmware version 21305, configured for 0.7 GSPS, display at 500 ns/div

Thank you,

Dmitry Hits.

|

|

Mon May 2 14:31:28 2016, Dmitry Hits, two DRS4 boards configuration with 2048 samples each Mon May 2 14:31:28 2016, Dmitry Hits, two DRS4 boards configuration with 2048 samples each

|

Hi Stefan

Any chance you have time to fix the software for multiboard configuration with 2048 samples each. I tried 5.0.5, but drsosc still shows only half of the waveform.

Dmitry

| Stefan Ritt wrote: |

|

The multi-board mode has never been tested with 2048 samples, so is very likely not to work. I don't know yet how much work this will be to fix, but I'm on a business trip the next three weeks and probably will only have time to look at it when I return.

Stefan

| Dmitry Hits wrote: |

|

Dear Stefan,

I daisy-chained two boards (master sn#: 2514 - slave sn#: 2513) each with 2048 samples. However, when I use drsosc and put check mark in "configure multi-board daisy-chain" I see only 1024 samples. Namely, the first 1024 samples, the last part is missing. When I remove this check mark, I see all 2048 samples. Is there a simple software fix for this or is it a more involved firmware limitation?

Other parameters: software version: 5.0.4, firmware version 21305, configured for 0.7 GSPS, display at 500 ns/div

Thank you,

Dmitry Hits.

|

|

|

Thu Apr 28 15:47:53 2016, Stefan Ritt, New software version and binary format Thu Apr 28 15:47:53 2016, Stefan Ritt, New software version and binary format

|

A new software version 5.0.5 has been released today. This fixes a few bugs in multi-board configurations, and adds saving of the scaler values into XML and binary files. Please note that the binary file format has been changed for that. The new format is described in an updated manual (page 25), and reflected in a new read_binary.cpp program contained in the distribution.

/Stefan |

Wed Apr 27 20:04:12 2016, Abaz Kryemadhi, Best settings for time measurements Wed Apr 27 20:04:12 2016, Abaz Kryemadhi, Best settings for time measurements

|

I am studing some pulses that are about 200-300 ns wide and a rise time of few ns, which settings would be best for coincidence time measurements?

In some preliminary work I found for 700 MegaS the time measurement is better without time calibration (in -0.05 to 1V) rather than with time calibration in -0.5 to 0.5, my pulses are about 60 mV. Is it expected that always with time calibration time accuracy would be better or depends?

Also I use this code snippet to find time for channel 1 and the same idea for chan. 2.

// find peak in channel 1 above threshold

for (i=0 ; i<1022 ; i++)

if (waveform[0][i] < threshold1 && waveform[0][i+1] >= threshold1) {

tt1 = (threshold1-waveform[0][i])/(waveform[0][i+1]-waveform[0][i])*(time[0][i+1]-time[0][i])+time[0][i];

break;

}

Thanks!

Abaz |

Thu Apr 28 15:46:34 2016, Stefan Ritt, Best settings for time measurements Thu Apr 28 15:46:34 2016, Stefan Ritt, Best settings for time measurements

|

The DRS4 chip has been designed to work best at high sampling speeds. At 700 MSPS, the chip is at it's limit and timing is very poorr (ns?). In order to get good timing, run it at least at 2 GSPS.

Stefan

| Abaz Kryemadhi wrote: |

|

I am studing some pulses that are about 200-300 ns wide and a rise time of few ns, which settings would be best for coincidence time measurements?

In some preliminary work I found for 700 MegaS the time measurement is better without time calibration (in -0.05 to 1V) rather than with time calibration in -0.5 to 0.5, my pulses are about 60 mV. Is it expected that always with time calibration time accuracy would be better or depends?

Also I use this code snippet to find time for channel 1 and the same idea for chan. 2.

// find peak in channel 1 above threshold

for (i=0 ; i<1022 ; i++)

if (waveform[0][i] < threshold1 && waveform[0][i+1] >= threshold1) {

tt1 = (threshold1-waveform[0][i])/(waveform[0][i+1]-waveform[0][i])*(time[0][i+1]-time[0][i])+time[0][i];

break;

}

Thanks!

Abaz

|

|

Wed Apr 27 08:14:14 2016, Toshihiro Nonaka, serial number problem Wed Apr 27 08:14:14 2016, Toshihiro Nonaka, serial number problem

|

Dear all,

I'm using 3 DRS boards simultaneously and their serial numbers are 2169, 2170, 2172 respectively.

Recently however, I obtain serial number "0" by DRSBoard::GetBoardSerialNumber() for #2172 board.

Data taking can be done without any problems, but I'd like to know what is happening.

Any advice?

Thank you.

Toshihiro Nonaka |

Wed Apr 27 09:04:01 2016, Stefan Ritt, serial number problem Wed Apr 27 09:04:01 2016, Stefan Ritt, serial number problem

|

If dis- and reconnecting the board does not help, there is the (small) chance that the serial number got erased in the board. You can re-set it with the "drscl" command line tool:

$ drscl

Found DRS4 board 0 on USB, serial #0, firmware revision 21305

B0> serial 2172

| Toshihiro Nonaka wrote: |

|

Dear all,

I'm using 3 DRS boards simultaneously and their serial numbers are 2169, 2170, 2172 respectively.

Recently however, I obtain serial number "0" by DRSBoard::GetBoardSerialNumber() for #2172 board.

Data taking can be done without any problems, but I'd like to know what is happening.

Any advice?

Thank you.

Toshihiro Nonaka

|

|

Wed Apr 27 09:51:37 2016, Toshihiro Nonaka, serial number problem Wed Apr 27 09:51:37 2016, Toshihiro Nonaka, serial number problem

|

The serial number has been fixed by using drscl. Thank you!

| Stefan Ritt wrote: |

|

If dis- and reconnecting the board does not help, there is the (small) chance that the serial number got erased in the board. You can re-set it with the "drscl" command line tool:

$ drscl

Found DRS4 board 0 on USB, serial #0, firmware revision 21305

B0> serial 2172

| Toshihiro Nonaka wrote: |

|

Dear all,

I'm using 3 DRS boards simultaneously and their serial numbers are 2169, 2170, 2172 respectively.

Recently however, I obtain serial number "0" by DRSBoard::GetBoardSerialNumber() for #2172 board.

Data taking can be done without any problems, but I'd like to know what is happening.

Any advice?

Thank you.

Toshihiro Nonaka

|

|

|

Fri Apr 15 12:58:46 2016, Konstantin Gusev, DRS4 purchase information Fri Apr 15 12:58:46 2016, Konstantin Gusev, DRS4 purchase information

|

Hi,

I can't contact with Anita Van Loon about DSR4 chip's price and delivery.

Did you still sell it? Can you provide me this information? |

Tue Apr 26 13:42:42 2016, Stefan Ritt, DRS4 purchase information Tue Apr 26 13:42:42 2016, Stefan Ritt, DRS4 purchase information

|

Just be patient. Anita is not at work this week.

| Konstantin Gusev wrote: |

|

Hi,

I can't contact with Anita Van Loon about DSR4 chip's price and delivery.

Did you still sell it? Can you provide me this information?

|

|

Thu Apr 21 22:16:43 2016, Kyle Weinfurther, Negative fCellDT values from GetTimeCalibration() Thu Apr 21 22:16:43 2016, Kyle Weinfurther, Negative fCellDT values from GetTimeCalibration()

|

Hello Stefan,

I am using four DRS4 v5 eval boards to digitize 16 channels of data. I have recently changed from saving the timing information of the waveform using GetTime() to GetTimeCalibration(). When changing over, I noticed that some values for fCellDT for cell 498 are negative. Over the 16 channels used, 4 of them have negative time bin widths for cell 498 while the other 12 channels are very close to 0 (in the ~10 ps range). One of the eval boards has no negative fCellDT whereas the other three boards have one or two channels with negative values.

Upon further inspection, I checked the time between samples of GetTime() and found the same results in cell 498. After finding this, I did a timing calibration again with CalibrateTiming() even though in a different post on the discussion forum you said it was valid for a wide range of temperatures and a long time (years). This still allowed the negative fCellDT values to persist.

Is this a common occurance? If so, is there a method to fix this issue? Is there a reason for cell 498 to have a small value for fCellDT? I searched the discussion forum and did not find anything relating to this issue.

Attached are a couple waveform traces using GetTime() zoomed in on cell 498.

Thanks,

Kyle Weinfurther |

Sat Apr 23 12:33:17 2016, Daniel Stricker-Shaver, Negative fCellDT values from GetTimeCalibration() Sat Apr 23 12:33:17 2016, Daniel Stricker-Shaver, Negative fCellDT values from GetTimeCalibration()

|

Hi Kyle,

If I remember right the negative sampling width happens only for 498 and at high sampling speeds. It is described in a paper from Stefan:

http://arxiv.org/pdf/1405.4975.pdf

or

“Novel Calibration Method for Switched Capacitor Arrays Enables Time Measurements With Sub-Picosecond Resolution”( IEEE Transactions on Nuclear Science 61 (2014),Nr. 6, 3607–3617)

| Kyle Weinfurther wrote: |

|

Hello Stefan,

I am using four DRS4 v5 eval boards to digitize 16 channels of data. I have recently changed from saving the timing information of the waveform using GetTime() to GetTimeCalibration(). When changing over, I noticed that some values for fCellDT for cell 498 are negative. Over the 16 channels used, 4 of them have negative time bin widths for cell 498 while the other 12 channels are very close to 0 (in the ~10 ps range). One of the eval boards has no negative fCellDT whereas the other three boards have one or two channels with negative values.

Upon further inspection, I checked the time between samples of GetTime() and found the same results in cell 498. After finding this, I did a timing calibration again with CalibrateTiming() even though in a different post on the discussion forum you said it was valid for a wide range of temperatures and a long time (years). This still allowed the negative fCellDT values to persist.

Is this a common occurance? If so, is there a method to fix this issue? Is there a reason for cell 498 to have a small value for fCellDT? I searched the discussion forum and did not find anything relating to this issue.

Attached are a couple waveform traces using GetTime() zoomed in on cell 498.

Thanks,

Kyle Weinfurther

|

|

Tue Apr 26 09:54:16 2016, Stefan Ritt, Negative fCellDT values from GetTimeCalibration() Tue Apr 26 09:54:16 2016, Stefan Ritt, Negative fCellDT values from GetTimeCalibration()

|

I just realized that the negative bin widht is not explicitly mentioned in the quoted paper. So let me explain it here:

The negative value of cell 498 is correct and "real" in the sense that the signal is first captured in cell 498 and later in cell 497. This is due to the exact layout of the cells on the chip and the input signal. Cell 498 is simply much closer to the input, so sees the signal earlier than cell 497, even if it's triggerd after cell 497. So nothing to worry about.

Stefan

| Daniel Stricker-Shaver wrote: |

|

Hi Kyle,

If I remember right the negative sampling width happens only for 498 and at high sampling speeds. It is described in a paper from Stefan:

http://arxiv.org/pdf/1405.4975.pdf

or

“Novel Calibration Method for Switched Capacitor Arrays Enables Time Measurements With Sub-Picosecond Resolution”( IEEE Transactions on Nuclear Science 61 (2014),Nr. 6, 3607–3617)

| Kyle Weinfurther wrote: |

|

Hello Stefan,

I am using four DRS4 v5 eval boards to digitize 16 channels of data. I have recently changed from saving the timing information of the waveform using GetTime() to GetTimeCalibration(). When changing over, I noticed that some values for fCellDT for cell 498 are negative. Over the 16 channels used, 4 of them have negative time bin widths for cell 498 while the other 12 channels are very close to 0 (in the ~10 ps range). One of the eval boards has no negative fCellDT whereas the other three boards have one or two channels with negative values.

Upon further inspection, I checked the time between samples of GetTime() and found the same results in cell 498. After finding this, I did a timing calibration again with CalibrateTiming() even though in a different post on the discussion forum you said it was valid for a wide range of temperatures and a long time (years). This still allowed the negative fCellDT values to persist.

Is this a common occurance? If so, is there a method to fix this issue? Is there a reason for cell 498 to have a small value for fCellDT? I searched the discussion forum and did not find anything relating to this issue.

Attached are a couple waveform traces using GetTime() zoomed in on cell 498.

Thanks,

Kyle Weinfurther

|

|

|

Mon Mar 21 10:38:27 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run Mon Mar 21 10:38:27 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run

|

Dear Stefan Ritt,

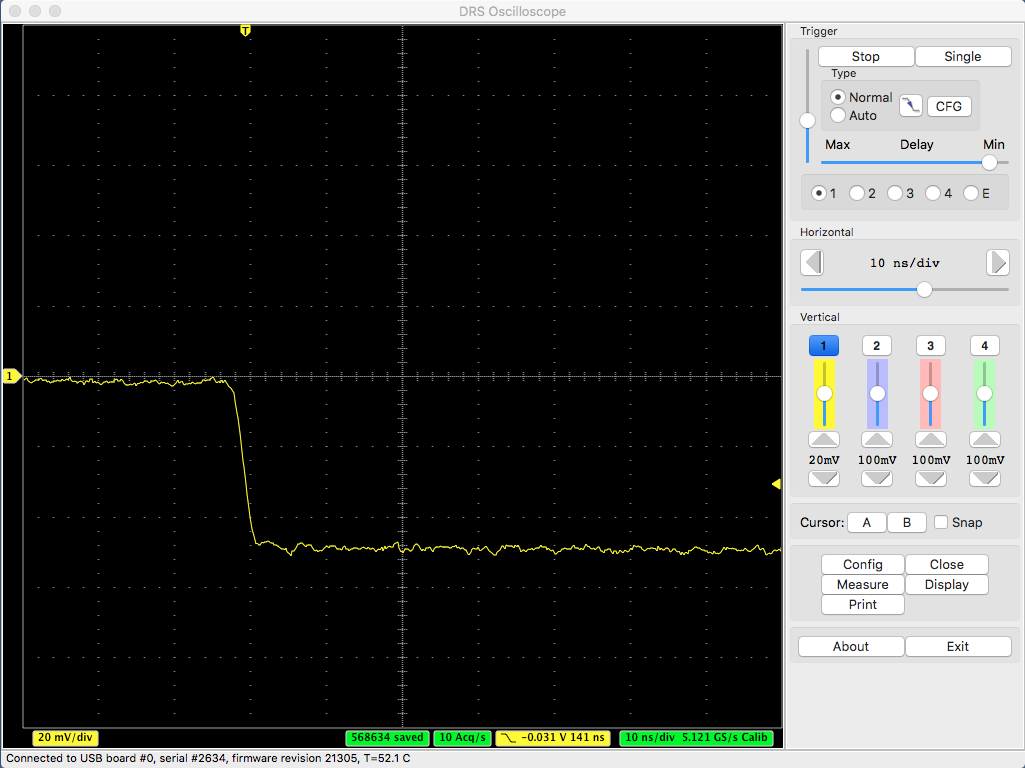

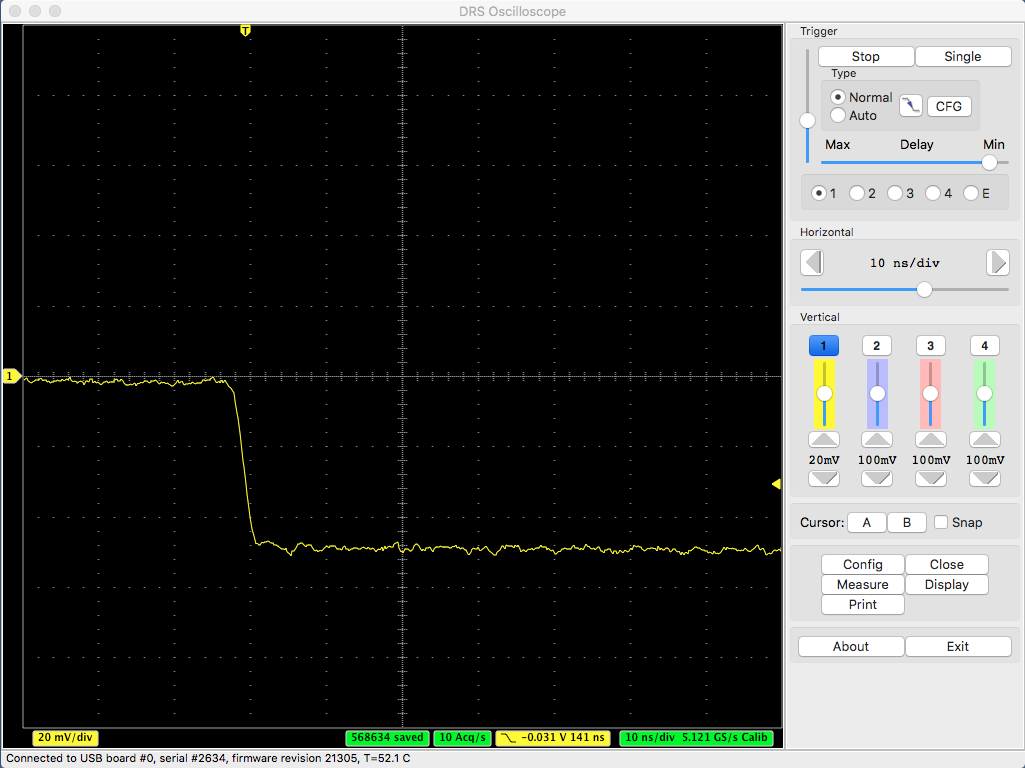

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

Mon Apr 4 11:31:34 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run Mon Apr 4 11:31:34 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run

|

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

Mon Apr 4 11:41:26 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run Mon Apr 4 11:41:26 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run

|

Dear Stefan Ritt,

Yes I use Windows 7, If the DRS Oscilloscope program stays on for a couple of hours without saving the data, the problem will occur. It seems it happens more often when there is data writing and when the rate of events is slow, about 100 events per second, at high rates it almost doesn't happen. Can it be temperature related?

Daniel

| Stefan Ritt wrote: |

|

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

|

Mon Apr 4 12:08:15 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run Mon Apr 4 12:08:15 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run

|

Then it seems that there is some USB communication problem. I heard this also from other people, that the USB data transfer under Windows has sometimes problems. I develop and run the board under Mac OSX, and there the same software runs for days without problem. So I guess it's related to the underlying libusb lib which is used by the DRS oscilloscope, on which I have no influence. So the only advice I can give is to take shorter series of data. Anyhow the board is not considered a full DAQ system, just an "evaluation board" which means one can try the DRS4 chip and play with it. For serious business one should build own electronics with the chip. Anyhow we are currently developping an Ethernet board which allows much faster acquisition rates, so USB will be obsolete some day. Nevertheless I will try to reproduce your problem and see if I can do anything. At what trigger rate does it show up most prominently?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

Yes I use Windows 7, If the DRS Oscilloscope program stays on for a couple of hours without saving the data, the problem will occur. It seems it happens more often when there is data writing and when the rate of events is slow, about 100 events per second, at high rates it almost doesn't happen. Can it be temperature related?

Daniel

| Stefan Ritt wrote: |

|

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

|

|

Tue Apr 5 16:08:59 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run Tue Apr 5 16:08:59 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run

|

I tried this night to run the board at a 10 Hz rate with an external pulser, without writing, and it did not freeze after ~14 hours of running on Mac OSX. This night I will try again with writing.

Stefan

| Stefan Ritt wrote: |

|

Then it seems that there is some USB communication problem. I heard this also from other people, that the USB data transfer under Windows has sometimes problems. I develop and run the board under Mac OSX, and there the same software runs for days without problem. So I guess it's related to the underlying libusb lib which is used by the DRS oscilloscope, on which I have no influence. So the only advice I can give is to take shorter series of data. Anyhow the board is not considered a full DAQ system, just an "evaluation board" which means one can try the DRS4 chip and play with it. For serious business one should build own electronics with the chip. Anyhow we are currently developping an Ethernet board which allows much faster acquisition rates, so USB will be obsolete some day. Nevertheless I will try to reproduce your problem and see if I can do anything. At what trigger rate does it show up most prominently?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

Yes I use Windows 7, If the DRS Oscilloscope program stays on for a couple of hours without saving the data, the problem will occur. It seems it happens more often when there is data writing and when the rate of events is slow, about 100 events per second, at high rates it almost doesn't happen. Can it be temperature related?

Daniel

| Stefan Ritt wrote: |

|

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

|

|

|

Wed Apr 6 08:41:08 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run Wed Apr 6 08:41:08 2016, Stefan Ritt, DRS Oscilloscope freezing after a long run

|

Even with writing for one night no problem (see below). Have you checked how big your data file is? I guess there is a limit under Windows of 2 GB. If that's the case, you have to write shorter files.

|

Wed Apr 6 09:43:52 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run Wed Apr 6 09:43:52 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run

|

At hight rates I worked with files of up to 20 GB so I don't think this is the problem.

I will try to run it under Ubuntu and see if i can recreate the problem.

Thank you very much for the quick responses and help.

| Stefan Ritt wrote: |

|

Even with writing for one night no problem (see below). Have you checked how big your data file is? I guess there is a limit under Windows of 2 GB. If that's the case, you have to write shorter files.

|

|

Wed Apr 6 09:01:28 2016, Martin Petriska, DRS Oscilloscope freezing after a long run Wed Apr 6 09:01:28 2016, Martin Petriska, DRS Oscilloscope freezing after a long run

|

| Stefan Ritt wrote: |

|

I tried this night to run the board at a 10 Hz rate with an external pulser, without writing, and it did not freeze after ~14 hours of running on Mac OSX. This night I will try again with writing.

Stefan

| Stefan Ritt wrote: |

|

Then it seems that there is some USB communication problem. I heard this also from other people, that the USB data transfer under Windows has sometimes problems. I develop and run the board under Mac OSX, and there the same software runs for days without problem. So I guess it's related to the underlying libusb lib which is used by the DRS oscilloscope, on which I have no influence. So the only advice I can give is to take shorter series of data. Anyhow the board is not considered a full DAQ system, just an "evaluation board" which means one can try the DRS4 chip and play with it. For serious business one should build own electronics with the chip. Anyhow we are currently developping an Ethernet board which allows much faster acquisition rates, so USB will be obsolete some day. Nevertheless I will try to reproduce your problem and see if I can do anything. At what trigger rate does it show up most prominently?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

Yes I use Windows 7, If the DRS Oscilloscope program stays on for a couple of hours without saving the data, the problem will occur. It seems it happens more often when there is data writing and when the rate of events is slow, about 100 events per second, at high rates it almost doesn't happen. Can it be temperature related?

Daniel

| Stefan Ritt wrote: |

|

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

|

|

|

Hi I have also positron annihilation system based on DRS4v4 cards. Its running several weeks, sometimes months, without freezing in windows7 64bit system (Pentium Core Quad 2Ghz, 4GRam). Problem was when widows was trying to install updates and restarted PC. In beginning I had some problem with memory leak in my application, but it was simple seen in task manager that application memory was rising and was need to find memory leak in application code. Now I remember card was sometimes freezing when room air conditioning with 2kW was starting and high electricity pulses were reason of USB problems, it helped to put air conditioner and PC in different power line input. Hope it help to solve zour problems.

Martin |

Wed Apr 6 09:46:10 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run Wed Apr 6 09:46:10 2016, Daniel Dribin, DRS Oscilloscope freezing after a long run

|

| Martin Petriska wrote: |

|

| Stefan Ritt wrote: |

|

I tried this night to run the board at a 10 Hz rate with an external pulser, without writing, and it did not freeze after ~14 hours of running on Mac OSX. This night I will try again with writing.

Stefan

| Stefan Ritt wrote: |

|

Then it seems that there is some USB communication problem. I heard this also from other people, that the USB data transfer under Windows has sometimes problems. I develop and run the board under Mac OSX, and there the same software runs for days without problem. So I guess it's related to the underlying libusb lib which is used by the DRS oscilloscope, on which I have no influence. So the only advice I can give is to take shorter series of data. Anyhow the board is not considered a full DAQ system, just an "evaluation board" which means one can try the DRS4 chip and play with it. For serious business one should build own electronics with the chip. Anyhow we are currently developping an Ethernet board which allows much faster acquisition rates, so USB will be obsolete some day. Nevertheless I will try to reproduce your problem and see if I can do anything. At what trigger rate does it show up most prominently?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

Yes I use Windows 7, If the DRS Oscilloscope program stays on for a couple of hours without saving the data, the problem will occur. It seems it happens more often when there is data writing and when the rate of events is slow, about 100 events per second, at high rates it almost doesn't happen. Can it be temperature related?

Daniel

| Stefan Ritt wrote: |

|

Dear Daniel,

sorry my late reply, I'm pretty busy these days. The behavior you report has not been seen before, but I guess no one tried to take such long runs of data yet. Can you confirm that the problem also occurs without writing data to disk, or is it disk-related? I guess you use it under Windows 7, right?

Stefan

| Daniel Dribin wrote: |

|

Dear Stefan Ritt,

I am using a DRS4 v5 to do timing measurements of Positron lifetime. I use the DRS Oscilloscope with triggering on 2 channels when I have a coincidence. Attached is a picture with all the setting that I use. When I use the DRS4 for a long measurements of 5 million events for a couple of hours, the DRS Oscilloscope stops showing any signal .After the first restart of the program I get a strange signal which is at the bottom of the scope range of voltage picture below(in the picture I changed the vertical positions of the channels for better viewing). Only after a couple of DRS Oscilloscope restarts and USB reconnections do I get the results again.

I currently am using another DRS4 v5 and the same situation occurs again although with lower frequency.

What can I do to solve this problem?

thank you very much,

Daniel

|

|

|

|

|

Hi I have also positron annihilation system based on DRS4v4 cards. Its running several weeks, sometimes months, without freezing in windows7 64bit system (Pentium Core Quad 2Ghz, 4GRam). Problem was when widows was trying to install updates and restarted PC. In beginning I had some problem with memory leak in my application, but it was simple seen in task manager that application memory was rising and was need to find memory leak in application code. Now I remember card was sometimes freezing when room air conditioning with 2kW was starting and high electricity pulses were reason of USB problems, it helped to put air conditioner and PC in different power line input. Hope it help to solve zour problems.

Martin

|

I too have air conditioning in the room, not sure to which power line it is connected, but I'll try to check this aswell.

Thank you very much. |

Thu Mar 31 19:30:26 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal Thu Mar 31 19:30:26 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz |

Thu Mar 31 19:35:06 2016, Stefan Ritt, Trigger on the And of a positive and negative signal Thu Mar 31 19:35:06 2016, Stefan Ritt, Trigger on the And of a positive and negative signal

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

Thu Mar 31 19:44:38 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal Thu Mar 31 19:44:38 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

Thu Mar 31 20:34:25 2016, Stefan Ritt, Trigger on the And of a positive and negative signal Thu Mar 31 20:34:25 2016, Stefan Ritt, Trigger on the And of a positive and negative signal

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

Thu Mar 31 20:38:05 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal Thu Mar 31 20:38:05 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

Thu Mar 31 20:48:00 2016, Chris Thompson, Trigger on the And of a positive and negative signal Thu Mar 31 20:48:00 2016, Chris Thompson, Trigger on the And of a positive and negative signal

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

Fri Apr 1 01:30:40 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal Fri Apr 1 01:30:40 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

Fri Apr 1 22:09:07 2016, Chris Thompson, Trigger on the And of a positive and negative signal Fri Apr 1 22:09:07 2016, Chris Thompson, Trigger on the And of a positive and negative signal

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

Sat Apr 2 17:22:34 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal Sat Apr 2 17:22:34 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

Sun Apr 3 22:10:19 2016, Chris Thompson, Trigger on the And of a positive and negative signal Sun Apr 3 22:10:19 2016, Chris Thompson, Trigger on the And of a positive and negative signal

|

No there are no other components. I put a photo of the inverter with its cables SMA and one end, BNC at the other. You can see it is very small. I glued the inverter to a piece of thin plywood, and fixed the cables to it before attempting to solder them to the pads on the ferite bead support

| Abaz Kryemadhi wrote: |

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

Sun Apr 3 22:34:28 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal Sun Apr 3 22:34:28 2016, Abaz Kryemadhi, Trigger on the And of a positive and negative signal

|

Thanks, great!

| Chris Thompson wrote: |

|

No there are no other components. I put a photo of the inverter with its cables SMA and one end, BNC at the other. You can see it is very small. I glued the inverter to a piece of thin plywood, and fixed the cables to it before attempting to solder them to the pads on the ferite bead support

| Abaz Kryemadhi wrote: |

|

Thanks again, this is very useful, just another question did you put any other passive elements in the circuit for inverting the signal or just simply swaped the transformer connections?

| Chris Thompson wrote: |

|

The coilcraft part number is: JA4220-ALB. Iordered two of them and they were sent as free samples. You might want to buy some slightly bigger ones. I found them so small it was very hard to solder the coax cable to the connectors. Since I got them, I managed to damage one as they are quite fragile! In the confirmation email I got there was some contact info which may be useful for you: "For help, contact Victoria Berner at 847-516-5551 vberner@coilcraft.com " BTW every time I use this forum I'm told that my password is not valid. Each time I reset it according to the "Lost pasword preceedure. Then I can log on again. Its quite annoying.

| Abaz Kryemadhi wrote: |

|

Hi Chris,

I am looking at Sensl SiPMs as well, can you send the part number from Coilcraft?

Thanks!

Abaz

| Chris Thompson wrote: |

|

I needed a fast pulse inverter in order to feed signals from the recent SensL SiPMs into a conventional CFD which only accepted negative signals. I got a very small ferite torridal transformer from Coilcraft and wired up to invert signals then inserted into in 50 ohm coax cable and it works fine. These things cost only a few cents each!

| Abaz Kryemadhi wrote: |

|

Thanks, that looks just fine.

| Stefan Ritt wrote: |

|

Here is one (SI 100): https://www.picoquant.com/products/category/accessories/adapters-splitters-cables-various-accessories-for-photon-counting-setups

| Abaz Kryemadhi wrote: |

|

Ok, thanks! do you know an easy in-line inverter like mini-circuit or digikey? Can also redesign the detector I gues to produce positive signals, just it might be easier if there was a simple inverter if you are aware of? thanks Abaz

| Stefan Ritt wrote: |

|

No. You have to use an inverter for one of your signals.

Stefan

| Abaz Kryemadhi wrote: |

|

I would like to be able to trigger in this fashon: channel 0 > 0.1 and. channel 1< -0.1, because I have a positive and a negative signal. Can DRS4 (5) Eval board do this kind of trigger?

Thanks!

Abaz

|

|

|

|

|

|

|

|

|

|

|

Sat Apr 2 11:21:10 2016, Felix Bachmair, Question about timimng calibration Sat Apr 2 11:21:10 2016, Felix Bachmair, Question about timimng calibration

|

Hi,

I am trying to understand some details about the timing calibration.

We wrote our own code but we more or less use the ideas of the Oscilloscope class.

In the binary file writing of in the function Osci.cpp::SaveWaveforms() (line 924ff)

the following code is executed:

if (m_waveDepth == 2048) {

t = (tcal[j]+tcal[j+1])/2;

j++;

} else

t = tcal[j];

I do not understand the averaging of the to adjacent calibration constants. Could you explain this? Do one have two measurements?

Cheers

Felix

|

Sat Apr 2 11:41:07 2016, Stefan Ritt, Question about timimng calibration Sat Apr 2 11:41:07 2016, Stefan Ritt, Question about timimng calibration

|

The evaluation board normally has 1024 bins per channel. We offer an option with 2048 bins using channel cascading, to capture longer waveform windows. The binary data format is however defined as having 1024 bins. Therefore, for the 2048 bin boards, the software averages over two adjacent cells and saves effectively 1024 bins. The noise of each bin improves this way by sqrt(2). The time however is not very well defined, since you average the voltage of two bins. Therefore, I simple also average over the time of the two bins. Maybe this is not the best way, so feel free to change this.

Stefan

| Felix Bachmair wrote: |

|

Hi,

I am trying to understand some details about the timing calibration.

We wrote our own code but we more or less use the ideas of the Oscilloscope class.

In the binary file writing of in the function Osci.cpp::SaveWaveforms() (line 924ff)

the following code is executed:

if (m_waveDepth == 2048) {

t = (tcal[j]+tcal[j+1])/2;

j++;

} else

t = tcal[j];

I do not understand the averaging of the to adjacent calibration constants. Could you explain this? Do one have two measurements?

Cheers

Felix

|

|

Fri Mar 11 19:50:18 2016, Dominik Neise, Fri Mar 11 19:50:18 2016, Dominik Neise,

|

Hello Stefan,

I just stumbled again over a phrase in the DRS4 datasheet I never really understood, but didn't find the time to ask.

On page 8 it says: "An internal circuit ensures that the write signal is always 16 cells wide."

So when I look at a single channel, do I understand correctly, that at any given time during sampling, always 16 cells are open, i.e. 16 cells are connected to the analog inputs? So when the domino frequency is e.g. 5GHz then each cell sees the analog input not for 200ps but for 3.2ns correct? |

Tue Mar 22 12:54:41 2016, Stefan Ritt, Tue Mar 22 12:54:41 2016, Stefan Ritt,

|

Yes this is correct. But it is a sample-and-hold circuit. So the sampling cell follows the input for 3.2 ns, then samples and holds the current value at the end of the period.

| Dominik Neise wrote: |

|

Hello Stefan,

I just stumbled again over a phrase in the DRS4 datasheet I never really understood, but didn't find the time to ask.

On page 8 it says: "An internal circuit ensures that the write signal is always 16 cells wide."

So when I look at a single channel, do I understand correctly, that at any given time during sampling, always 16 cells are open, i.e. 16 cells are connected to the analog inputs? So when the domino frequency is e.g. 5GHz then each cell sees the analog input not for 200ps but for 3.2ns correct?

|

|

Mon Feb 29 12:58:17 2016, Dmitry Philippov, baseline shift Mon Feb 29 12:58:17 2016, Dmitry Philippov, baseline shift

|

Hello! My name is Dmitry. I am from SiPM Lab is NRNU MEPhI (Russia, Moscow). We bought DRS4 evaluation board V5 with firmware 21305. We use 5.0.4 build 21911 2015-11-23 software version (and before that we used 5.0.3 build 21508, 2014-10-15) with Windows 7 32bit.

We observe some strange behaviour. When we save waveforms (in xml or binary data) we see that some of them have the baseline shifted of about -5 mV.

The first picture (pic1) is 1000 waveforms which were glued in one. It is clearly see that baseline quite often has the shift.

The same effect can be seen without saving (writting): rarely when we use normal or auto trigger mode (pic3), and always in single trigger mode (pic2).

The images are attached.

Do you have any idea how it can be fixed?

Thanks, Dmitry.

|

Mon Feb 29 13:09:29 2016, Stefan Ritt, baseline shift Mon Feb 29 13:09:29 2016, Stefan Ritt, baseline shift

|

The baseline shift comes from some instable power supply inside the evaluation board which cannot be controlled to the mV level. In a real measurement, you usually get an additional baseline shift due to some environmental electromagnetic interferences, such as a 50 Hz signal. People fix this shifting baseline by always aquiring a small portion (10-20 samples) of the baseline before any signal from a particle detector. The signal is then corrected event-by-event by subtracting the baseline from each waveform. By doing that, you fix not only the 50 Hz noise, but also the shifting baseline you mention.

Stefan

| Dmitry Philippov wrote: |

|

Hello! My name is Dmitry. I am from SiPM Lab is NRNU MEPhI (Russia, Moscow). We bought DRS4 evaluation board V5 with firmware 21305. We use 5.0.4 build 21911 2015-11-23 software version (and before that we used 5.0.3 build 21508, 2014-10-15) with Windows 7 32bit.

We observe some strange behaviour. When we save waveforms (in xml or binary data) we see that some of them have the baseline shifted of about -5 mV.

The first picture (pic1) is 1000 waveforms which were glued in one. It is clearly see that baseline quite often has the shift.

The same effect can be seen without saving (writting): rarely when we use normal or auto trigger mode (pic3), and always in single trigger mode (pic2).

The images are attached.

Do you have any idea how it can be fixed?

Thanks, Dmitry.

|

|

Thu Nov 26 18:59:27 2015, Robert Adams, Saving histogram data Thu Nov 26 18:59:27 2015, Robert Adams, Saving histogram data

|

I would really love to be able to save histogram data, though I have not been able to do this. I could take a screenshot and extract the data from an image, but would prefer to avoid this if there is a simpler way... possibly I have overlooked something obvious? Thanks very much for any advice or tips. |

Tue Feb 16 11:21:43 2016, Stefan Ritt, Saving histogram data Tue Feb 16 11:21:43 2016, Stefan Ritt, Saving histogram data

|

There is no histogram save functoinality in ther DRSOscilloscope program - on purpose. The board and the software are meant to evaluate the board, not to replace a full DAQ system. If we want to save histograms, you maybe also want to set the range, make cuts, do fits etc. So it would take lots of resources to add all that. Therefore we recommend to use the stand-alone C program drs_exam.cpp to read the board, the you can either do whatever you want in the C program, including saving of histograms. Alternatively, you can use ROOT to analyze binary stored DRS data and do whatever histogram manipulation you want there.

Stefan

| Robert Adams wrote: |

|

I would really love to be able to save histogram data, though I have not been able to do this. I could take a screenshot and extract the data from an image, but would prefer to avoid this if there is a simpler way... possibly I have overlooked something obvious? Thanks very much for any advice or tips.

|

|

Tue Feb 16 11:55:54 2016, Martin Petriska, Saving histogram data Tue Feb 16 11:55:54 2016, Martin Petriska, Saving histogram data

|

| Robert Adams wrote: |

|

I would really love to be able to save histogram data, though I have not been able to do this. I could take a screenshot and extract the data from an image, but would prefer to avoid this if there is a simpler way... possibly I have overlooked something obvious? Thanks very much for any advice or tips.

|

You can use qtpals, there is posibility to save histograms (energy, time diference), only set trigger on channel which you use. https://sourceforge.net/projects/qtpals/files/?source=navbar |

Thu Jan 14 21:49:37 2016, Chris Thompson, Triggering of DRS4 in the fastest sampling mode Thu Jan 14 21:49:37 2016, Chris Thompson, Triggering of DRS4 in the fastest sampling mode

|

I am attempting to use the DRS4 to measure the timing resolution of a pair of SensL silicon photomultipliers (SiPM). In order to do this I need to trigger the DRS4 only when there is a coincidence between the two input signals, and hopefully make histograms of the relative detection times of each detector.

There are two completely separate issues. (1) I think this may just be a labelling error. In the first image (OR_mode_selected) one can clearly see two pulses which are very similar. In this mode, both signals are present, and are always present. I think this should be the "AND", not "OR" of the two signals. Contrast this with the second image where I have selected "AND_mode". Clearly only one signal is present, and either signal trigges an event, so this should be "OR", not "AND"

The second issue is, for me, much more serious. I want to sample the leading edge of this event in order to determine its "time". The little "T" at the top of each image is, I believe the "trigger point" in the first two images. However, this is well after the part of the signal I am interested in. The first two images were at 2 GigaSamples/sec. The third is at 5 GigaSamples/sec. Clearly the event I am interested in processing is over by then. At the lower sampling rate, I can see well before the "T", but at the higher one I can only see after the "T". I had built an external "coincidence circuit" and the "external trigger mode" hoping to to circumvent this issue by using very long cables to delay the signals inut to the DRS4, But even then I have not been successful in getting the to work.

I am using version 5.0.3 on a PC as the version released after that did not work.

I hope some can help!

Chris Thompson |

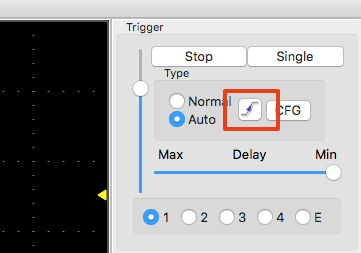

Fri Jan 15 08:09:00 2016, Stefan Ritt, Triggering of DRS4 in the fastest sampling mode Fri Jan 15 08:09:00 2016, Stefan Ritt, Triggering of DRS4 in the fastest sampling mode

|

Hi Chris,

if you ever used an oscilloscope, you might be familar with the button controlling the riger in respect to "risign edge" vs. "falling edge". I copied the same for the DRS software. So just click on that button:

and you will get what you want. Also the AND/OR gets reversed this way. If you select rising edge (default), the AND will be made if both signals are ABOVE the threshold, that's why it does not work for you. If you select falling edge, the AND will be made if both signals are BELOW the threshold. For negative pulses you need falling edge.

Stefan

| Chris Thompson wrote: |

|

I am attempting to use the DRS4 to measure the timing resolution of a pair of SensL silicon photomultipliers (SiPM). In order to do this I need to trigger the DRS4 only when there is a coincidence between the two input signals, and hopefully make histograms of the relative detection times of each detector.

There are two completely separate issues. (1) I think this may just be a labelling error. In the first image (OR_mode_selected) one can clearly see two pulses which are very similar. In this mode, both signals are present, and are always present. I think this should be the "AND", not "OR" of the two signals. Contrast this with the second image where I have selected "AND_mode". Clearly only one signal is present, and either signal trigges an event, so this should be "OR", not "AND"

The second issue is, for me, much more serious. I want to sample the leading edge of this event in order to determine its "time". The little "T" at the top of each image is, I believe the "trigger point" in the first two images. However, this is well after the part of the signal I am interested in. The first two images were at 2 GigaSamples/sec. The third is at 5 GigaSamples/sec. Clearly the event I am interested in processing is over by then. At the lower sampling rate, I can see well before the "T", but at the higher one I can only see after the "T". I had built an external "coincidence circuit" and the "external trigger mode" hoping to to circumvent this issue by using very long cables to delay the signals inut to the DRS4, But even then I have not been successful in getting the to work.

I am using version 5.0.3 on a PC as the version released after that did not work.

I hope some can help!

Chris Thompson

|

|

Wed Dec 23 15:38:14 2015, mony orbach, Dtap stops toggling after 40msec Wed Dec 23 15:38:14 2015, mony orbach, Dtap stops toggling after 40msec

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony |

Wed Dec 23 15:48:42 2015, Stefan Ritt, Dtap stops toggling after 40msec Wed Dec 23 15:48:42 2015, Stefan Ritt, Dtap stops toggling after 40msec

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

Thu Dec 24 10:51:31 2015, mony orbach, Dtap stops toggling after 40msec Thu Dec 24 10:51:31 2015, mony orbach, Dtap stops toggling after 40msec

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

Thu Dec 24 12:45:41 2015, Stefan Ritt, Dtap stops toggling after 40msec Thu Dec 24 12:45:41 2015, Stefan Ritt, Dtap stops toggling after 40msec

|

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

Sun Dec 27 15:41:32 2015, mony orbach, Dtap stops toggling after 40msec Sun Dec 27 15:41:32 2015, mony orbach, Dtap stops toggling after 40msec

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

| Stefan Ritt wrote: |

|

I want to see the trace on the scope for the DTAP, the REFCLK, the DENABLE and the DWRITE.

Probably (but it's just a guess), you have a problem with the soldering of the DRS chip, maybe to the PLL loop filter. Or you chose the wrong capacitor/resistor combination for the loop filter. There are ~10 other groupsl who did the same and it works for all of them, so there must be a problem on your side.

Stefan

| mony orbach wrote: |

|

my refclk is 1.25Mhz

what are the inputs and voltage you need to see?

Avdd and Dvdd are 2.5v

Denable is "1" Dwrite "0"

currently i am doing an external reset cycle, after that i am doing the configuration cycle.

should i relay on the internal reset?

the Dtap is toggling for 33.8msec and then just stops.

Thanks, Mony

| Stefan Ritt wrote: |

|

No idea what you do wrong. I need to see oscilloscope traces for all your inputs and voltages. What is your REFCLK input?

| mony orbach wrote: |

|

Hi

the drs4 start to generate Dtap signal after reset and standard configuration.

while in reset Denable and Dwrite are low

after reset we put Denable in high

the Dtap starts to toggle, and the plllck stabilizes on about 1V.

After 40Msec the Dtap stops to toggle and the plllck go to 2.5V

Why do the Domino stop working?

Thanks, Mony

|

|

|

|

|

Mon Dec 28 11:05:15 2015, Stefan Ritt, Dtap stops toggling after 40msec Mon Dec 28 11:05:15 2015, Stefan Ritt, Dtap stops toggling after 40msec

|

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|

Mon Dec 28 11:21:54 2015, mony orbach, Dtap stops toggling after 40msec Mon Dec 28 11:21:54 2015, mony orbach, Dtap stops toggling after 40msec

|

Hi Stefan

Thanks for your input.

We are in the process of assemble another PCB board.

so soon we can compere between two boards.

As for the PLLEN bit, we set it.

We checked several times the soldering of the DRS4 using a microscope.

Everything looks ok.

In what method do you recommend to solder the DRS4?

Thanks for the invitation to meet.

120Km is not so far J

mony

| Stefan Ritt wrote: |

|

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|

|

Wed Dec 30 16:25:35 2015, mony orbach, Dtap stops toggling after 40msec Wed Dec 30 16:25:35 2015, mony orbach, Dtap stops toggling after 40msec

|

Hi

We have resolve the problem, the Dtap is now working correctly.

There were two problems:

- After configuration we put the all address bits to one (standby mode)

We are now setting the address bits to all zero. Failure

to do so result in Dtap stop toggling after several hundred milliseconds.

- The DMODE bit in contradiction to the data sheet should be set to 0

And not to 1.

Is this a known bug in the chip?

Only bay setting DMODE to zero we got the Dtap to work correctly.

The PLL locks after 1 milisec.

If we set it to one we get Dtap that stop toggling after several hundred milliseconds.

We have test it on two boards, they both worked in the same.

Never did we get a One shot Dtap.

Did you published a errata page to the drs4?

Thanks, Mony

| mony orbach wrote: |

|

Hi Stefan

Thanks for your input.

We are in the process of assemble another PCB board.

so soon we can compere between two boards.

As for the PLLEN bit, we set it.

We checked several times the soldering of the DRS4 using a microscope.

Everything looks ok.

In what method do you recommend to solder the DRS4?

Thanks for the invitation to meet.

120Km is not so far J

mony

| Stefan Ritt wrote: |

|

Thanks for posting the plots. It really looks like the PLL is not working. I see two possible reasons: 1) The PLLEN bit in the configuration register is not set and 2) The REFCLK signal does not reach the chip. We had cases whrere people had a hard time to solder the DRS4 correctly due to the small pins. So if the REFCLK+ and REFCLK- signals have a poor connection, then the PLL of course won't work. Putting some more tin at the pins manually usually helps. Or remove the chip completely and try with another chip. In theory there is the possibility that the internal bond wire of the REFCLK signal has a bad connection, but we tested all chips we send out so we should have seen that. But trying with another chip cannot hurt in general. Next month I'm coming to the Weizman Institute for the ISOTDAQ shool. If you want we can meet there if you don't mind the 120 km drive from Haifa.

Stefan

| mony orbach wrote: |

|

Hi

We have some measures to show (attached)

- Dtap and Denable

- Dtap+Denable in zoom

- Dtap + Refck+

- Dtap + Dspeed

From the screen shots it can be seen that refck+ is not synchronized with Dtap (PLL not working correctly)

And Dspeed is going done to zero after some time.

In our system Dspeed is shorted to pllout.

So it looks like pllout do not pump the RC filter capacitors.

We tested various value of R and C's.

Also we checked that pllout is sorted to Dspeed.

Thanks, mony

|

|

|

|

Wed Dec 30 17:00:00 2015, Stefan Ritt, Dtap stops toggling after 40msec Wed Dec 30 17:00:00 2015, Stefan Ritt, Dtap stops toggling after 40msec

|

While I can understand 1., I'm puzzeled by 2.