Wed Jun 1 09:57:43 2011, Martin Petriska, Removing spikes Wed Jun 1 09:57:43 2011, Martin Petriska, Removing spikes

|

I have DSR4 eval board. Found that there are spikes in channels. Procedure Osc::RemoveSpikes to remove them looks litlle dificult. There is simple way, if you doesnt need to measure all 4 channels.Spikes are in all channels, and it looks like they are same in time and value between channels. To remove them, if you are not using one channel, substract that unused channel with spikes from used channel and your data will be without spikes. If you need all 4 inputs, then may be channel 9 could be substracted. |

Thu Jun 2 21:01:29 2011, Stefan Ritt, Removing spikes Thu Jun 2 21:01:29 2011, Stefan Ritt, Removing spikes

|

| Martin Petriska wrote: |

|

I have DSR4 eval board. Found that there are spikes in channels. Procedure Osc::RemoveSpikes to remove them looks litlle dificult. There is simple way, if you doesnt need to measure all 4 channels.Spikes are in all channels, and it looks like they are same in time and value between channels. To remove them, if you are not using one channel, substract that unused channel with spikes from used channel and your data will be without spikes. If you need all 4 inputs, then may be channel 9 could be substracted.

|

Indeed that's what I had before. If you don't need the 9th channels, you can use it to identify the spikes. But we have applications where we need all 9 channels. That's why I made Osc::RemoveSpikes a bit more complicated, so it will still work when all 9 channels are used. This new version is release 3.1.0. If you just blindly subtract the 9th channel, your noise could increase by a sqrt(2). |

Fri Feb 25 10:13:51 2011, Stefan Ritt, Announcement digital pulse processing workshop Fri Feb 25 10:13:51 2011, Stefan Ritt, Announcement digital pulse processing workshop

|

Dear colleague,

if you live not so far from Zurich, you might be interested in this workshop:

http://www.xtronix.ch/hep/psi_workshop.htm

This is a combined PSI-CAEN presentation of digitizer hardware including the new V1742 board based on the DRS4 chip. The workshop will also show how digital pulse processing can be used to effectively extract time and energy from detector signals, and thus replace more and more traditional analog electronics. Please register at the above site if you are interested.

Best regards,

Stefan Ritt |

Sat Feb 19 17:25:29 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards Sat Feb 19 17:25:29 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya |

Sat Feb 19 22:46:35 2011, Stefan Ritt, how to synchronize Sampling frequency of two evaluation boards Sat Feb 19 22:46:35 2011, Stefan Ritt, how to synchronize Sampling frequency of two evaluation boards

|

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board. |

Mon Feb 21 08:10:31 2011, Stefan Ritt, how to synchronize Sampling frequency of two evaluation boards Mon Feb 21 08:10:31 2011, Stefan Ritt, how to synchronize Sampling frequency of two evaluation boards

|

| Stefan Ritt wrote: |

|

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board.

|

Well, one thing you can do is to generate an external trigger and send it to the external trigger input of both cards. Then you can determine the time in respect to the trigger point in both boards. But since the trigger cell jitters by 2-3 cells in each chip, the accuracy is limited to about 1-2 ns when running at 2 GS/s. |

Mon Feb 21 12:42:33 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards Mon Feb 21 12:42:33 2011, S S Upadhya, how to synchronize Sampling frequency of two evaluation boards

|

| Stefan Ritt wrote: |

|

| Stefan Ritt wrote: |

|

| S S Upadhya wrote: |

|

Dear sir,

We have two evaluation boards of DRS4. We would like to use 8 inputs to be recorded on a trigger and we would like to find the relative time difference of inputs. So is it possible to synchronize the sampling frequency of the two evaluation boards.

with best regards

S S Upadhya

|

No, not in this version. We plan a future version of the evaluation board with clock synchronization, but that board will not be ready before 2-3 months. Anyhow the board is more meant as an evaluation board, to test the chip and develop own electronics, and not to build a complete DAQ system. Note that CAEN distributes now a VME board containing the four DRS4 chips and 32 channels on a board.

|

Well, one thing you can do is to generate an external trigger and send it to the external trigger input of both cards. Then you can determine the time in respect to the trigger point in both boards. But since the trigger cell jitters by 2-3 cells in each chip, the accuracy is limited to about 1-2 ns when running at 2 GS/s.

|

Dear Stefan,

Thanks for the second suggestion. I wanted to do feasibility study of DRS4 application to our requirement in the experiment

Thank you again sir,

Upadhya |

Tue May 18 09:24:02 2010, Stefan Ritt, Reference design for DRS4 active input buffer Tue May 18 09:24:02 2010, Stefan Ritt, Reference design for DRS4 active input buffer

|

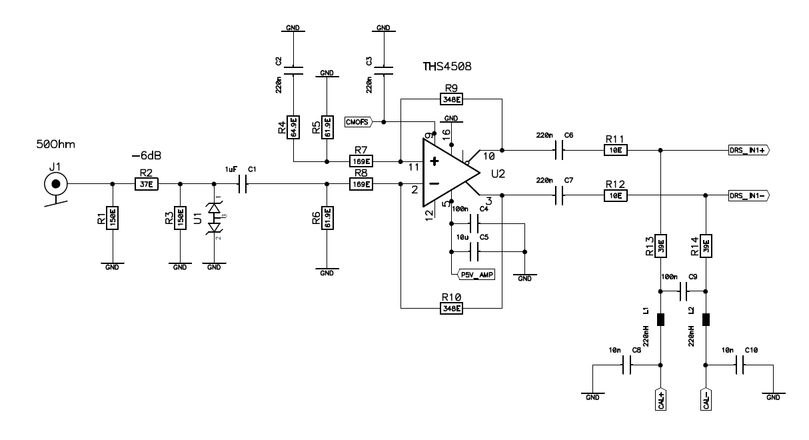

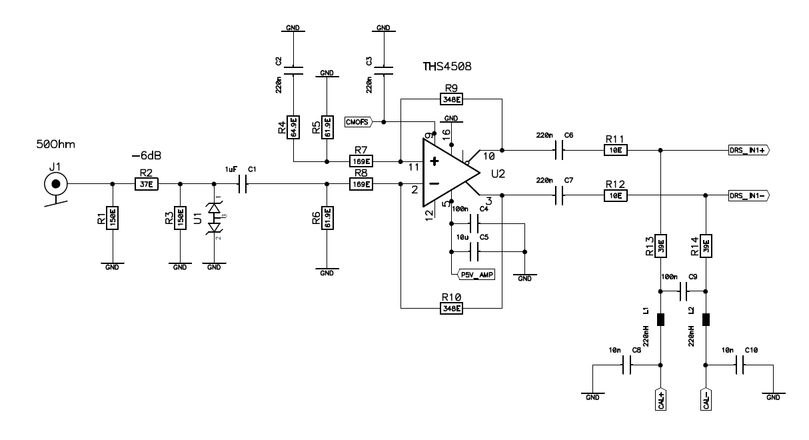

The design of high frequency differential input stages with the DRS4 is a challenge, since the chip draws quite some current at the input (up to 1 mA at 5 GSPS), which must be sourced by the input buffer. A simple transformer as used in the DRS4 Evaluation Board 2.0 limits the bandwidth to 220 MHz. In meantime two active input stages have been worked out and successfully been tested, both utilizing the THS4508 differential amplifier. The first design is AC-coupled and uses less power, the second design is DC-coupled and uses more power with the benefit of delivering a higher bandwidth.

Both designs use a clamping diode at the input as a protection against high voltage spikes at the input. We used a RCLAMP0502B diode from SEMTECH, but any fast voltage suppressor diode will do the job.

The CMOFS input to the THS4508 set the common mode of the differential amplifier. In the AC version the level is set to mid-rail (2.5V), in the DC version it's set to 1.8V to match the input range of the DRS4.

The CAL+ and CAL- signals are used to bias the inputs to a well-defined DC level and can also be used to calibrate the chip. For bipolar inputs, they are both set to 0.8V. A positive 0.5V input pulse then drives DRS_IN+ to (0.8+0.25)V = 1.05V and DRS_IN- to (0.8-0.25)V = 0.55V. A negative 0.5V pulse then drives then DRS_IN+ to 0.55V and DRS_IN- to 1.05V. With ROFS=1.6V, the full dynamic range of the DRS4 is then used. Note that the THS4508 has a gain of 2, and the input has a -6dB voltage divider to compensate for that. To use other input ranges, such as -1V...0V, the CAL+ and CAL- signals can be adjusted accordingly. Note that the inputs of the DRS4 must always be between 0.1V and 1.5V.

AC-coupled version

(click to enlarge)

Power supply: +5 V 40 mA

Bandwidth (-3dB): 600 MHz

CMOFS: 2.5 V

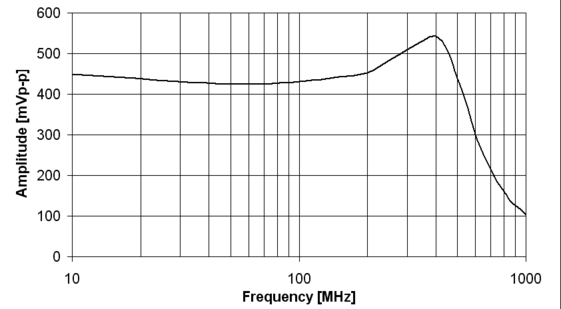

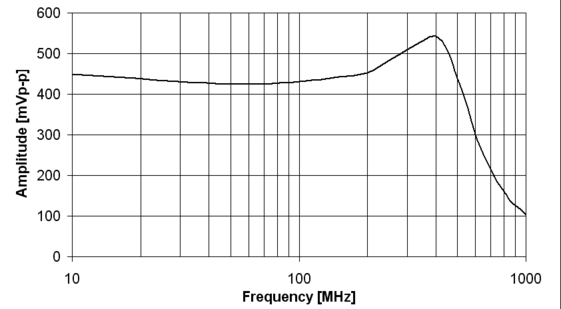

Transfer function:

(click to enlarge)

The transfer function was measured by applying a fixed amplitude sine wave to the input, and measuring the peak-to-peak value of the read out waveform with the DRSOsc application.

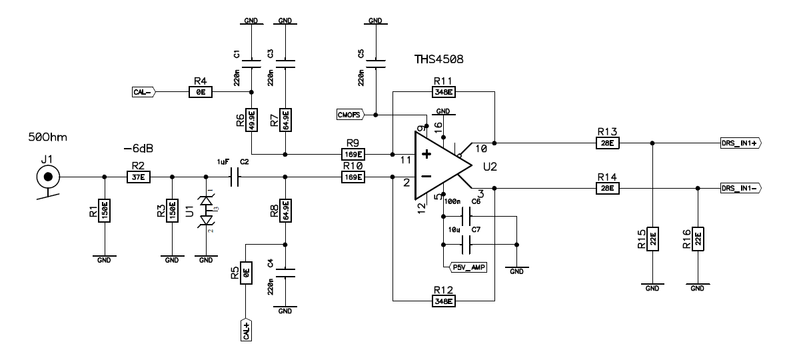

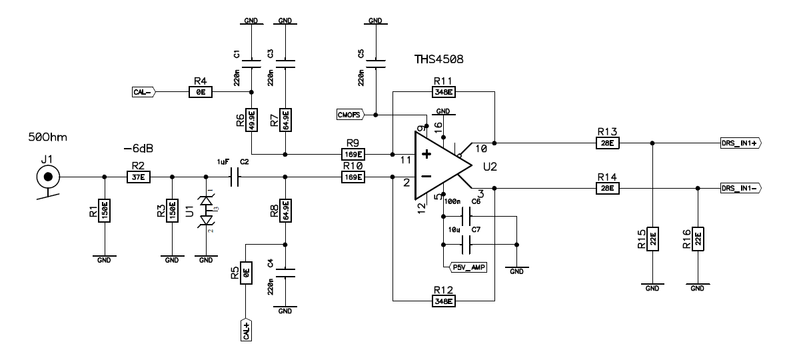

DC-coupled Version

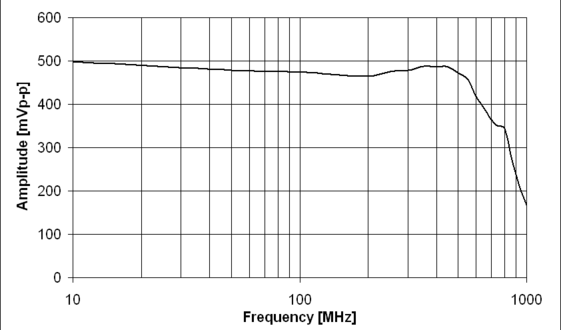

The DC-coupled version has a slightly higher power consumption since there is a constant current flowing through the output into the DRS4 chip. On the other hand, the bandwidth is a bit higher and the peaking around 400 MHz is a bit smaller. The input is still AC-coupled, so both positive and negative pulses can be accepted.

(click to enlarge)

Power supply: +5 V 115 mA

Bandwidth (-3dB): 800 MHz

CMOFS: 1.8 V

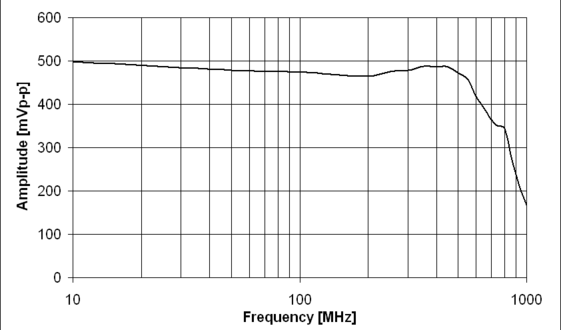

Transfer function:

(click to enlarge)

Achievable performance

With the active input stage, much faster rise- and fall times can be achieved. Following picture shows a signal from a external clock having a fall time of about 300 ps being recorded with the AC-coupled version of the active input stage. The fall time of the recorded signal is about 800 ps, which is about the minimum which can be achieved with the AC-coupled version. The DC-coupled version achieves about 700ps.

|

Tue Oct 12 03:53:37 2010, Jinhong Wang, Reference design for DRS4 active input buffer Tue Oct 12 03:53:37 2010, Jinhong Wang, Reference design for DRS4 active input buffer

|

| Stefan Ritt wrote: |

|

The design of high frequency differential input stages with the DRS4 is a challenge, since the chip draws quite some current at the input (up to 1 mA at 5 GSPS), which must be sourced by the input buffer. A simple transformer as used in the DRS4 Evaluation Board 2.0 limits the bandwidth to 220 MHz. In meantime two active input stages have been worked out and successfully been tested, both utilizing the THS4508 differential amplifier. The first design is AC-coupled and uses less power, the second design is DC-coupled and uses more power with the benefit of delivering a higher bandwidth.

Both designs use a clamping diode at the input as a protection against high voltage spikes at the input. We used a RCLAMP0502B diode from SEMTECH, but any fast voltage suppressor diode will do the job.

The CMOFS input to the THS4508 set the common mode of the differential amplifier. In the AC version the level is set to mid-rail (2.5V), in the DC version it's set to 1.8V to match the input range of the DRS4.

The CAL+ and CAL- signals are used to bias the inputs to a well-defined DC level and can also be used to calibrate the chip. For bipolar inputs, they are both set to 0.8V. A positive 0.5V input pulse then drives DRS_IN+ to (0.8+0.25)V = 1.05V and DRS_IN- to (0.8-0.25)V = 0.55V. A negative 0.5V pulse then drives then DRS_IN+ to 0.55V and DRS_IN- to 1.05V. With ROFS=1.6V, the full dynamic range of the DRS4 is then used. Note that the THS4508 has a gain of 2, and the input has a -6dB voltage divider to compensate for that. To use other input ranges, such as -1V...0V, the CAL+ and CAL- signals can be adjusted accordingly. Note that the inputs of the DRS4 must always be between 0.1V and 1.5V.

AC-coupled version

(click to enlarge)

Power supply: +5 V 40 mA

Bandwidth (-3dB): 600 MHz

CMOFS: 2.5 V

Transfer function:

(click to enlarge)

The transfer function was measured by applying a fixed amplitude sine wave to the input, and measuring the peak-to-peak value of the read out waveform with the DRSOsc application.

DC-coupled Version

The DC-coupled version has a slightly higher power consumption since there is a constant current flowing through the output into the DRS4 chip. On the other hand, the bandwidth is a bit higher and the peaking around 400 MHz is a bit smaller. The input is still AC-coupled, so both positive and negative pulses can be accepted.

(click to enlarge)

Power supply: +5 V 115 mA

Bandwidth (-3dB): 800 MHz

CMOFS: 1.8 V

Transfer function:

(click to enlarge)

Achievable performance

With the active input stage, much faster rise- and fall times can be achieved. Following picture shows a signal from a external clock having a fall time of about 300 ps being recorded with the AC-coupled version of the active input stage. The fall time of the recorded signal is about 800 ps, which is about the minimum which can be achieved with the AC-coupled version. The DC-coupled version achieves about 700ps.

|

Hi, stefan,

In the DC coupled version of the analog drivers for DRS4 input in Eval. Board V3, you mentioned that CMOFS of THS4508 was set to 1.8V to match the input range of DRS4, however, will this clash with the requirements of DRS4 input voltage between 0.1 V ~1.5V ? The output of THS4508 can easily rise beyond 1.5V for CMOFS=1.8V. I also noticed the resister paris R13/R15, R14/R16 was added among the output of THS4508 and the inputs of DRS4, were these resister pairs were used to attenuate the level of THS4508 output signal (a half ? ) to match the input requirements of DRS4? Maybe I have some misunderstanding about it.

|

Tue Nov 16 16:38:06 2010, Stefan Ritt, Reference design for DRS4 active input buffer Tue Nov 16 16:38:06 2010, Stefan Ritt, Reference design for DRS4 active input buffer

|

| Jinhong Wang wrote: |

|

Hi, stefan,

In the DC coupled version of the analog drivers for DRS4 input in Eval. Board V3, you mentioned that CMOFS of THS4508 was set to 1.8V to match the input range of DRS4, however, will this clash with the requirements of DRS4 input voltage between 0.1 V ~1.5V ? The output of THS4508 can easily rise beyond 1.5V for CMOFS=1.8V. I also noticed the resister paris R13/R15, R14/R16 was added among the output of THS4508 and the inputs of DRS4, were these resister pairs were used to attenuate the level of THS4508 output signal (a half ? ) to match the input requirements of DRS4? Maybe I have some misunderstanding about it.

|

No you are right about that. The THS4508 has a gain of +2, and by using the resistor pairs we do

1) Reduce the gain back to unity

2) Reduce the input DC level from 1.8V to 0.9V to match the input range

3) Terminate the signals at the input of the DRS chip to minimize reflections

I know this is not so obvious from the schematic, so thanks for asking.

- Stefan |

Wed Jul 21 10:46:32 2010, Jinhong Wang, ENOB of DRS Wed Jul 21 10:46:32 2010, Jinhong Wang, ENOB of DRS

|

Hi, Stefan, I see in your ppt "Design and performance of 6 GSPS waveform digitizing chip DRS4" , you define DRS4 ENOB as 1Vpp/0.35mv(RMS) = 11.5bit, where, 1Vpp is the linearity input range, and 0.35mv is the rms voltage after offset correction. What I understand is that 0.35mV is obtained from DC offset Correction, hence 11.5 bit is for DC input, am i right? If true, what about ENOB for AC input in the whole analog bandwidth? thanks~ |

Wed Jul 21 10:58:20 2010, Stefan Ritt, ENOB of DRS Wed Jul 21 10:58:20 2010, Stefan Ritt, ENOB of DRS

|

| Jinhong Wang wrote: |

|

Hi, Stefan, I see in your ppt "Design and performance of 6 GSPS waveform digitizing chip DRS4" , you define DRS4 ENOB as 1Vpp/0.35mv(RMS) = 11.5bit, where, 1Vpp is the linearity input range, and 0.35mv is the rms voltage after offset correction. What I understand is that 0.35mV is obtained from DC offset Correction, hence 11.5 bit is for DC input, am i right? If true, what about ENOB for AC input in the whole analog bandwidth? thanks~

|

The expression ENOB for 1Vpp/0.35mV(RMS) is wrong, but I learned this later. Now I call it SNR. The ENOB is calculated in a more complicated way, see for example http://en.wikipedia.org/wiki/ENOB. If you measure the ENOB without timing correction, it's pretty poor (in the order of 7-8 bits). This is because without timing calibration, a sine input has huge side bands, and the ENOB involves the power of your signal over the power of the side bands. If you do a proper timing calibration, you spectrum gets "sharper", and hence the ENOB increases. But I have to admit that I never measured it carefully, since we are still optimizing the timing calibration. Once we have a perfect timing calibration, I will do it and update the data sheet. |

Mon Jul 12 16:07:37 2010, Stefan Ritt, Announcement evaluation board V3 Mon Jul 12 16:07:37 2010, Stefan Ritt, Announcement evaluation board V3

|

Dear DRS4 users,

a new version of the evaluation board has been designed and is in production now. The main difference is that it uses active input amplifiers, which result in an analog bandwidth of 700 MHz (as compared with the 220 MHz of the previous board) at moderate power consumption, so the board can still be powered by the USB port. New orders will receive boards V3, the old V2 boards are not available any more.

It is mandatory to use the software revision 3.0.0 or later with the new board. This software has also many new features in the oscilloscope application, and together with the new firmware it reduces the noise of the board below 0.5 mV RMS. Although the software can be used with old V2 boards, some limitations might apply due to the old firmware of the boards. People having a Xilinx download cable can flash the firmware contained in the 3.0.0 revision to their V2 board to get all features of the new software.

The evaluation board manual V3 contains the new schematics of the analog inputs using the THS4508 differential amplifier, so people doing their own design can use this schematics as and example.

Best regards,

Stefan Ritt |

Tue Jun 22 10:50:19 2010, Jinhong Wang, Reset of DRS4 Tue Jun 22 10:50:19 2010, Jinhong Wang, Reset of DRS4

|

Hi Stefan,

I found DRS draw a lot of current when applied Reset after power on, and the PLL does not work properly. I believe there was something that I misunderstood. So, what will happen when Reset is applied more than once after power on? . Though the chip worked well without a Reset, i want to try to find out what was wrong, for a better understanding of DRS.

best regards!

Jinhong |

Tue Jun 22 11:02:30 2010, Stefan Ritt, Reset of DRS4 Tue Jun 22 11:02:30 2010, Stefan Ritt, Reset of DRS4

|

| Jinhong Wang wrote: |

|

Hi Stefan,

I found DRS draw a lot of current when applied Reset after power on, and the PLL does not work properly. I believe there was something that I misunderstood. So, what will happen when Reset is applied more than once after power on? . Though the chip worked well without a Reset, i want to try to find out what was wrong, for a better understanding of DRS.

best regards!

Jinhong

|

Have you made sure that DENABLE and DWRITE stays low during the reset? |

Tue Jun 22 11:29:26 2010, Jinhong Wang, Reset of DRS4 Tue Jun 22 11:29:26 2010, Jinhong Wang, Reset of DRS4

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan,

I found DRS draw a lot of current when applied Reset after power on, and the PLL does not work properly. I believe there was something that I misunderstood. So, what will happen when Reset is applied more than once after power on? . Though the chip worked well without a Reset, i want to try to find out what was wrong, for a better understanding of DRS.

best regards!

Jinhong

|

Have you made sure that DENABLE and DWRITE stays low during the reset?

|

Yes, they are stay low until Reset goes high. the process is as following

Step1: Reset ='1', DEnable ='0', DWrite ='0', Reg_addr ="1111", Rsload='0', Srin ='0'

Step2: Reset='0', the others do not change, the low of the pulse is longer than 10 ns.

Step3: Reset='1', the others do not change, wait for some time

Step4: DEnable ='1' to start the domino. |

Tue Jun 22 11:35:18 2010, Stefan Ritt, Reset of DRS4 Tue Jun 22 11:35:18 2010, Stefan Ritt, Reset of DRS4

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan,

I found DRS draw a lot of current when applied Reset after power on, and the PLL does not work properly. I believe there was something that I misunderstood. So, what will happen when Reset is applied more than once after power on? . Though the chip worked well without a Reset, i want to try to find out what was wrong, for a better understanding of DRS.

best regards!

Jinhong

|

Have you made sure that DENABLE and DWRITE stays low during the reset?

|

Yes, they are stay low until Reset goes high. the process is as following

Step1: Reset ='1', DEnable ='0', DWrite ='0', Reg_addr ="1111", Rsload='0', Srin ='0'

Step2: Reset='0', the others do not change, the low of the pulse is longer than 10 ns.

Step3: Reset='1', the others do not change, wait for some time

Step4: DEnable ='1' to start the domino.

|

Ok, then I have no idea. I never tried several reset pulses (actually this is not needed), so I have to reproduce the problem myself and investigate it. Actually in all my designs the reset input is just left open, since the internal initial reset is enough, so I have to modify my design first... |

Tue Jun 22 11:37:42 2010, Jinhong Wang, Reset of DRS4 Tue Jun 22 11:37:42 2010, Jinhong Wang, Reset of DRS4

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan,

I found DRS draw a lot of current when applied Reset after power on, and the PLL does not work properly. I believe there was something that I misunderstood. So, what will happen when Reset is applied more than once after power on? . Though the chip worked well without a Reset, i want to try to find out what was wrong, for a better understanding of DRS.

best regards!

Jinhong

|

Have you made sure that DENABLE and DWRITE stays low during the reset?

|

Yes, they are stay low until Reset goes high. the process is as following

Step1: Reset ='1', DEnable ='0', DWrite ='0', Reg_addr ="1111", Rsload='0', Srin ='0'

Step2: Reset='0', the others do not change, the low of the pulse is longer than 10 ns.

Step3: Reset='1', the others do not change, wait for some time

Step4: DEnable ='1' to start the domino.

|

Ok, then I have no idea. I never tried several reset pulses (actually this is not needed), so I have to reproduce the problem myself and investigate it. Actually in all my designs the reset input is just left open, since the internal initial reset is enough, so I have to modify my design first...

|

Ok ,thank you. |

Thu May 13 19:14:27 2010, Hao Huan, DVDD Problem of DRS 4 Thu May 13 19:14:27 2010, Hao Huan, DVDD Problem of DRS 4

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot! |

Fri May 14 08:40:14 2010, Stefan Ritt, DVDD Problem of DRS 4 Fri May 14 08:40:14 2010, Stefan Ritt, DVDD Problem of DRS 4

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely. |

Tue May 18 01:47:59 2010, Hao Huan, DVDD Problem of DRS 4 Tue May 18 01:47:59 2010, Hao Huan, DVDD Problem of DRS 4

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit? |

Tue May 18 08:23:07 2010, Stefan Ritt, DVDD Problem of DRS 4 Tue May 18 08:23:07 2010, Stefan Ritt, DVDD Problem of DRS 4

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence? |

Wed May 19 02:24:12 2010, Hao Huan, DVDD Problem of DRS 4 Wed May 19 02:24:12 2010, Hao Huan, DVDD Problem of DRS 4

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence?

|

Yes; I used RSRLOAD to trigger readout of all channels in parallel so the asymmetry between channels of the same chip is really a big puzzle. Also during reset DSPEED indeed goes to 2.5V, but after reset the PLL will not try to lock with the external reference clock and lower DSPEED. Instead the Domino circuit just oscillates at the highest frequency by itself.

A more confusing discovery is that the SRIN level before starting the Domino wave could affect the behavior of the PLL. I mean the level of SRIN when the chip is at A="1111" or "1010". Is SRIN supposed to influence the chip even in these standby or transparent modes? |

Wed May 19 09:16:02 2010, Stefan Ritt, DVDD Problem of DRS 4 Wed May 19 09:16:02 2010, Stefan Ritt, DVDD Problem of DRS 4

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence?

|

Yes; I used RSRLOAD to trigger readout of all channels in parallel so the asymmetry between channels of the same chip is really a big puzzle. Also during reset DSPEED indeed goes to 2.5V, but after reset the PLL will not try to lock with the external reference clock and lower DSPEED. Instead the Domino circuit just oscillates at the highest frequency by itself.

A more confusing discovery is that the SRIN level before starting the Domino wave could affect the behavior of the PLL. I mean the level of SRIN when the chip is at A="1111" or "1010". Is SRIN supposed to influence the chip even in these standby or transparent modes?

|

Just some ideas:

- Is DENABLE really kept high all the time?

- Is DRESET only applied once during initialization, after that it should stay high

- Does REFCLK+/REFCLK- really toggle at the required sampling speed / 2048?

- Is the REFCLK really a good differential signal? Note that it must be biased properly since the DRS4 inputs are high impedance

- Is the Bit1 in the Config Register really at "1" to enable the PLL?

The only way the SRIN level could affect the PLL is if you address the Config Register (A="1100") and you clock in a few bits with SRCLK.

Have you thought about 'crazy' things such as:

- Defining the DRS4 chip wronly in your CAD software so that the pins are different from what you think?

- Some soldering problem of the DRS4 chips (we had this in the past) so that some pins are not connected at all and others have shorts

I guess you checked most of the things, so I'm just wildly guessing in order to stimulate some thoughts.

The ultimate check would be to get one of the evaluation boards (I sent a few to Jean-Francois Genat some time ago...) and compare the DRS4 signals pin by pin. |

Fri Jun 18 11:31:20 2010, Jinhong Wang, DVDD Problem of DRS 4 Fri Jun 18 11:31:20 2010, Jinhong Wang, DVDD Problem of DRS 4

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

on our board some DRS chips draw a lot of current through DVDD after power-up and heat up significantly--it is true that our board doesn't have weak pull-down resistors at DENABLE and DWRITE output pins of FPGA, so this problem might have been caused by that, but a reinitialization of the Domino circuit doesn't help either. We tried different capacitors at DVDD and it seemed the larger the capacitance, the better the result--with a capacitor larger than 10nF some of the DRS chips could work happily in the normal way while if the capacitor is only 4.7nF all of them got very hot. Would you please provide some suggestions why there should be such a problem?

Thanks a lot!

|

I found that sometimes even a reinitialization fails if the pull-down resistors are missing. So instead playing with capacitors at DVDD, I would just solder two resistors on the board which should fix the problem completely.

|

Thanks! After adding pull-down resistors the voltages come back to normal.

However there is another weird problem that arises: a reset pulse seems unable to set the internal shift registers to default values. For example, after reset without addressing the Config Register the PLL will not try to lock with external reference clock. Even if I explicitly address the Config Register after reset and have the PLL locked, some channels of the chip will give null output during readout while other channels work normally. Could it be that some channels are not initiated properly with the Domino circuit?

|

Something is wrong. I have 800 chips, and they all start up fine. Check with your scope the RESET, DSPEED, DENABLE and DTAP signals. When RESET is applied, DSPEED should go to 2.5 V. When DENABLE goes high, the domino wave is started and you should see DTAP toggle. DSPEED is then lowered by the PLL until DTAP matches your external reference clock. I usually keep DENABLE high all the time after initialization, so the domino wave just continues running.

Another problem could however be the chip readout. If some channel gives null output, it could be that your readout has a problem. Do you use RSRLOAD to initialize the readout sequence?

|

Yes; I used RSRLOAD to trigger readout of all channels in parallel so the asymmetry between channels of the same chip is really a big puzzle. Also during reset DSPEED indeed goes to 2.5V, but after reset the PLL will not try to lock with the external reference clock and lower DSPEED. Instead the Domino circuit just oscillates at the highest frequency by itself.

A more confusing discovery is that the SRIN level before starting the Domino wave could affect the behavior of the PLL. I mean the level of SRIN when the chip is at A="1111" or "1010". Is SRIN supposed to influence the chip even in these standby or transparent modes?

|

Just some ideas:

- Is DENABLE really kept high all the time?

- Is DRESET only applied once during initialization, after that it should stay high

- Does REFCLK+/REFCLK- really toggle at the required sampling speed / 2048?

- Is the REFCLK really a good differential signal? Note that it must be biased properly since the DRS4 inputs are high impedance

- Is the Bit1 in the Config Register really at "1" to enable the PLL?

The only way the SRIN level could affect the PLL is if you address the Config Register (A="1100") and you clock in a few bits with SRCLK.

Have you thought about 'crazy' things such as:

- Defining the DRS4 chip wronly in your CAD software so that the pins are different from what you think?

- Some soldering problem of the DRS4 chips (we had this in the past) so that some pins are not connected at all and others have shorts

I guess you checked most of the things, so I'm just wildly guessing in order to stimulate some thoughts.

The ultimate check would be to get one of the evaluation boards (I sent a few to Jean-Francois Genat some time ago...) and compare the DRS4 signals pin by pin.

|

Hi Stefan

I designed the evaluation board for our experiment. On our boards, I encountered the similar problem when working on the PLL of DRS4. I compared the following two configuration process, which on with PLL locked, the other not,

Process1:

step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set DEnable high, thus do nothing but wait

I found DRS4 PLL working and locked.

Process 2:

Step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set Config. Register( "11111111" .of course, this step was not necessary, just to see whether SPI was working properly from DTAP when set to "11111110")

Step4: Set The read shift Register ( full read out mode)

Step5: Set DEnable high,

Step6: Set DWrite high , thus low it , and prepare to read the waveform.

Well, I found in this case, the PLL was not locked, I am sure there was no problem with my SPI configuration process of DRS4.

toggle from DTAP could be viewed, but not stable.

Any Suggestions ?

thanks. |

Fri Jun 18 11:45:18 2010, Stefan Ritt, DVDD Problem of DRS 4 Fri Jun 18 11:45:18 2010, Stefan Ritt, DVDD Problem of DRS 4

|

| Jinhong Wang wrote: |

|

Hi Stefan

I designed the evaluation board for our experiment. On our boards, I encountered the similar problem when working on the PLL of DRS4. I compared the following two configuration process, which on with PLL locked, the other not,

Process1:

step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set DEnable high, thus do nothing but wait

I found DRS4 PLL working and locked.

Process 2:

Step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set Config. Register( "11111111" .of course, this step was not necessary, just to see whether SPI was working properly from DTAP when set to "11111110")

Step4: Set The read shift Register ( full read out mode)

Step5: Set DEnable high,

Step6: Set DWrite high , thus low it , and prepare to read the waveform.

Well, I found in this case, the PLL was not locked, I am sure there was no problem with my SPI configuration process of DRS4.

toggle from DTAP could be viewed, but not stable.

Any Suggestions ?

thanks.

|

So the main difference, if I understand correctly, is the setting of the Config Register. Actually I never tried that, I always went with the default settings (all "1"). What happens if you write "00000000"? You know Bit1 controls the PLL, maybe there is a bug and the signal needs to be inverted. |

Sat Jun 19 10:09:18 2010, Jinhong Wang, DVDD Problem of DRS 4 Sat Jun 19 10:09:18 2010, Jinhong Wang, DVDD Problem of DRS 4

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Hi Stefan

I designed the evaluation board for our experiment. On our boards, I encountered the similar problem when working on the PLL of DRS4. I compared the following two configuration process, which on with PLL locked, the other not,

Process1:

step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set DEnable high, thus do nothing but wait

I found DRS4 PLL working and locked.

Process 2:

Step 1: Set DEnable and DWrite low,

Step2 : Reset DRS4 with a negative pulse of about 900 ns

Step3: Set Config. Register( "11111111" .of course, this step was not necessary, just to see whether SPI was working properly from DTAP when set to "11111110")

Step4: Set The read shift Register ( full read out mode)

Step5: Set DEnable high,

Step6: Set DWrite high , thus low it , and prepare to read the waveform.

Well, I found in this case, the PLL was not locked, I am sure there was no problem with my SPI configuration process of DRS4.

toggle from DTAP could be viewed, but not stable.

Any Suggestions ?

thanks.

|

So the main difference, if I understand correctly, is the setting of the Config Register. Actually I never tried that, I always went with the default settings (all "1"). What happens if you write "00000000"? You know Bit1 controls the PLL, maybe there is a bug and the signal needs to be inverted.

|

Hi, Stefan,

The problem was fixed by setting Reg_addr "1001" instead of "1111" when in idle state, I was confused. |

Wed May 26 19:18:09 2010, Hao Huan, High Frequency Input for DRS Wed May 26 19:18:09 2010, Hao Huan, High Frequency Input for DRS

|

Hi Stefan,

I read in the DRS datasheet that the bandwidth for the transparent mode OUT+ is only 200MHz which I think cannot be improved by any active input buffer; so if you want to operate the chip for really high frequency input, would it be better to feed on-board discriminators not from the output of DRS but from the input end?

Thanks!

|

Tue Jun 1 13:36:18 2010, Stefan Ritt, High Frequency Input for DRS Tue Jun 1 13:36:18 2010, Stefan Ritt, High Frequency Input for DRS

|

| Hao Huan wrote: |

|

Hi Stefan,

I read in the DRS datasheet that the bandwidth for the transparent mode OUT+ is only 200MHz which I think cannot be improved by any active input buffer; so if you want to operate the chip for really high frequency input, would it be better to feed on-board discriminators not from the output of DRS but from the input end?

Thanks!

|

First, the 200 MHz is not correct. Table 1 clearly states ANALOG OUTPUTS - Bandwidth (-3dB): 50 MHz. This is also shown in plot 11 (revision 0.9). But that does not necessarily mean that you have to drive your discriminators from the input of the DRS4 chip. If you use this for triggering, a 1-2 ns timing jitter does not matter, since stopping the domino wave anyhow has a 3-4 cell jitter. If you send a very fast signal though a 50 MHz low pass filter, the timing anyhow doe not change, only the slope of your signal gets lower, so you are more sensitive to noise, which in turn causes the 1-2 ns timing jitter. But I personally would not worry about that too much. Putting any signal splitting components in the input path would reduce the input bandwidth, which would be much more of an issue. |

Sun May 2 18:36:14 2010, Ignacio Di�guez Estremera, DRS4 chip model Sun May 2 18:36:14 2010, Ignacio Di�guez Estremera, DRS4 chip model

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera. |

Mon May 3 11:09:12 2010, Stefan Ritt, DRS4 chip model Mon May 3 11:09:12 2010, Stefan Ritt, DRS4 chip model

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer. |

Mon May 3 17:06:02 2010, Ignacio Di�guez Estremera, DRS4 chip model Mon May 3 17:06:02 2010, Ignacio Di�guez Estremera, DRS4 chip model

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards. |

Mon May 3 17:10:29 2010, Stefan Ritt, DRS4 chip model Mon May 3 17:10:29 2010, Stefan Ritt, DRS4 chip model

|

| Ignacio Diéguez Estremera wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards.

|

I just checked and realized that we are not allowed to give out the "huge" model since it contains parameters from the chip manufacturer's library which are confidentially. |

Mon May 3 23:21:55 2010, Ignacio Di�guez Estremera, DRS4 chip model Mon May 3 23:21:55 2010, Ignacio Di�guez Estremera, DRS4 chip model

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

Hi all,

i'm an electronics engineering student at UCM (Madrid) working on my master's thesis within the CTA collaboration. I'm designing the readout electronics for the telescope's camera, and i'm focusing in using GAPDs instead of PMTs and using the domino chip for the sampling of the signal. I was wondering if there is a spice and/or RF model of the DRS4 chip available. It would be very useful to perform some simulations before deciding to use the chip as the sampling solution for our prototypes.

If the answer is negative, can you give me some advise for modelling the chip in spice? Have you done any simulations?

Thanks in advance,

Ignacio Diéguez Estremera.

|

Yes there is a transistor-level spice model, which I used to design the chip, but you won't be happy with it: Given the 500,000+ transistors on the chip, a 100 ns simulation takes a couple of weeks. We tried to make a simplified model just for the analog input using some measured S-parameters, but found that the RF behavior of the chip is almost impossible to describe to better than let's say 50%. In the end you have to fine-tune your analog front-end experimentally, to obtain optimal bandwidth. We are just working on a reference design with gives you 850 MHz bandwidth using an active input buffer.

|

Thanks for the information.

I would like to try the huge :-) model. Can you send it to my email address? Since the input signal are pulses of a few nanoseconds at FHWM, the simulation time may be reduced. I will post some feedback in the forum once i give it a try.

Kind regards.

|

I just checked and realized that we are not allowed to give out the "huge" model since it contains parameters from the chip manufacturer's library which are confidentially.

|

Thank you for the effort anyway.

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-) |

Tue May 4 11:26:21 2010, Stefan Ritt, DRS4 chip model Tue May 4 11:26:21 2010, Stefan Ritt, DRS4 chip model

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters. |

Tue May 4 16:23:16 2010, Ignacio Di�guez Estremera, DRS4 chip model Tue May 4 16:23:16 2010, Ignacio Di�guez Estremera, DRS4 chip model

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters.

|

Thanks :-) |

Wed May 12 11:47:39 2010, Jinhong Wang, DRS4 chip model Wed May 12 11:47:39 2010, Jinhong Wang, DRS4 chip model

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters.

|

Hi, we plan to do a time interpolating among the eight channels on a single chip to obtain a maximum 40 GSPS (or, maybe 30 GSPS ) sampling rate. Hence RF behavior of the anlog input is very important for us.

Will you give us some advice on the modeling of the anlog input circuit of the chip? Perhaps just the Spice model of the analog input?

The attached S parameters I found here is for fs =1 GSPS, what about fs=5GSPS?

thanks in advance,

Jinhong Wang (wangjinh@mail.ustc.edu.cn ; alleyor.wang@gmail.com) |

Wed May 12 16:26:12 2010, Stefan Ritt, DRS4 chip model Wed May 12 16:26:12 2010, Stefan Ritt, DRS4 chip model

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Ignacio Diéguez Estremera wrote: |

|

So i guess i won't be able to include drs4 in my simulations :-(. Any other suggestions? Maybe the S-params model you where working on? Anything is better than nothing :-)

|

Please find attached the S-parameters.

|

Hi, we plan to do a time interpolating among the eight channels on a single chip to obtain a maximum 40 GSPS (or, maybe 30 GSPS ) sampling rate. Hence RF behavior of the anlog input is very important for us.

Will you give us some advice on the modeling of the anlog input circuit of the chip? Perhaps just the Spice model of the analog input?

The attached S parameters I found here is for fs =1 GSPS, what about fs=5GSPS?

thanks in advance,

Jinhong Wang (wangjinh@mail.ustc.edu.cn ; alleyor.wang@gmail.com)

|

To be honest, we never really succeeded to do any good simulation above let's say 500 MHz. We carefully tried to simulate the bond wire of the chip, the parasitic capacitances of the traces of the chip etc. but we always were off by a factor or two or so. Other groups reported the same problems. Some even did some 3D simulation model, without success. So our conclusion is that if you are interested in anything precise above 500 MHz, do a measurement.

So our current best design is with the THS4508. There is an AC coupled version going to 600 MHz, and a DC coupled version (uses more power) going to 800 MHz (-3dB). If you use passive inputs with a transformer for example, you can't go above 220 MHz. Next week I will publish both designs in this forum. |

Wed May 5 22:30:50 2010, Ignacio Di�guez Estremera, Random noise spec in datasheet Wed May 5 22:30:50 2010, Ignacio Di�guez Estremera, Random noise spec in datasheet

|

Hi,

According to DRS4's datasheet, the random noise is 0.35mVrms. Is this the input equivalent noise voltage? It is computed over the 0-950MHz frequency band?

Regards. |

Thu May 6 08:15:39 2010, Stefan Ritt, Random noise spec in datasheet Thu May 6 08:15:39 2010, Stefan Ritt, Random noise spec in datasheet

|

| Ignacio Diéguez Estremera wrote: |

|

Hi,

According to DRS4's datasheet, the random noise is 0.35mVrms. Is this the input equivalent noise voltage? It is computed over the 0-950MHz frequency band?

Regards.

|

You cannot compare the DRS4 noise directly with an amplifier for example. The noise mainly comes from variations of the charge injection into the storage cells, and some noise during the readout process, which happens in a completely different frequency domain than the sampling.

So what I did is to keep the inputs open, measure a 1024-bin waveform, and compute the RMS of this waveform. So I believe that this is kind of equivalent noise voltage from 1-950 MHz. It does not start from zero since very low frequency noise (like 50 Hz) just causes a baseline shift and does not influence the RMS, but this is not so important since in most applications people do an event-by-event baseline subtraction to get rid of low frequency noise in their apparatus. The 0.35 mV RMS also depend on the electronics around the chip. On our USB evaluation board the noise it typically smaller (0.31 mV RMS), while in some VME board we measure 0.42 mV RMS. If you do the perfect analog design around the chip, you can maybe push this maybe even lower. |

Tue Mar 30 22:57:34 2010, Hao Huan, ROFS Configuration Tue Mar 30 22:57:34 2010, Hao Huan, ROFS Configuration

|

Hi Stefan,

according to the DRS4 datasheet, if we want an input range centered around U0, the ROFS should be 1.55V-U0. However when I read the codes of the evaluation board application, ROFS seems to be 1.6V-1.25*U0 where the coefficient 1.25 is said to come from sampling cell charge injection correction. Is it the right equation to use? What exactly does that charge injection correction mean?

Thanks a lot.

|

Thu Apr 15 13:48:40 2010, Stefan Ritt, ROFS Configuration Thu Apr 15 13:48:40 2010, Stefan Ritt, ROFS Configuration

|

| Hao Huan wrote: |

|

Hi Stefan,

according to the DRS4 datasheet, if we want an input range centered around U0, the ROFS should be 1.55V-U0. However when I read the codes of the evaluation board application, ROFS seems to be 1.6V-1.25*U0 where the coefficient 1.25 is said to come from sampling cell charge injection correction. Is it the right equation to use? What exactly does that charge injection correction mean?

Thanks a lot.

|

1.55V-U0 is the theoretical values, but there are certain "dirt" effects like chip-to-chip variation and charge injection. The difference between various chips is easily 20-30mV, so there is not a single "correct" value. The formula 1.6V-1.25*U0 I developed for a special evaluation board, where it kind of worked better than the theoretical value, but I never made systematic studies. One should average over several chips and use some solid average there. Best is if you try both formulas and check what give you the better linearity. |

Mon Apr 5 17:50:39 2010, Heejong Kim, version 1.2 evaluation board with firmware 13279? Mon Apr 5 17:50:39 2010, Heejong Kim, version 1.2 evaluation board with firmware 13279?

|

Hi, Stefan,

I found that my collaborator bought 2 older version of evaluation board before.

They are the version 1.2 in plastics case with firmware 13191.

Can I upgrade the firmware from 13191 to 13279?

I'm wondering if the older version of evaluation board is working with firmware 13279.

Thanks,

Heejong

|

Wed Apr 14 16:34:28 2010, Stefan Ritt, version 1.2 evaluation board with firmware 13279? Wed Apr 14 16:34:28 2010, Stefan Ritt, version 1.2 evaluation board with firmware 13279?

|

| Heejong Kim wrote: |

Hi, Stefan,

I found that my collaborator bought 2 older version of evaluation board before.

They are the version 1.2 in plastics case with firmware 13191.

Can I upgrade the firmware from 13191 to 13279?

I'm wondering if the older version of evaluation board is working with firmware 13279.

Thanks,

Heejong

|

I checked and there is no significant difference between the two revisions, so I would just leave it. |

Tue Apr 28 11:44:07 2009, Stefan Ritt, Simple example application to read a DRS evaluation board Tue Apr 28 11:44:07 2009, Stefan Ritt, Simple example application to read a DRS evaluation board

|

Several people asked for s simple application to guide them in writing their own application to read out a DRS board. Such an application has been added in software revions 2.1.1 and is attached to this message. This example program drs_exam.cpp written in C++ does the following necessary steps to access a DRS board:

- Crate a "DRS" object and scan all USB devices

- Display found DRS boards

- Initialize the first found board and set the sampling frequency to 5 GSPS

- Enable internal trigger on channel #1 with 250 mV threshold

- Start acquisition and wait for a trigger

- Read two waveforms (both time and amplitude)

- Repeat this 10 times

I know that we are still missing a good documentation for the DRS API, but I have not yet found the time to do that. I hope the example program is enough for most people to start writing own programs. For Windows users (MS Visual C++ 8.0) there is a drs.sln project file, and for linux users there is a Makefile which can be used to compile this example program.

|

Wed Apr 29 07:57:33 2009, Stefan Ritt, Simple example application to read a DRS evaluation board Wed Apr 29 07:57:33 2009, Stefan Ritt, Simple example application to read a DRS evaluation board

|

| Stefan Ritt wrote: |

|

Several people asked for s simple application to guide them in writing their own application to read out a DRS board. Such an application has been added in software revions 2.1.1 and is attached to this message. This example program drs_exam.cpp written in C++ does the following necessary steps to access a DRS board:

- Crate a "DRS" object and scan all USB devices

- Display found DRS boards

- Initialize the first found board and set the sampling frequency to 5 GSPS

- Enable internal trigger on channel #1 with 250 mV threshold

- Start acquisition and wait for a trigger

- Read two waveforms (both time and amplitude)

- Repeat this 10 times

I know that we are still missing a good documentation for the DRS API, but I have not yet found the time to do that. I hope the example program is enough for most people to start writing own programs. For Windows users (MS Visual C++ 8.0) there is a drs.sln project file, and for linux users there is a Makefile which can be used to compile this example program.

|

One note: The program drs_exam.cpp published in the previous message needs the current version of the DRS library in DRS.cpp and DRS.h. They are contained in the software release 2.1.1 which has to be downloaded. For simplicity, I attached the two files to this message. |

Mon Apr 5 17:57:41 2010, Heejong Kim, Simple example application to read a DRS evaluation board Mon Apr 5 17:57:41 2010, Heejong Kim, Simple example application to read a DRS evaluation board

|

| Stefan Ritt wrote: |

|

Several people asked for s simple application to guide them in writing their own application to read out a DRS board. Such an application has been added in software revions 2.1.1 and is attached to this message. This example program drs_exam.cpp written in C++ does the following necessary steps to access a DRS board:

- Crate a "DRS" object and scan all USB devices

- Display found DRS boards

- Initialize the first found board and set the sampling frequency to 5 GSPS

- Enable internal trigger on channel #1 with 250 mV threshold

- Start acquisition and wait for a trigger

- Read two waveforms (both time and amplitude)

- Repeat this 10 times

I know that we are still missing a good documentation for the DRS API, but I have not yet found the time to do that. I hope the example program is enough for most people to start writing own programs. For Windows users (MS Visual C++ 8.0) there is a drs.sln project file, and for linux users there is a Makefile which can be used to compile this example program.

|

Hi, Stefan,

drs_exam.cpp is working good to read-out one board.

Now I would like to read-out two boards at the same time using the same trigger( external or internal).

I'm trying to understand and modify the original code for control two board.

Meantime, it would be very appreciated if you give any tips for this.

Thanks,

Heejong |

Tue Apr 13 14:15:16 2010, Stefan Ritt, Simple example application to read a DRS evaluation board Tue Apr 13 14:15:16 2010, Stefan Ritt, Simple example application to read a DRS evaluation board

|

| Heejong Kim wrote: |

|

| Stefan Ritt wrote: |

|

Several people asked for s simple application to guide them in writing their own application to read out a DRS board. Such an application has been added in software revions 2.1.1 and is attached to this message. This example program drs_exam.cpp written in C++ does the following necessary steps to access a DRS board:

- Crate a "DRS" object and scan all USB devices

- Display found DRS boards

- Initialize the first found board and set the sampling frequency to 5 GSPS

- Enable internal trigger on channel #1 with 250 mV threshold

- Start acquisition and wait for a trigger

- Read two waveforms (both time and amplitude)

- Repeat this 10 times

I know that we are still missing a good documentation for the DRS API, but I have not yet found the time to do that. I hope the example program is enough for most people to start writing own programs. For Windows users (MS Visual C++ 8.0) there is a drs.sln project file, and for linux users there is a Makefile which can be used to compile this example program.

|

Hi, Stefan,

drs_exam.cpp is working good to read-out one board.

Now I would like to read-out two boards at the same time using the same trigger( external or internal).

I'm trying to understand and modify the original code for control two board.

Meantime, it would be very appreciated if you give any tips for this.

Thanks,

Heejong

|

The evaluation boards are not really made for multi-board applications. What you have to do is to maintain an external trigger which synchronizes the boards. So you need:

- two boards connected to two USB ports

- an external flip-flop connected to the two trigger inputs of both boards

If a trigger is sent to the flip-flop, it sends a trigger to both evaluation boards. You poll on one of the boards to see if it has triggered (vis IsBusy()), then you read out both boards. Now you have to reset the external flip-flop somehow from the computer. If you have a CAMAC I/O board or some other means of sending a logical signal to it, that could do the job. From the software point, you get a "DRS" object upon initialization, which contains then two "DRSBoard" objects, over which you can iterate. Look at the "drscl" program from the distribution on how to do that. |

Fri Apr 9 17:14:45 2010, Hao Huan, Baseline Variation In Data Fri Apr 9 17:14:45 2010, Hao Huan, Baseline Variation In Data

|

Hi Stefan,

when I sample a constant input with the DRS 4 chip, there was a baseline variation showing up as a saw-tooth pattern which grows with the absolute value of the differential input. Do you think this is the kind of baseline variation mentioned in the evaluation board manual, i.e. coming from clock jitter in ADC sampling?

Thanks a lot!

|

Tue Apr 13 13:56:07 2010, Stefan Ritt, Baseline Variation In Data Tue Apr 13 13:56:07 2010, Stefan Ritt, Baseline Variation In Data

|

| Hao Huan wrote: |

|

Hi Stefan,

when I sample a constant input with the DRS 4 chip, there was a baseline variation showing up as a saw-tooth pattern which grows with the absolute value of the differential input. Do you think this is the kind of baseline variation mentioned in the evaluation board manual, i.e. coming from clock jitter in ADC sampling?

Thanks a lot!

|

Please post an oscilloscope screenshot here and I can tell you. |

Tue Apr 13 10:45:18 2010, lorenzo neri, evaluation board used like a counter Tue Apr 13 10:45:18 2010, lorenzo neri, evaluation board used like a counter

|

Hi all

it is possible to use the evaluation board like a counter?

I'm interested in the arriving time of all self trigger event in to a channel.

the input signal are 2V TTL of 10 ns at 50ohm, and the time acquisition window is 1 second.

can someone help me?

thanks in advance,

Lorenzo |

Tue Apr 13 13:12:43 2010, Stefan Ritt, evaluation board used like a counter Tue Apr 13 13:12:43 2010, Stefan Ritt, evaluation board used like a counter

|

| lorenzo neri wrote: |

|

Hi all

it is possible to use the evaluation board like a counter?

I'm interested in the arriving time of all self trigger event in to a channel.

the input signal are 2V TTL of 10 ns at 50ohm, and the time acquisition window is 1 second.

|

The evaluation board is as good or bad as an digital oscilloscope to work like a counter. At 1 GSPS, you have a window of one microsecond, which is certainly too short for your application. |

Sun Mar 21 02:03:44 2010, Hao Huan, PLL Loop Filter Configuration Sun Mar 21 02:03:44 2010, Hao Huan, PLL Loop Filter Configuration

|

Hi Stefan,

in the datasheet it says at 6GSPS the typical loop filter parameters are 220Ω, 2.2nF and 27nF. If I want to run the Domino wave nominally at 1GHz, i.e. with a reference clock frequency around 0.5MHz, is there any recommended loop filter configuration? Is the setup of the evaluation board, that is, 220Ω, 3.3nF and 33nF an optimal choice?

Thank you very much.

|

Mon Mar 22 09:12:19 2010, Stefan Ritt, PLL Loop Filter Configuration Mon Mar 22 09:12:19 2010, Stefan Ritt, PLL Loop Filter Configuration

|

| Hao Huan wrote: |

|

in the datasheet it says at 6GSPS the typical loop filter parameters are 220Ω, 2.2nF and 27nF. If I want to run the Domino wave nominally at 1GHz, i.e. with a reference clock frequency around 0.5MHz, is there any recommended loop filter configuration? Is the setup of the evaluation board, that is, 220Ω, 3.3nF and 33nF an optimal choice?

|

The setup of the evaluation board is a good compromise which runs between 1 GHz and 5 GHz. Unfortunately I never found the time to investigate this in more detail. So if someone is willing to measure settling time and phase jitter with various combinations of R, C1 and C2, I'm more than happy to include this into the datasheet. |

Tue Mar 9 23:28:45 2010, Hao Huan, Serial Interface Frequency of the DRS Chip Tue Mar 9 23:28:45 2010, Hao Huan, Serial Interface Frequency of the DRS Chip

|

Hi Stefan,

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

Thanks!

|

Wed Mar 10 10:07:28 2010, Stefan Ritt, Serial Interface Frequency of the DRS Chip Wed Mar 10 10:07:28 2010, Stefan Ritt, Serial Interface Frequency of the DRS Chip

|

| Hao Huan wrote: |

|

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

|

The reason for the 16.5 MHz is the following:

After each block of 32 bins, the DRS4 chip switches an internal segment, which causes some small spike at the analog output of the chip. This spike is a bit wider than 30ns, so if everything is digitized with 33 MHz, then you see small spiked each 32 cells. The appropriate solution would be to modify the firmware to digitize all cells with 30ns (33 MHz) and all cells with the spike with ~50 ns (20 MHz). If you do the ROI readout mode, you don't know for the first 10 cells if one of them belong to this class, since the cell address takes 10 cycles to be read out. So you would first have to read 10 cells, and then if you realize that one of them is one of the problematic ones (cell number modulo 32 is zero), you have to re-read the first 10 cells, and digitize the problematic cell with a longer settling time. Now this is a bit complicated to implement in the firmware, so I was just too lazy to do it and decided to digitize everything with 16.5 MHz. But if you are worried about the dead time, you should consider implementing the mentioned algorithm. |

Thu Mar 18 21:38:10 2010, Hao Huan, Serial Interface Frequency of the DRS Chip Thu Mar 18 21:38:10 2010, Hao Huan, Serial Interface Frequency of the DRS Chip

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

|

The reason for the 16.5 MHz is the following: