Mon Dec 15 13:37:38 2008, Stefan Ritt, Welcome Mon Dec 15 13:37:38 2008, Stefan Ritt, Welcome

|

Welcome to the DRS4 Discussion Forum. This forum contains information and discussions related to the DRS4 chip. Please subscribe to this forum to receive automatic email updates. If you have any technical questions, please feel free to post it here. |

Wed Jan 14 12:02:04 2009, Stefan Ritt, External Trigger Input requirements Wed Jan 14 12:02:04 2009, Stefan Ritt, External Trigger Input requirements

|

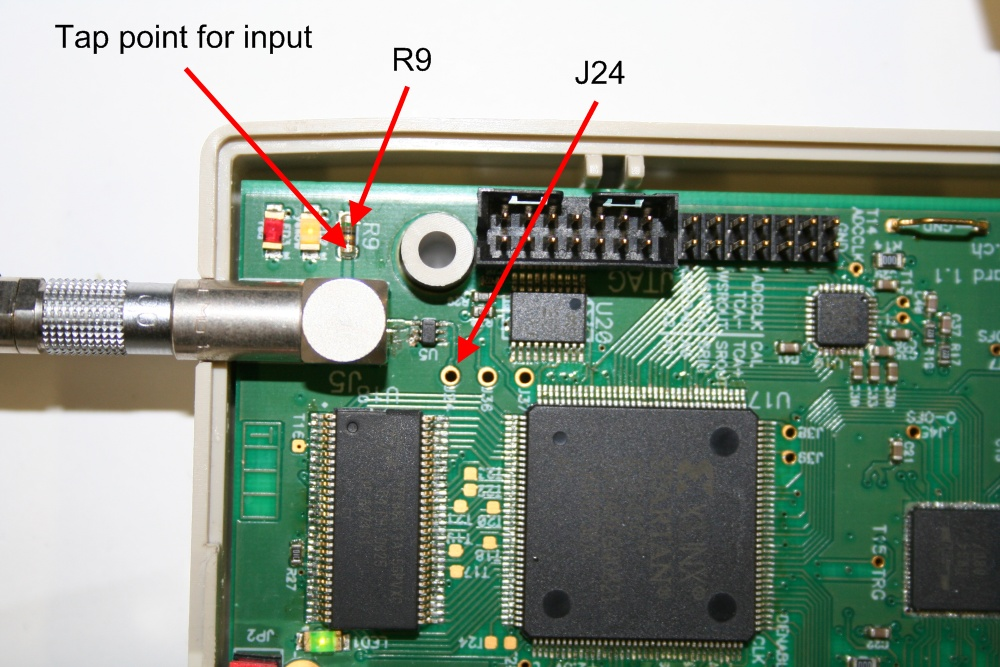

Several people mentioned that the external trigger input (TTL) does not work on the DRS4 Evaluation Board Rev. 1.1. This is not true. The requirement however is that the input signal must exceed approximately 1.8V. Since the input is terminated with 50 Ohms, not all TTL drivers may deliver enough current to exceed this threshold. To verify this, the trigger signal can be monitored with an oscilloscope at test point J24. Only if the input signal exceeds 1.8V, the signal will be seen at J24 and correctly trigger the FPGA. If the TTL driver is too weak, the termination resistor R9 can be optionally removed, but care should then be taken that reflections in the trigger input do not cause double triggers. The locations of the tap point for the input signal, the termination resistor R9 and the tap point J24 after the input level converter U5 are shown in this image:

|

Wed Jan 14 13:41:44 2009, Stefan Ritt, External Trigger Input requirements Wed Jan 14 13:41:44 2009, Stefan Ritt, External Trigger Input requirements

|

Another tricky issue comes from the fact that the external TTL trigger and the comparator are in a logical OR. So if the comparator level is set such that the signal is always over the threshold, the trigger is always "on" and the TTL trigger does not have any effect. It is therefore necessary to set the analog trigger level to a very high value in order to make the TTL trigger work. |

Wed Feb 11 12:21:07 2009, Stefan Ritt, Corrected datasheet Rev. 0.8 Wed Feb 11 12:21:07 2009, Stefan Ritt, Corrected datasheet Rev. 0.8

|

Please note the new datasheet Rev. 0.8 available from the DRS web site. It fixes the label of pin #76, which was AGND but is actualy AVDD. The input IN8+ is located at pin #20 and not at pin #19 as described in the old table 2. |

Mon Feb 23 09:24:24 2009, Stefan Ritt, Rise-time measurements Mon Feb 23 09:24:24 2009, Stefan Ritt, Rise-time measurements

|

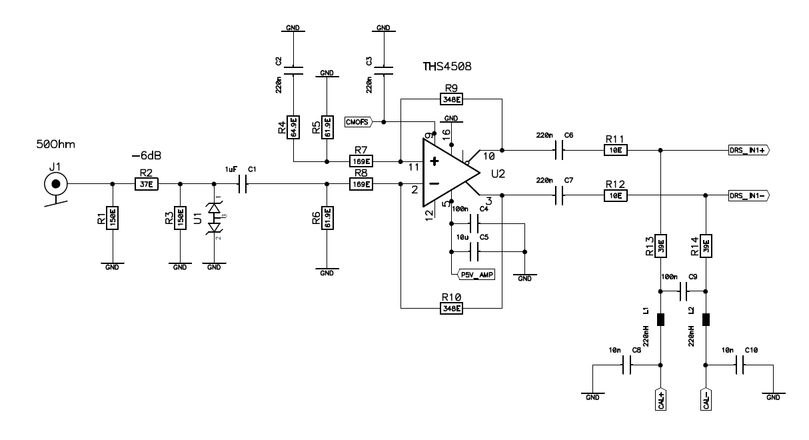

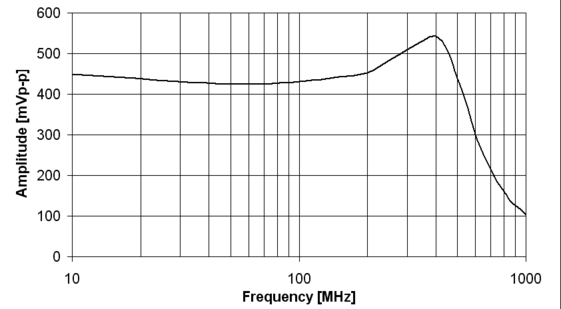

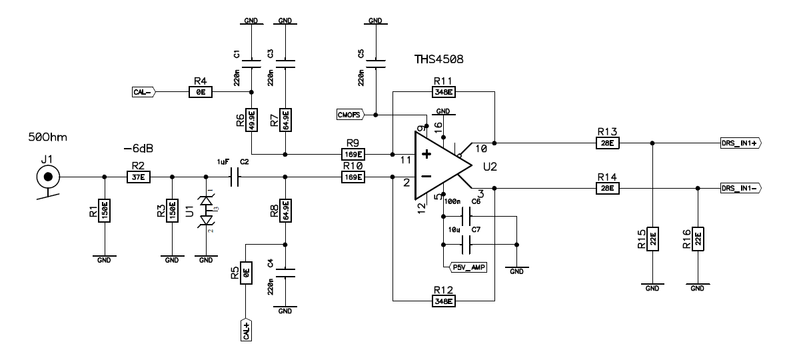

Many applications using the DRS4 need to measure fast rising signals, like for PMTs or MCPs. This short note shows the minimal rise-times which can be measured with different input signal conditioning.

Evaluation Board

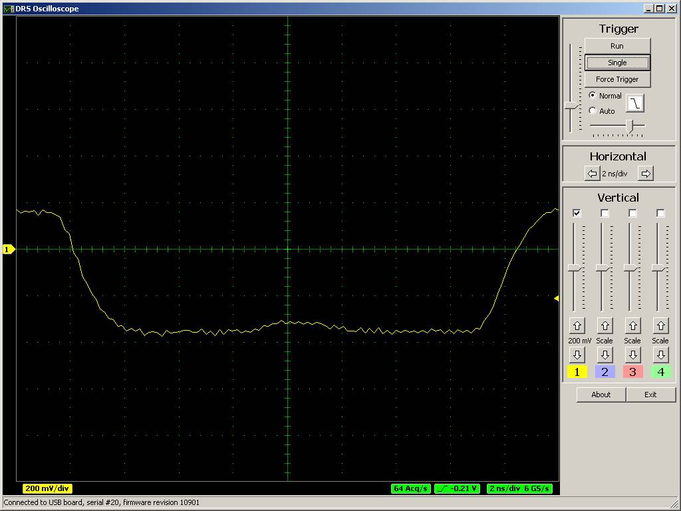

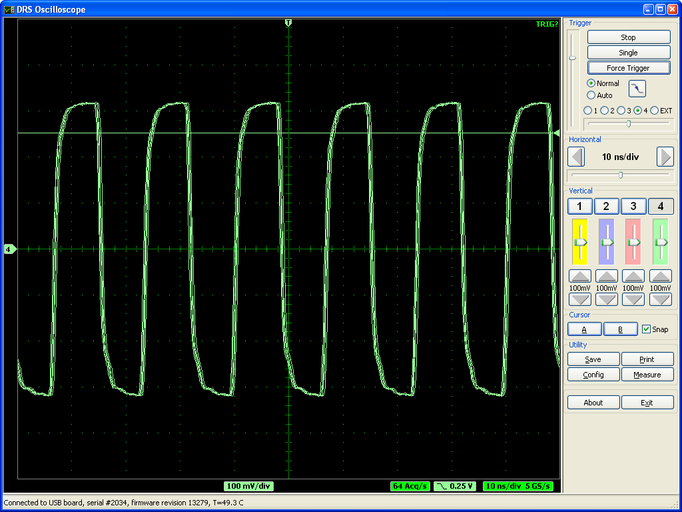

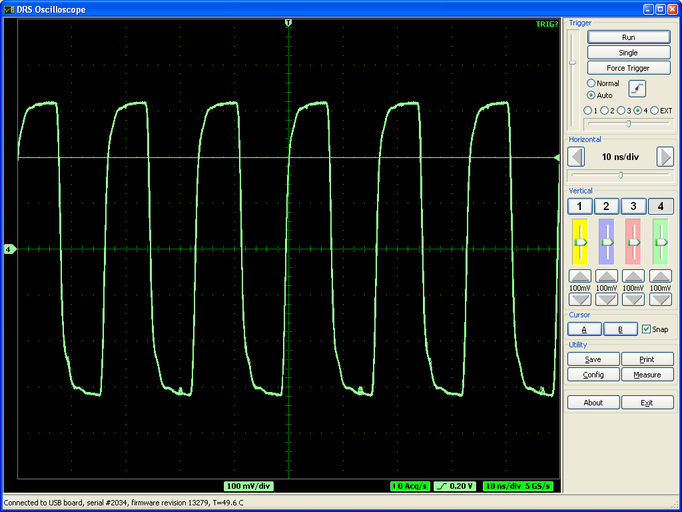

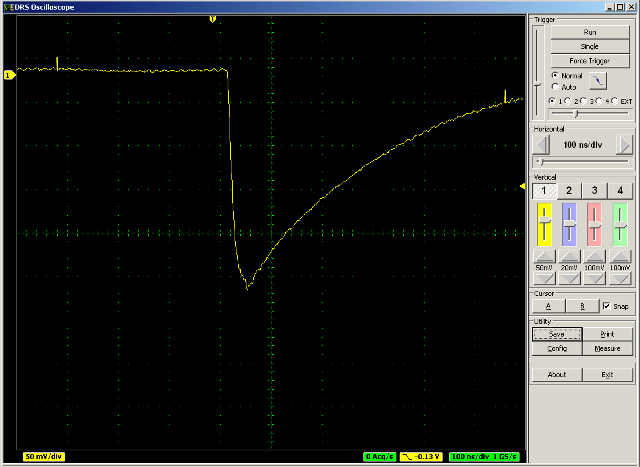

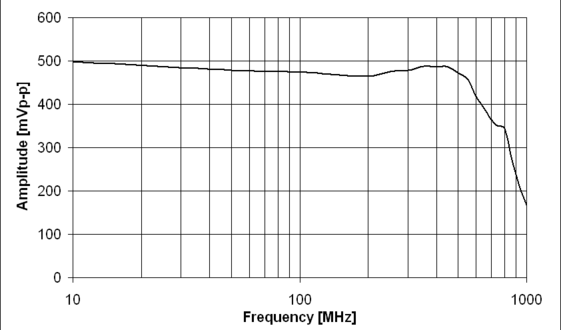

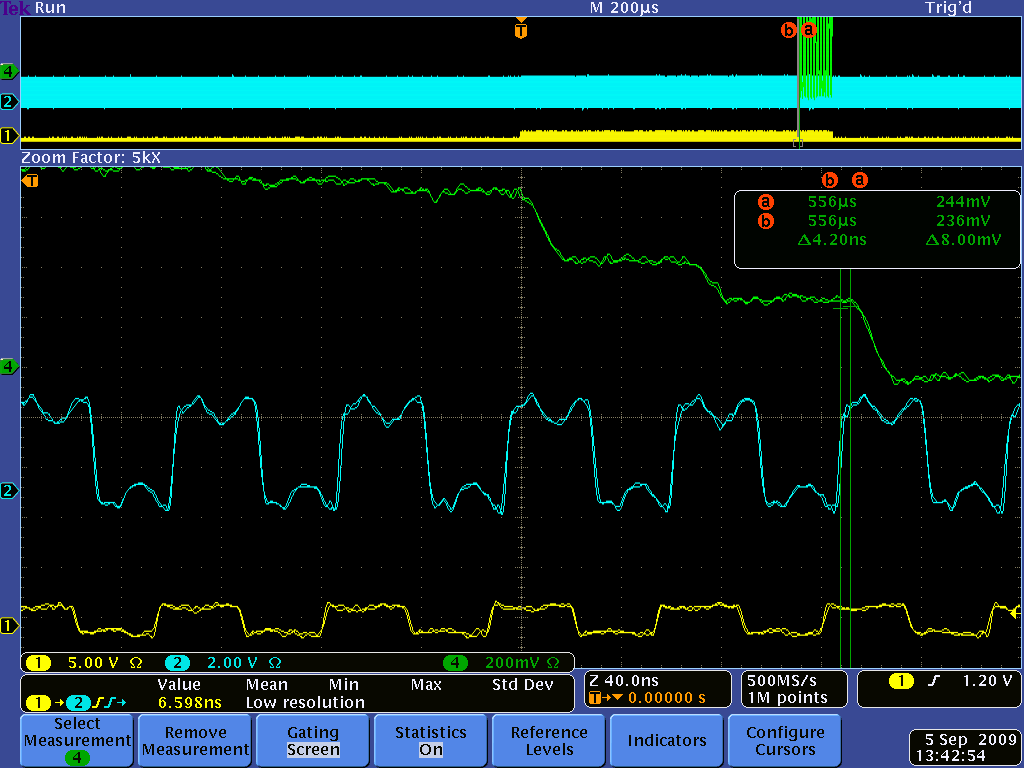

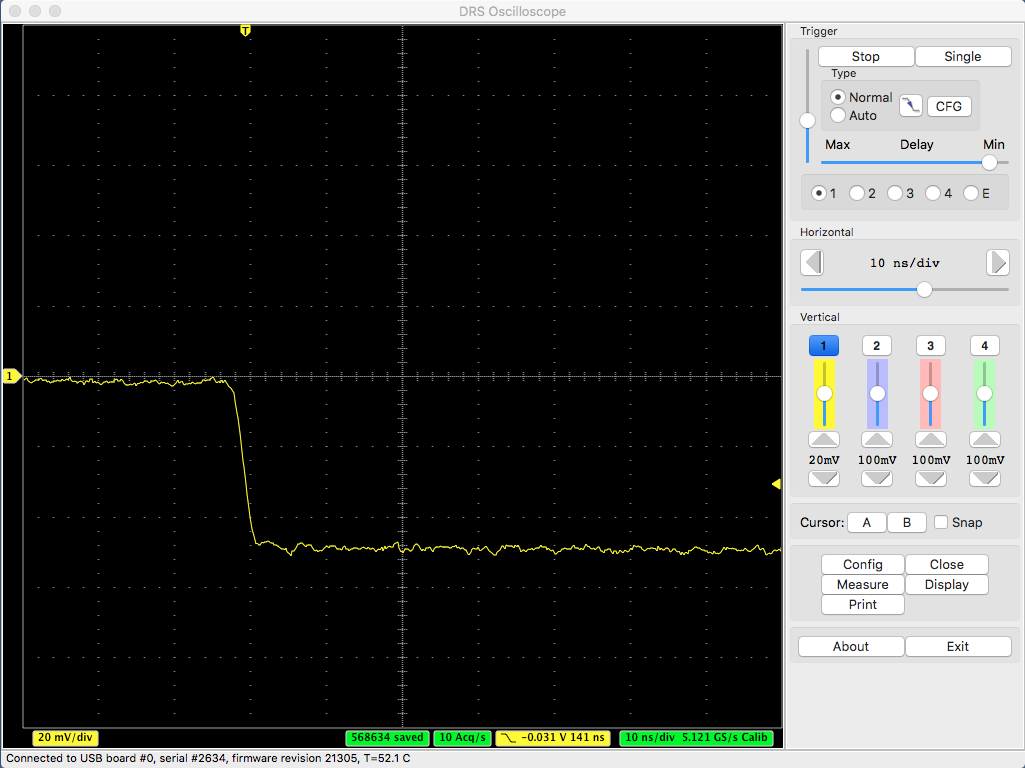

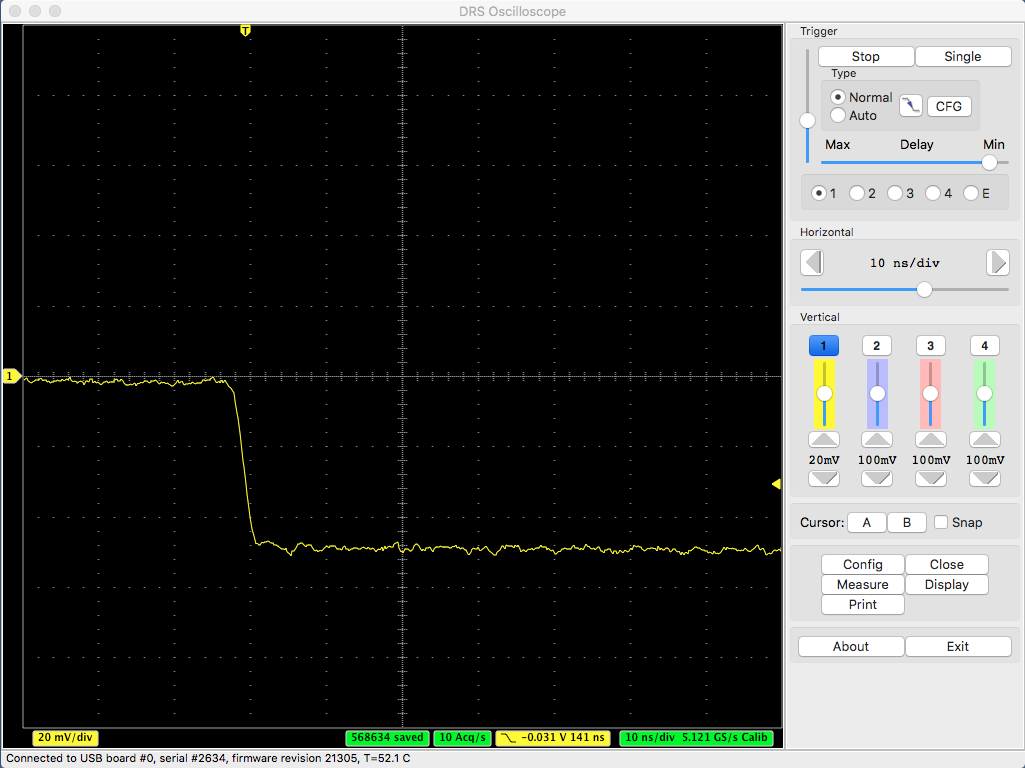

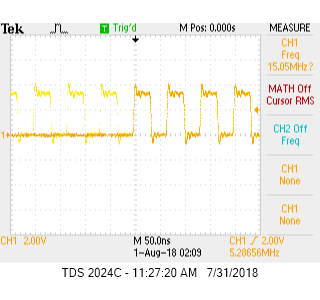

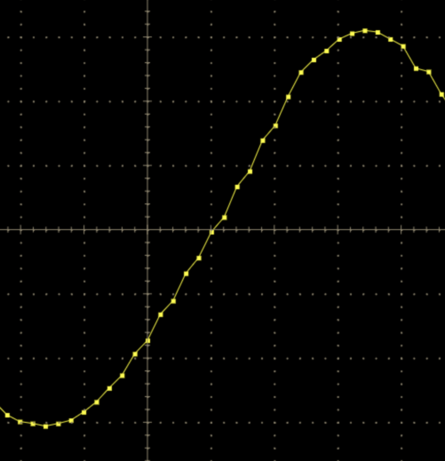

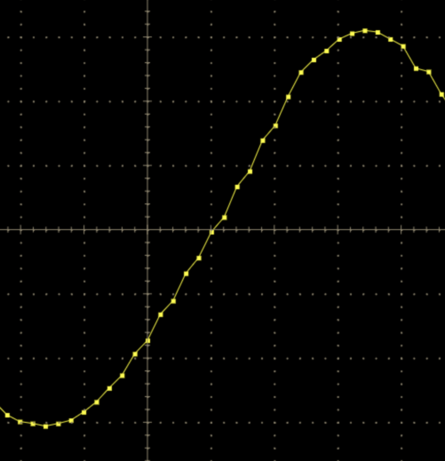

The evaluation board contains four passive transformers ADT1-1WT from Mini-Circuits to convert the single-ended input signal into a differential signal. Although these parts are rated 800 MHz bandwidth (-3dB), they have hard time to drive the DRS4 inputs. This is because at high frequencies the input impedance of DRS4 becomes pretty small (~20 Ohm at 500 MHz) due to its capacitive nature. Furthermore, each transformer drives two DRS4 inputs (channel cascading) which enhances this problem by a factor of two. We made a quick test sending a signal to the evaluation board with a rise time of 277ps and a fall time of 280ps. The result measured with the evaluation board is seen here:

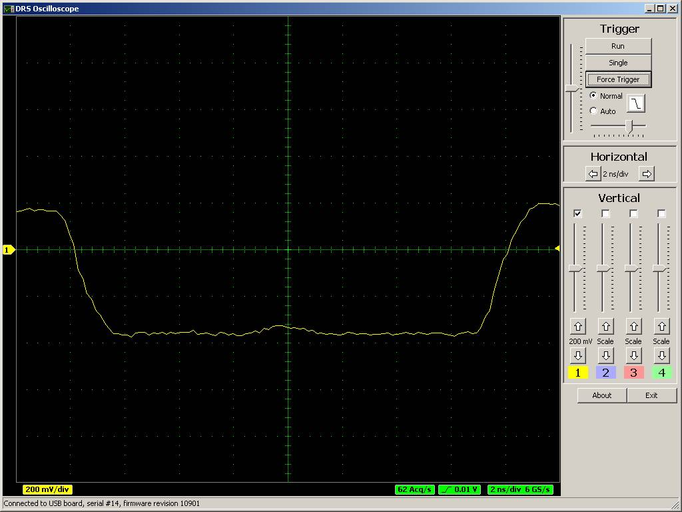

The measured rise-time (10%-90%) is only about 2ns. Disconnecting the second channel from each transformer improves this situation a bit:

so the rise-time comes down to ~1.6ns.

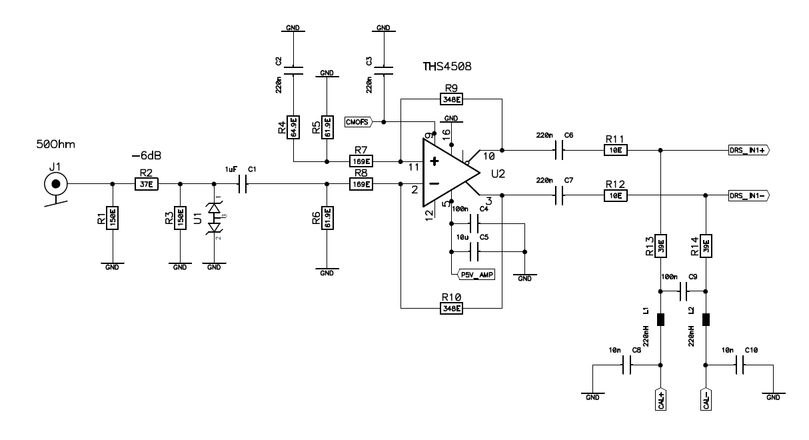

Active ADA4937 driver

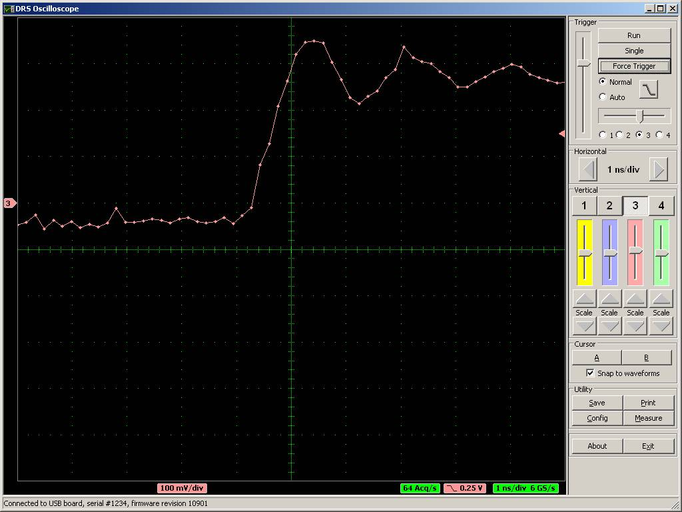

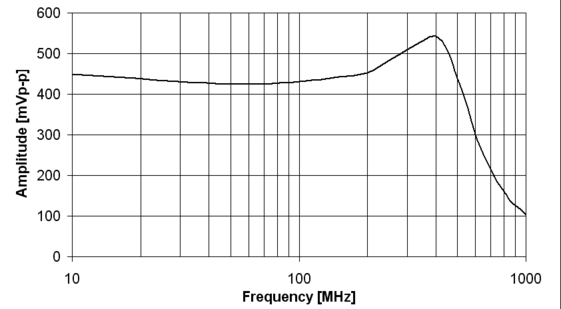

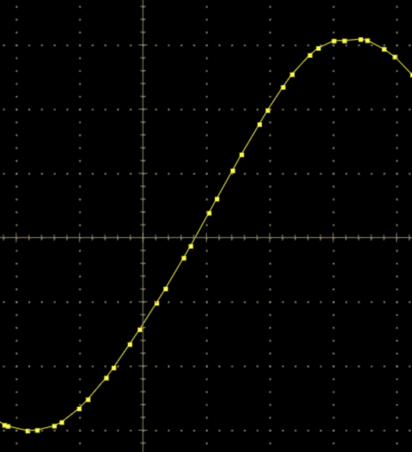

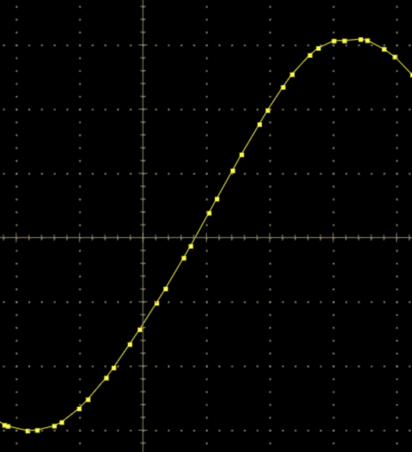

We tested the behavior using an active buffer ADA4937 to replace the passive transformer. Without the DRS4 connected to this buffer, we measured with the oscilloscope a rise time of 408ps and a fall time of 644ps. When we connect the DRS4 (single channel), this values increase to 702ps (rise) and 1400ps (fall), all measured with a differential oscilloscope probe (WL300 4 GHz Bandwidth, LeCroy 7300A, 3 GHz Bandwidth). In this case the rise time seen by the DRS4 is wieth ~700ps accordingly shorter:

(The signal was not properly terminated and therefore we have a small overswing).

Conclusion

To obtain an optimal rise-time measurement, the design of the input stage is rather important. A fast active driver seems to do a better job than a passive transformer (which was used on the evaluation board for power reasons). Connecting only one DRS4 channel to the input improves the rise-time measurement significantly. If channel cascading is still needed, a design should use one driver for each channel, and not driver two or more DRS4 inputs from a single buffer.

If anybody comes up with an even better input driver, I'm happy to publish the results here. |

Mon Apr 27 15:09:49 2009, Stefan Ritt, Amplitude and Timing calibration for DRS4 Evaluation Board Mon Apr 27 15:09:49 2009, Stefan Ritt, Amplitude and Timing calibration for DRS4 Evaluation Board

|

This is a quick notification to all users of the current DRS4 evaluation board.

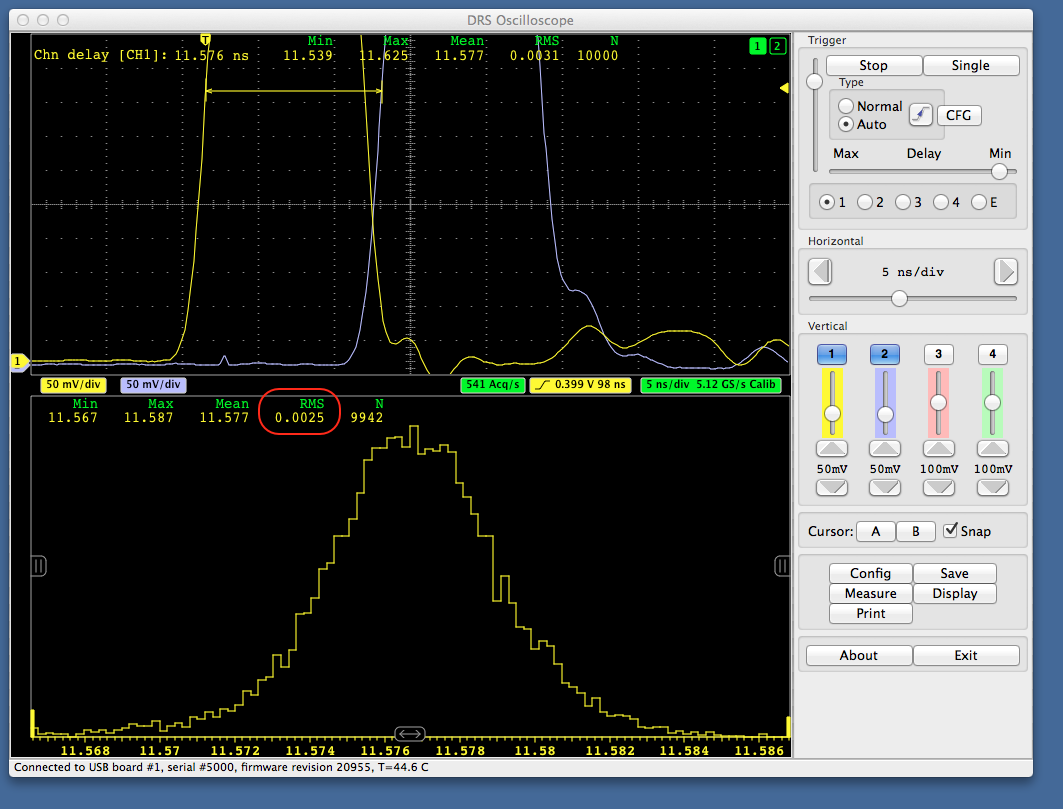

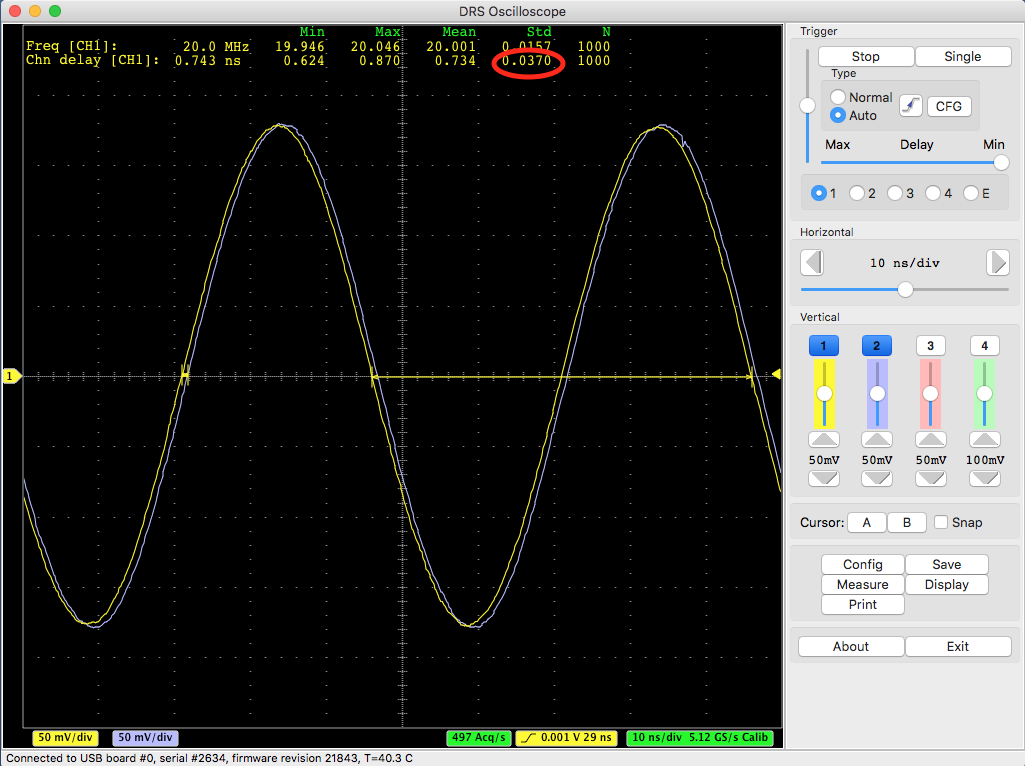

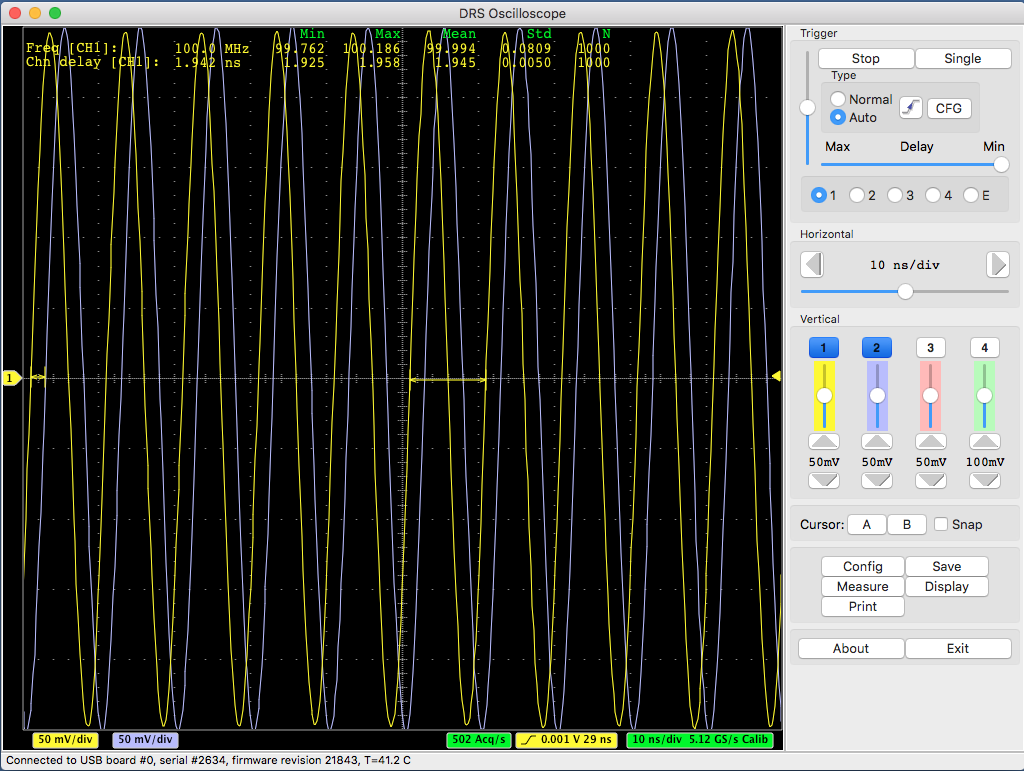

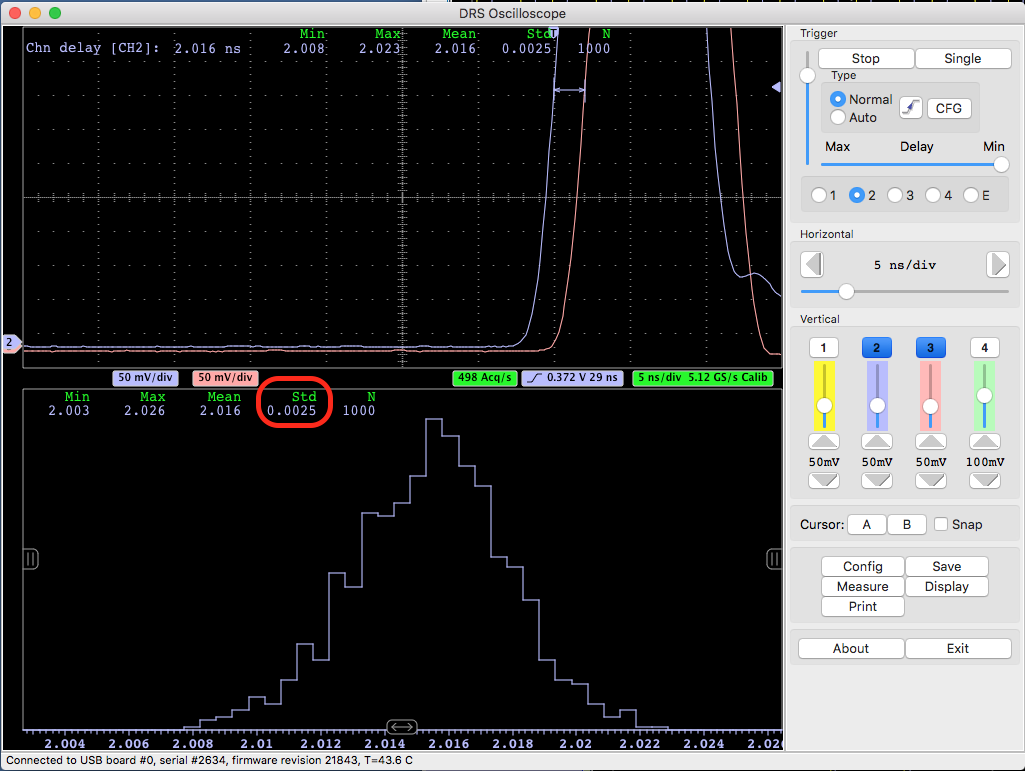

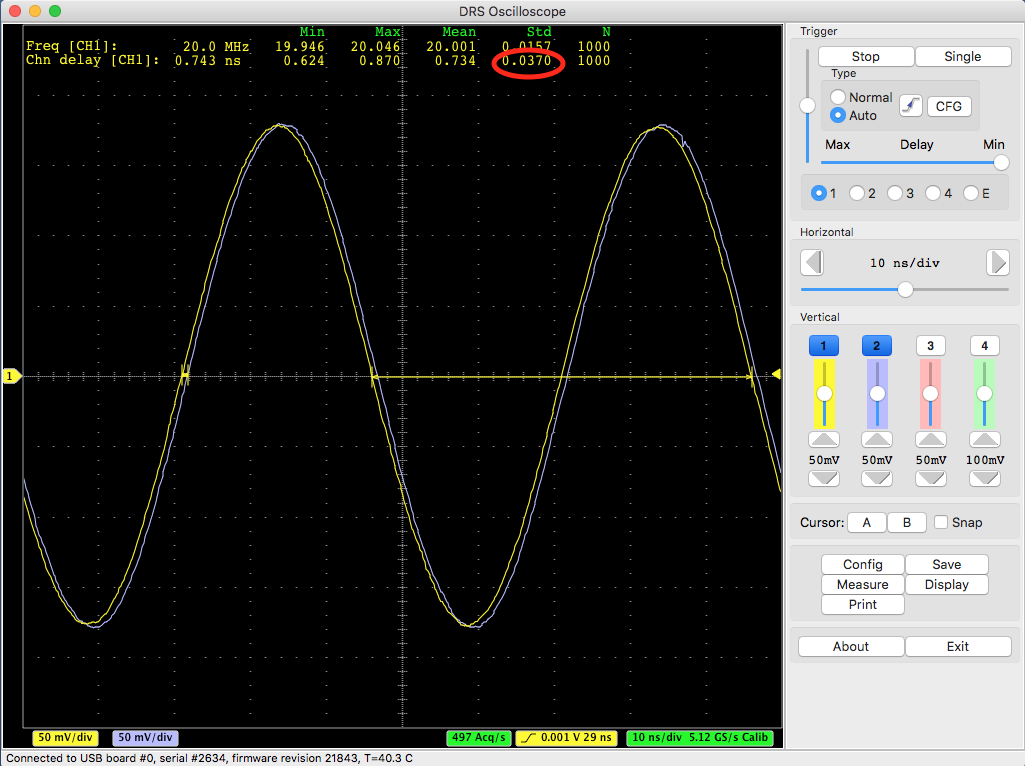

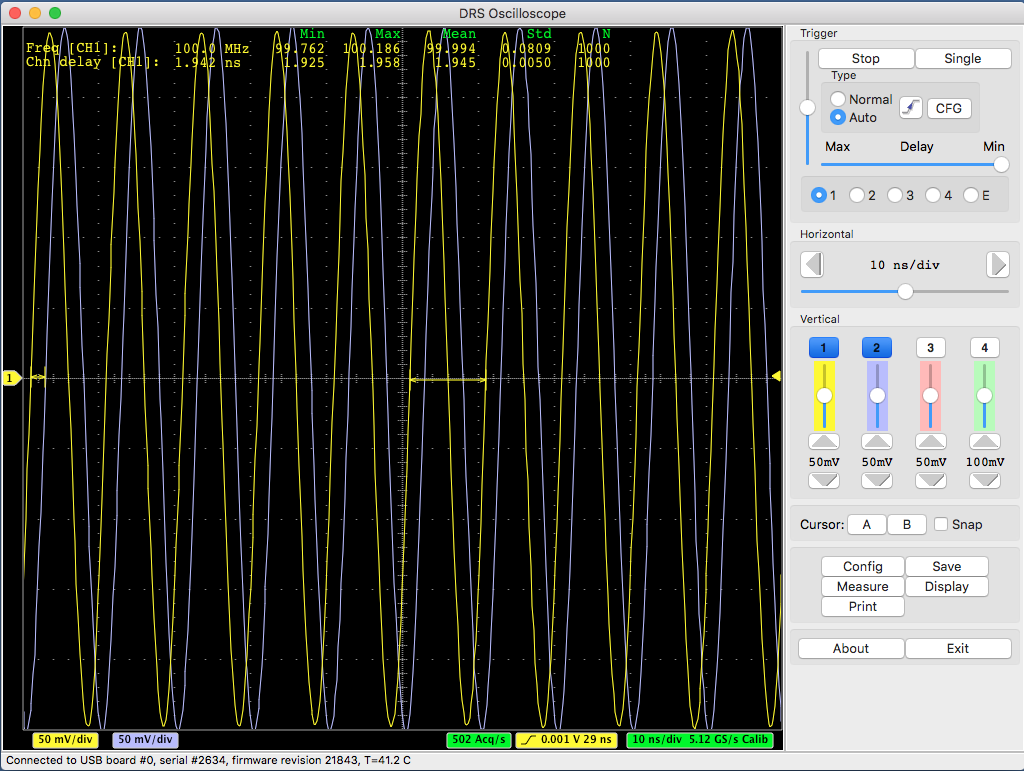

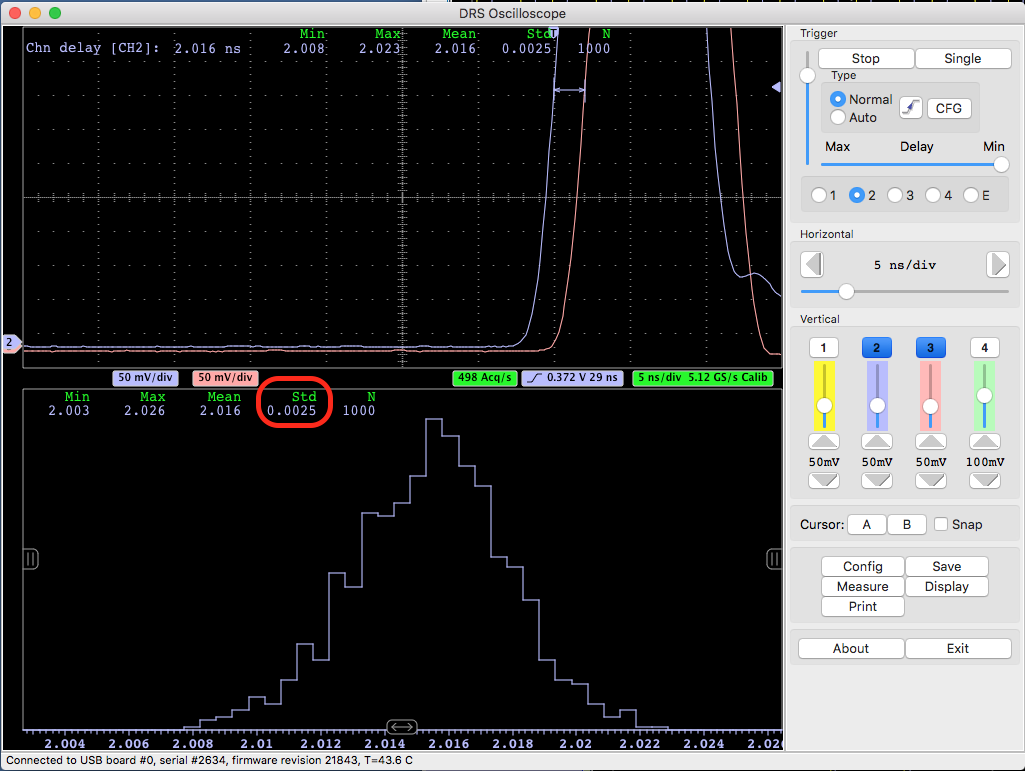

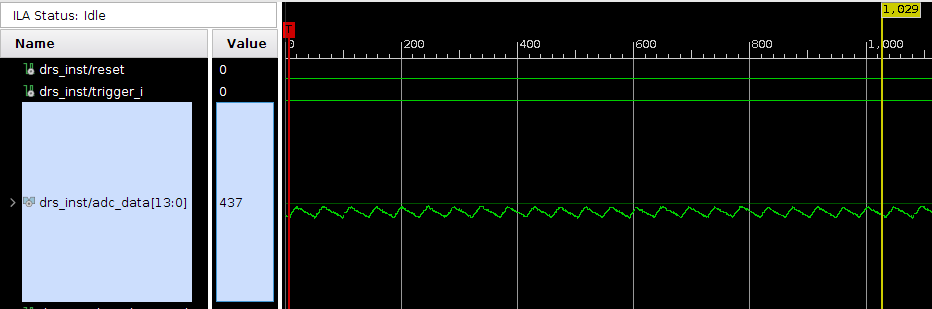

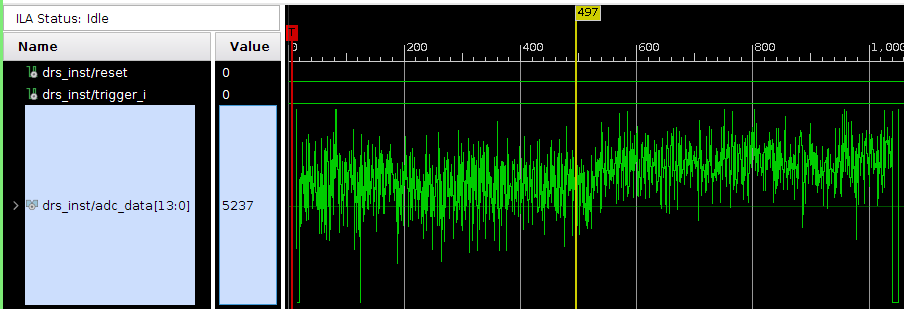

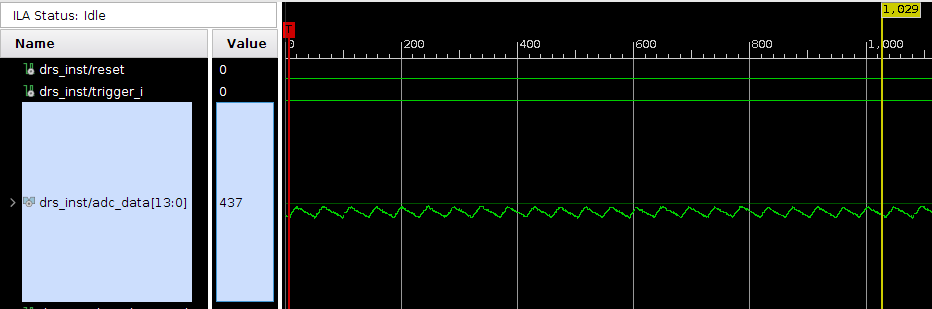

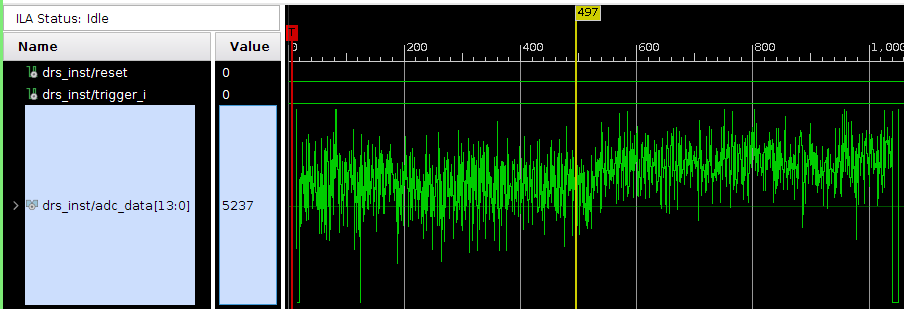

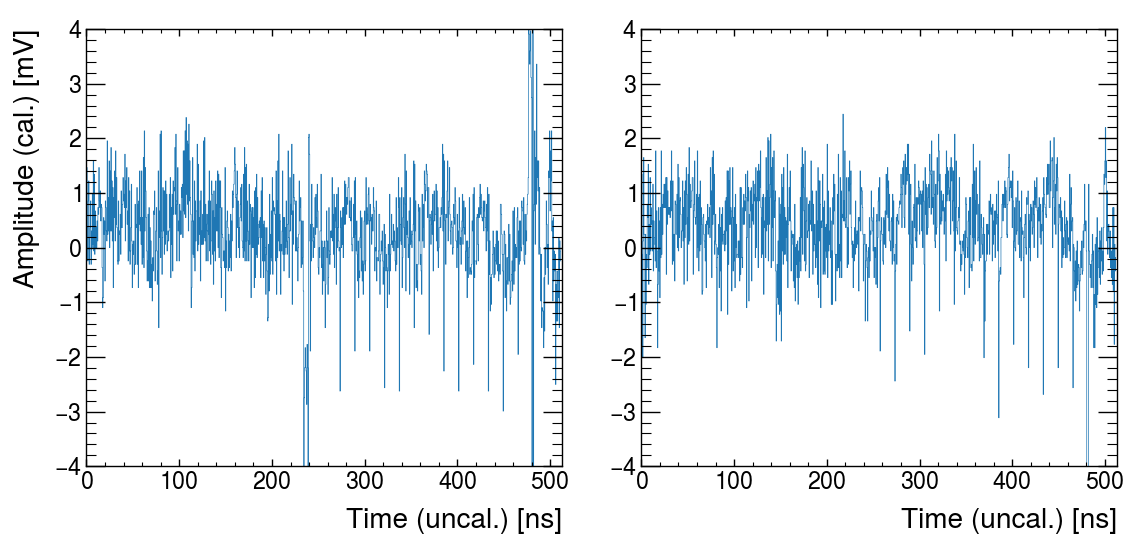

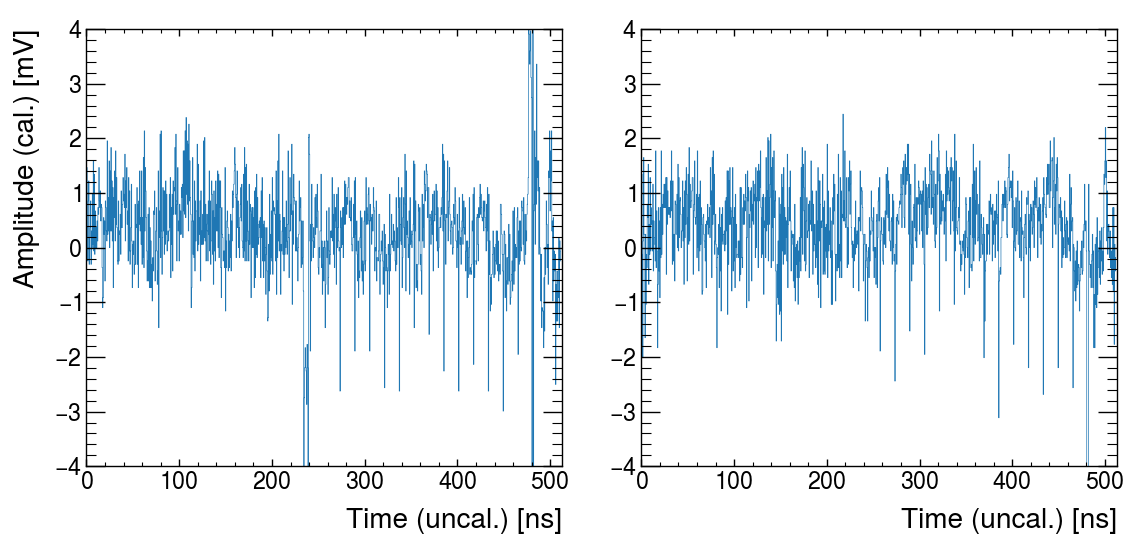

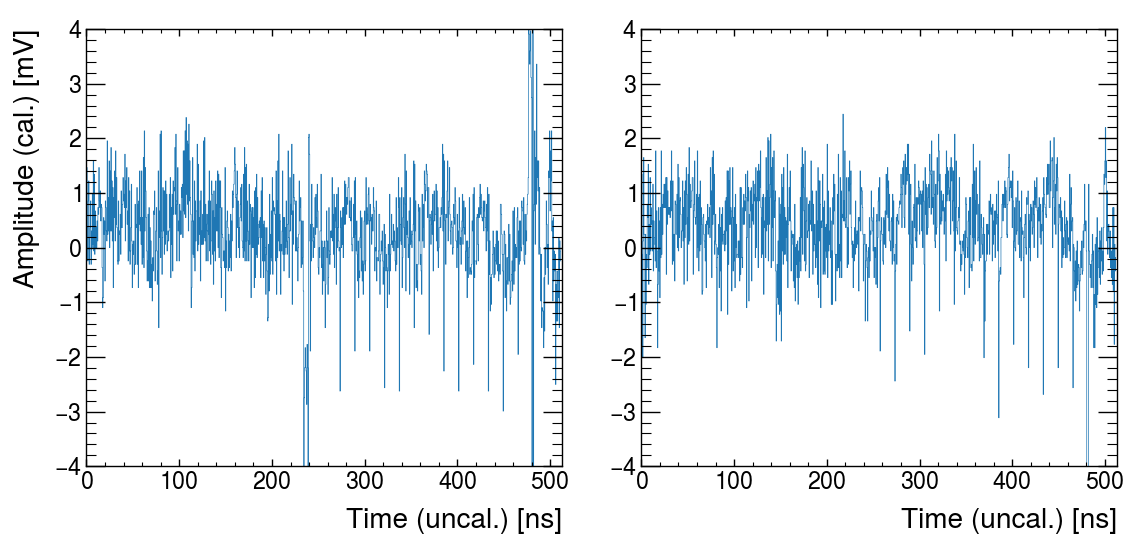

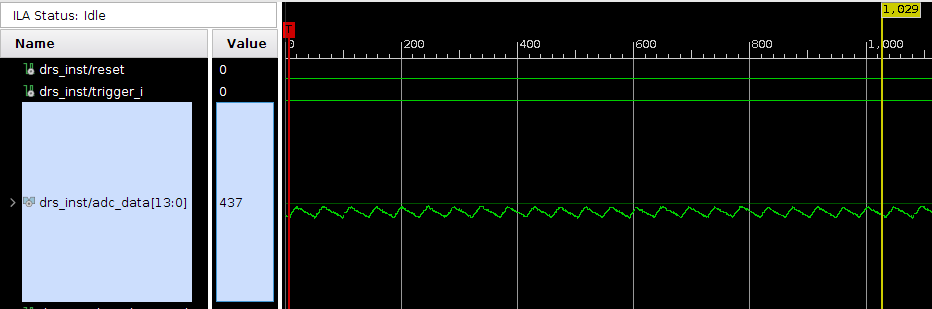

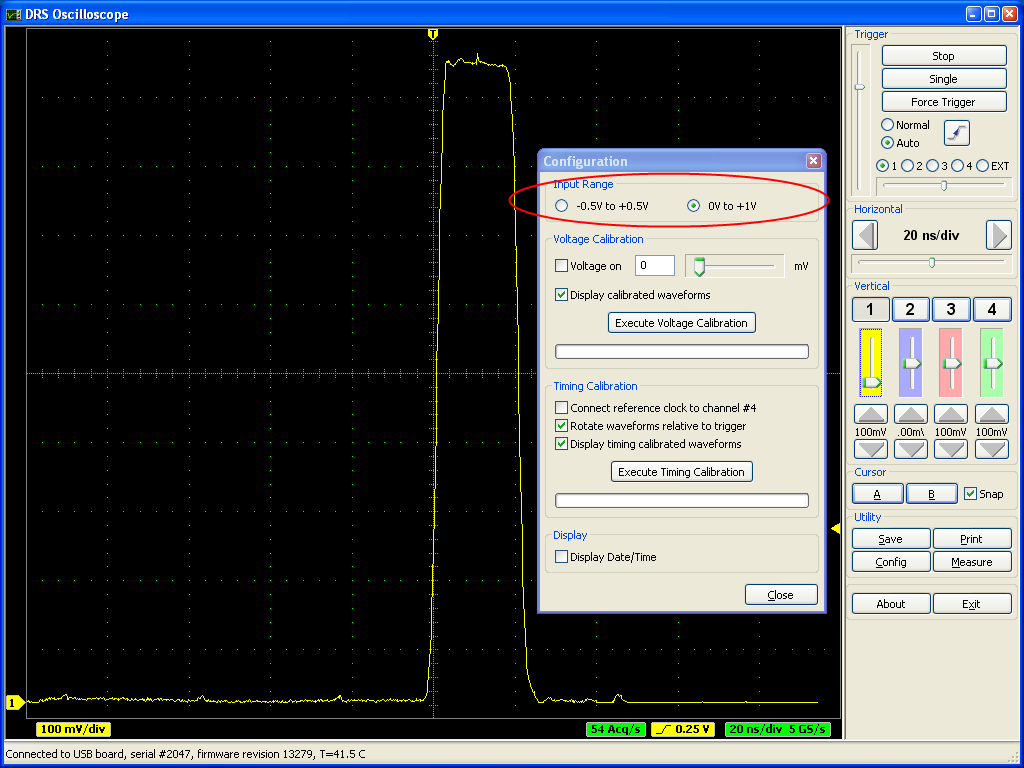

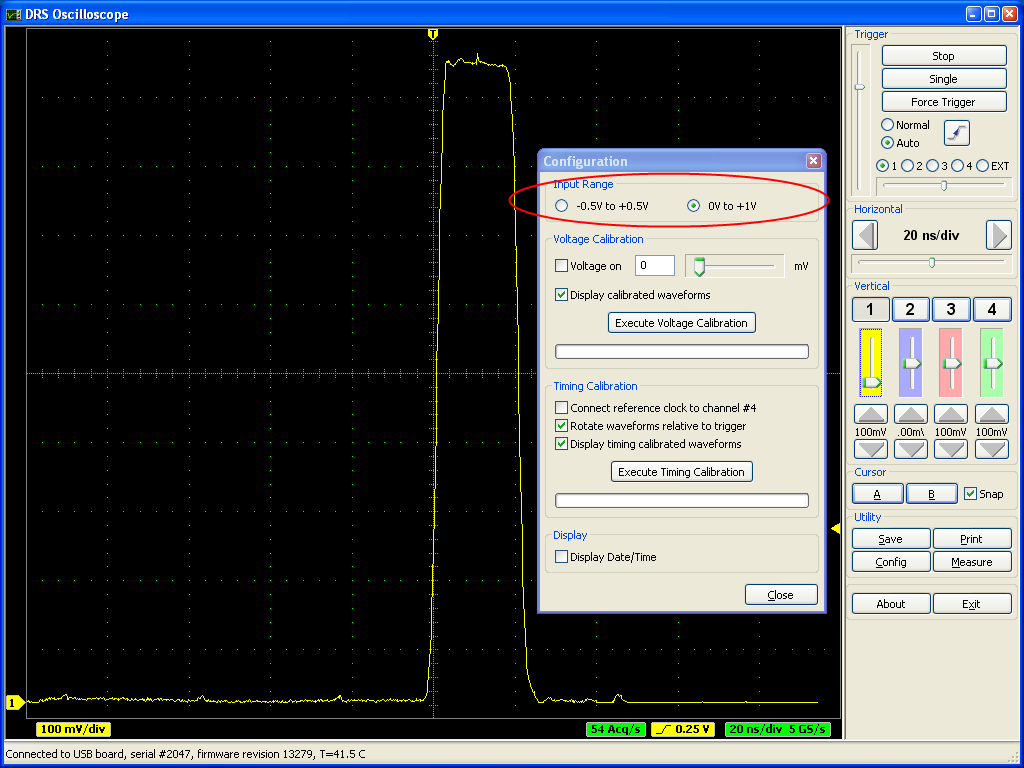

As you all know, the DRS4 chip needs some calibration for each individual cell which corrects the offset and the non-equidistant width in time. While the first evaluation boards have been shipped without this calibration, the current version of the software implements a full amplitude and timing calibration. The offset correction reduces the noise of the board by almost an order of magnitude to below 1 mV RMS. The timing calibration using an on-board reference clock allows a timing accuracy in the order of 10 ps. To illustrate that the following two pictures show a reference clock signal before and after timing calibration:

The integral temporal nonlineairy at 5 GSPS before timing calibration is about 600 ps as can be seen by the jitter of the overlaid waveforms.

In order to do a timing calibration, the firmware revison 13297 or later is required. The current software package 2.1 contains an updated firmware, but unfortunately one needs a Xilinx download cable to flash this new firmware (see http://drs.web.psi.ch/download/ under "Software Versions"). If some people want an update but do not want to buy such a cable, we offer a free update at our institute (just the postage has to be paid). The old evaluation board (Rev. 1.0, plastic housing) can unfortunately not be updated.

After the offset calibration is made, there are small (~20mV) short spikes left. They probably come from some cross-talk between the USB interface and the analog part of the board. This is currently under investigation. If new updates become available, they will be announced in this forum.

April 27th, 2009,

Stefan Ritt |

Tue Jul 7 16:39:57 2009, Stefan Ritt, Power up problem and remedy Tue Jul 7 16:39:57 2009, Stefan Ritt, Power up problem and remedy

|

Maybe some of you have experienced that the DRS4 chip can get pretty hot after power up. After it's initialized the first time, the power consumption goes back to normal. I finally found the cause of this problem and have a remedy. Here is the new paragraph from the updated data sheet:

During power-up, care has to be taken that the DENABLE and DWRITE signals are low. If not, the domino wave can get started before the power supply voltages are stable, which brings the DRS4 chip into a state where it draws a considerable amount of current and heats up significantly. This can be problematic if the signals are directly generated by a FPGA, since most FPGAs have internal pull-up resistors which get activated during the configuration phase of the FPGA. In such a case, the DENABLE and DWRITE signals should be connected to GND with a pull down resistor. This resistor should be much smaller than the FPGA pull-up resistor in order to keep the signals close to GND during the FPGA configuration. A typical value is 4.7 kOhm.

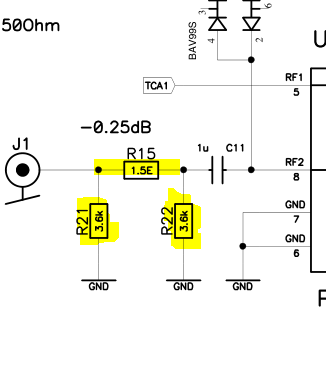

The attached schematics shows the location of the two required resistors. |

Thu Jul 9 09:11:03 2009, Stefan Ritt, Current problems with drs_exam.cpp Thu Jul 9 09:11:03 2009, Stefan Ritt, Current problems with drs_exam.cpp

|

The current version of the DRS readout example program drs_exam.cpp has two problems:

- The sampling frequency cannot be changed, it will always stay in the region around 5 GSPS

- The waveform obtained by GetWave is rotated such that the first DRS cell corresponds to the first array bin

Both problems have been fixed and the fix will be contained in an upcoming software release. |

Tue Oct 6 11:20:39 2009, Stefan Ritt, VDD instability Tue Oct 6 11:20:39 2009, Stefan Ritt, VDD instability

|

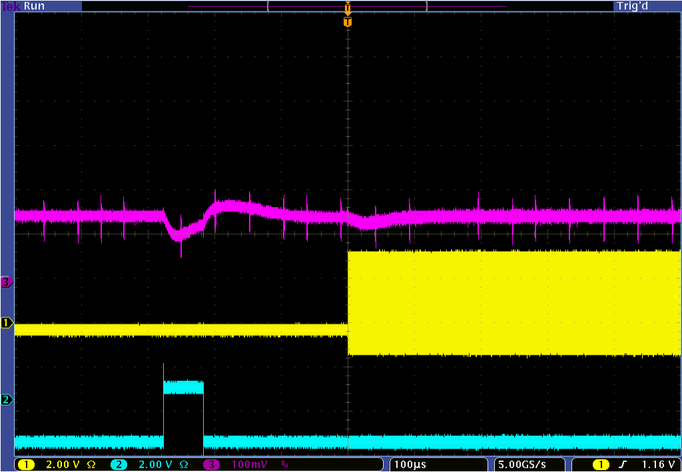

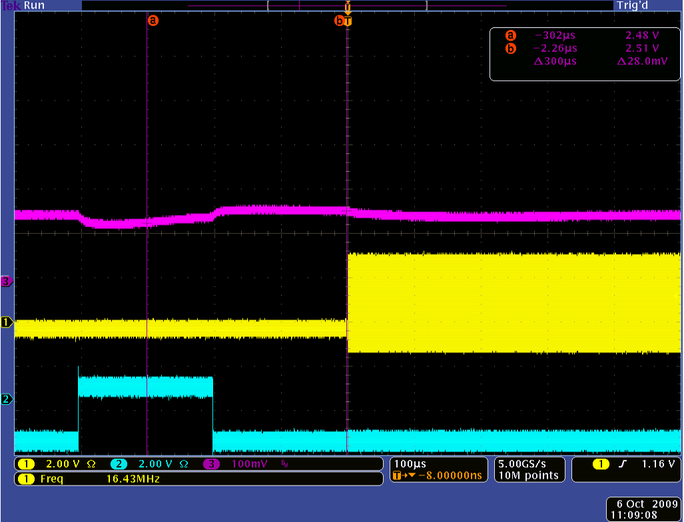

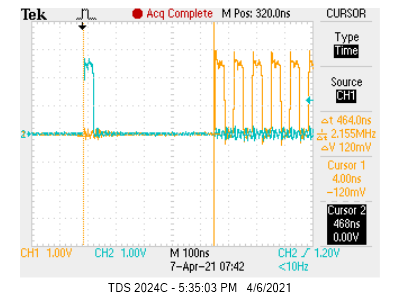

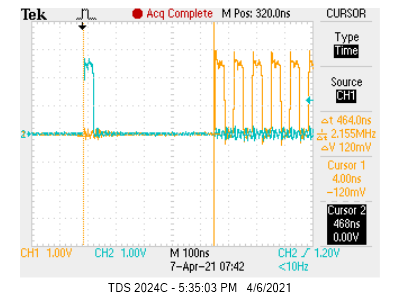

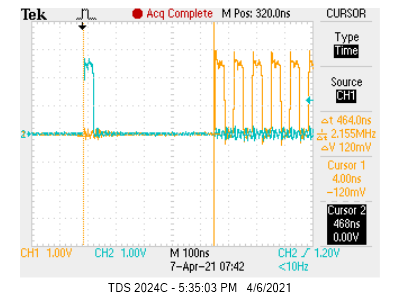

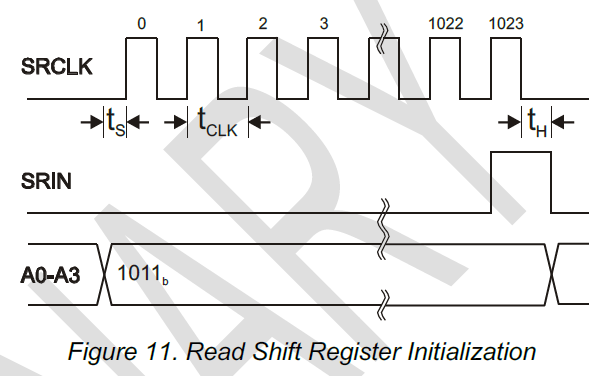

It has turned out that the stability of the AVDD and DVDD power supplies for the DRS4 are very critical. On the evaluation board I use a REG1117-2.5, on our VME board I use a ADP3338-2.5 for the DVDD power supply. When the domino wave is started, the power consumption of the DRS4 chip jumps up by ~40 mA, which has to be compensated by the linear regulator. Following screen shot shows what happens:

The blue trace is the DWRITE signal indicating the sampling phase when high. The yellow is the SRCLK showing when the readout takes place. The pink is now the DVDD power. It can be clearly seen that there is a dip of ~50 mV when the domino wave starts, a positive dip when it stops and another smaller dip when the readout starts. This causes strange effects: If the trigger arrives during the first dip, the actual sampling takes place when the DVDD is ~50 mV smaller, which leads to a baseline shift of a sampled 0V DC input voltage of about the same amount (-50 mV).

The obvious improvement is to put a huge capacitor on the power supply, but that does not help much:

The dip gets a bit smaller, but it's still there. So a better solution would be to use a faster LDO regulator. Please take care of this if you plan a new design.

Furthermore, I believe that the chip internally has some "warmup" phase, where the die heats up a bit when the additional 40 mA are drawn. So a "good" solution is to wait some time after starting the domino wave until one allows for triggers. Tests showed that a few milliseconds are necessary to keep the baseline shifts below a few millivolts. This of course decreases the dead time of the system significantly, so one has to choose the proper balance between increase dead time and increased base line shift. On some applications where a baseline shift is not an issue, one could opt for the minimum dead time. |

Wed Oct 7 17:58:20 2009, Stefan Ritt, VDD switch off speed Wed Oct 7 17:58:20 2009, Stefan Ritt, VDD switch off speed

|

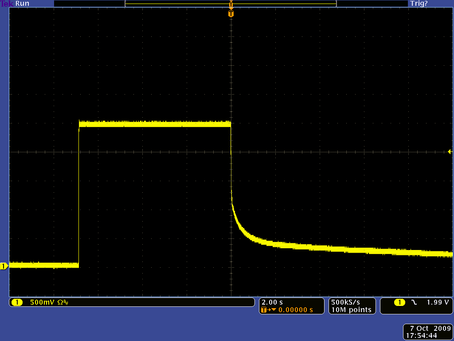

It turned out that the VDD switch off speed plays some important role. On our VME board, we have a linear regulator, then a 4.7 uF capacitor, then the DRS4 chip (DVDD and AVDD). When switching off the VME power, it takes quite some time to discharge the 4.7 uF capacitor, since the DRS4 chip goes into a high impedance mode if VDD < ~1V. This gives following VDD trace:

Rising edge is power on, falling edge is power off. Note the horizontal time scale of 2 s/div. So to get below 0.3 V or so, it takes up to 30 seconds. If the power is switched back on when AVDD is above 0.3V, the DRS4 chip can get into a weird state, where probably many domino waves are started and the chip draws an enormous amount of current. Typically the linear regulator limits the current, so the 2.5V drops to ~1.5V, and the board is not working. If people are aware of this and always wait >30sec. before turning the power on again, this is fine, but people might forget.

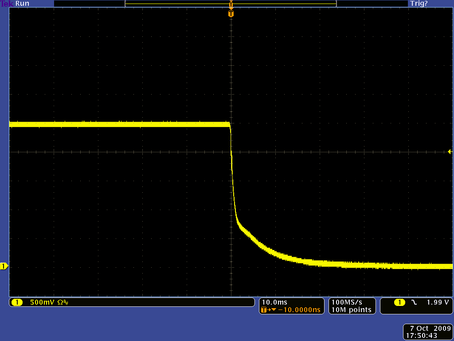

So the solution is to put a resistor (typically 100 Ohm to 1 kOhm) parallel to the 4.7 uF capacitor in order to have some resistive current load of a few mA. The discharge then looks like this:

Note the horizontal scale of 10ms/div. So after 30 ms AVDD is discharged and powering on the chip again does not do any harm. The same should be done to DVDD. |

Wed Oct 14 23:53:05 2009, Armin Kolb, DRS_exam using USB Evaluation Board with OS X Wed Oct 14 23:53:05 2009, Armin Kolb, DRS_exam using USB Evaluation Board with OS X

|

For the users using a Macintosh,

after several hours the Evaluation Board is working on my Macintosh (intel).

1) install the development package with xcode, its on the OS X installation DVD

2) install the libusb binary from http://www.ellert.se/twain-sane/

3) modify the makefile for compiling drs_exam (attached) afterwards it's running perfect!

best,

Armin

|

Fri Oct 16 09:51:03 2009, Jinhong Wang, DSR4 Full Readout Mode Fri Oct 16 09:51:03 2009, Jinhong Wang, DSR4 Full Readout Mode

|

Hello Mr. Stefan Ritt

In DSR4 DATASHEET Rev.0.8 Page13, I noticed you metioned the samping should occur after 38 ns after the rising edge of SRCLK when the multiplexer is used. So what is suggested value(delay time between sampling and the rising edge of SRCLK) for the parallel mode,in which the multiplexer is not used?

Best wishes!

Jinhong Wang |

Fri Oct 16 10:16:10 2009, Stefan Ritt, DSR4 Full Readout Mode Fri Oct 16 10:16:10 2009, Stefan Ritt, DSR4 Full Readout Mode

|

| Jinhong Wang wrote: |

|

Hello Mr. Stefan Ritt

In DSR4 DATASHEET Rev.0.8 Page13, I noticed you metioned the samping should occur after 38 ns after the rising edge of SRCLK when the multiplexer is used. So what is suggested value(delay time between sampling and the rising edge of SRCLK) for the parallel mode,in which the multiplexer is not used?

Best wishes!

Jinhong Wang

|

The clock-to-output delay is the same if one uses the multiplexer or not. I found however that in most cases the delay of 38 ns needs some fine tuning to get optimal performance. So I typically use a shifted clock generated by the FPGA clock manager with a programmable delay (+-5 ns for Xilinx) and optimize this in the running system. |

Mon Oct 19 09:06:43 2009, Jinhong Wang, BIAS Pin of DRS4 Mon Oct 19 09:06:43 2009, Jinhong Wang, BIAS Pin of DRS4

|

Dear Mr. Stefan Ritt.

Thank u for your timely response on "DSR4 Full Readout Mode", I received it from Professor Qi An, who is my PhD supervisor.

I am currently going through the DRS4 datasheet. Well, can you give some specification on the usage of "BIAS" pin of DRS4? It is just metioned in the datasheet as bias of internal buffer. What is the internal buffer exactly reffered to here? The MUXOUT buffer of channel 8 or else? Does it have some relationship to O_OFS? I mean, if the reference voltage to BIAS is changed, how will the output be influenced?

Looking forward to hearing from you soon.

Jinhong Wang

Fast Electronics LAB. of University of Science and Technology of China. |

Mon Oct 19 09:13:00 2009, Stefan Ritt, BIAS Pin of DRS4 Mon Oct 19 09:13:00 2009, Stefan Ritt, BIAS Pin of DRS4

|

| Jinhong Wang wrote: |

|

Dear Mr. Stefan Ritt.

Thank u for your timely response on "DSR4 Full Readout Mode", I received it from Professor Qi An, who is my PhD supervisor.

I am currently going through the DRS4 datasheet. Well, can you give some specification on the usage of "BIAS" pin of DRS4? It is just metioned in the datasheet as bias of internal buffer. What is the internal buffer exactly reffered to here? The MUXOUT buffer of channel 8 or else? Does it have some relationship to O_OFS? I mean, if the reference voltage to BIAS is changed, how will the output be influenced?

Looking forward to hearing from you soon.

Jinhong Wang

Fast Electronics LAB. of University of Science and Technology of China.

|

"internal buffers" are all internal operational amplifiers in the DRS4 chip. Every OPAMP needs a bias (just look it up in any electronics textbook), which determines the linearity and the speed of the OPAMP. When designing DRS4, I was not sure if the required BIAS voltage changes over time, or between chips, so I made it available at a pin, which is a common technique in chip design. But it turns out now that this voltage is not very critical, so just keeping the pin open will work in most cases. |

Mon Oct 19 11:26:29 2009, Jinhong Wang, output common mode voltage of DRS4 Mon Oct 19 11:26:29 2009, Jinhong Wang, output common mode voltage of DRS4

|

Hello Mr. Stifan.Ritt

In the DSR4 datasheet, it is mentioned that there is an additional buffer at each analog output, this buffer shifts the the differential range of -0.5V~0.5V to 0.8V~1.8V. Does it mean that this buffer shifts a voltage of about 1.3V for the primary differential range?

Again for the differential range of -0.5V~0.5V, can the common mode voltage of the analog output at OUT+/OUT- be chaned? In the example presented in the datasheet, OUT+ is 0.8V~1.8V and OUT- is 1.8V~0.8V. So for an output swing of 2V p-p, can the common mode voltage be modified to the desired value? Supposed that the input ranges from -0.5V~0.5V.

Thank you!

Jinhong Wang |

Mon Oct 19 12:46:12 2009, Stefan Ritt, output common mode voltage of DRS4 Mon Oct 19 12:46:12 2009, Stefan Ritt, output common mode voltage of DRS4

|

| Jinhong Wang wrote: |

|

Does it mean that this buffer shifts a voltage of about 1.3V for the primary differential range?

|

No. It shifts about ROFS-0.25V. So only if ROFS=1.55V, the shift will be 1.3V.

| Jinhong Wang wrote: |

|

Again for the differential range of -0.5V~0.5V, can the common mode voltage of the analog output at OUT+/OUT- be chaned?

|

Just read the datasheet under "ANALOG OUTPUTS". I'm sorry if I did not describe this clearly, but the U+ voltage is fixed (only dependent on ROFS), and U- can be calculated using Uofs as written in the datasheet.

| Jinhong Wang wrote: |

|

In the example presented in the datasheet, OUT+ is 0.8V~1.8V and OUT- is 1.8V~0.8V. So for an output swing of 2V p-p, can the common mode voltage be modified to the desired value? Supposed that the input ranges from -0.5V~0.5V.

|

OUT+ is 0.8V~1.8V, OUT- is 2*Uofs-OUT+. So you can only change the OUT- level, not the OUT+ level. |

Fri Oct 30 03:31:54 2009, Jinhong Wang, outline dimension of DRS4 Fri Oct 30 03:31:54 2009, Jinhong Wang, outline dimension of DRS4

|

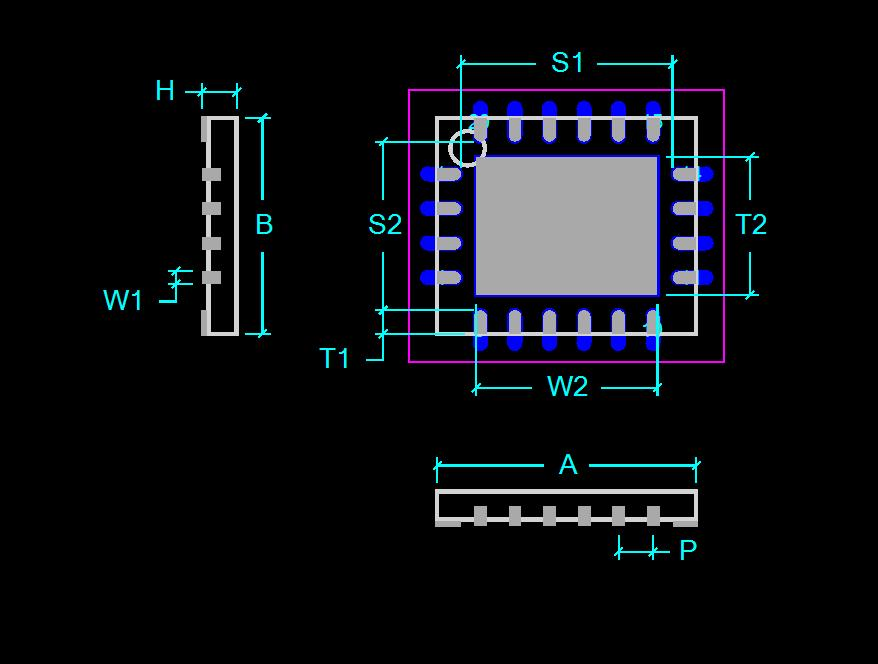

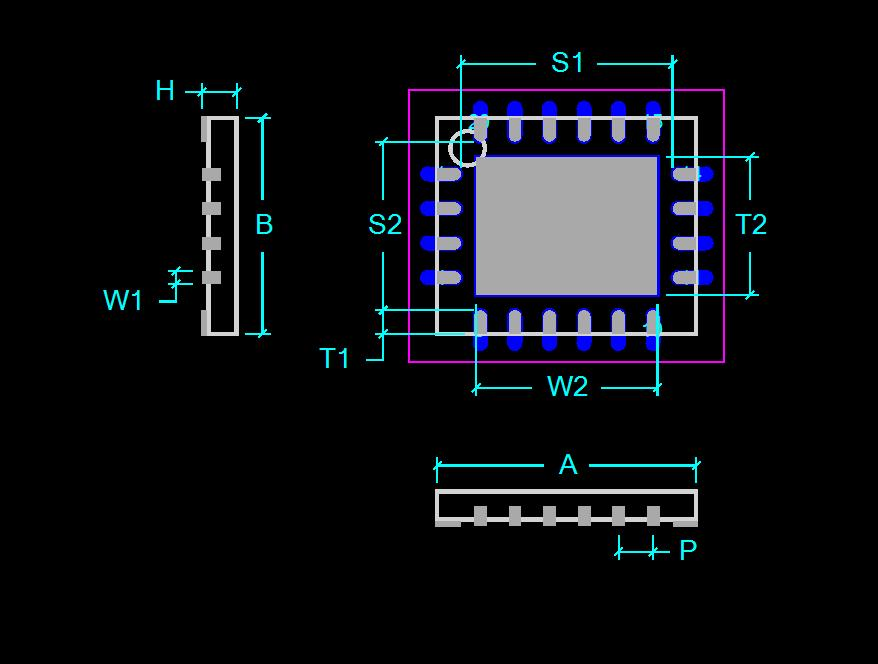

Fig.1 typical dimension of QFN package

Above is the typical dimension specification for QFN package. I cann't find the corresponding "T1" as in Fig.1 in the DRS4 documents, nor any of the tolerance of the dimensions, which are usually expressed in the form of a range between a min. value and a max. value.

So will you specify the dimension of "T1" and "W1", and the dimension tolerance of them?

Thanks and best wishes!

Jinhong Wang University of Science and Technology of China |

Wed Nov 4 14:42:22 2009, Stefan Ritt, outline dimension of DRS4 Wed Nov 4 14:42:22 2009, Stefan Ritt, outline dimension of DRS4

|

| Jinhong Wang wrote: |

|

Fig.1 typical dimension of QFN package

Above is the typical dimension specification for QFN package. I cann't find the corresponding "T1" as in Fig.1 in the DRS4 documents, nor any of the tolerance of the dimensions, which are usually expressed in the form of a range between a min. value and a max. value.

So will you specify the dimension of "T1" and "W1", and the dimension tolerance of them?

Thanks and best wishes!

Jinhong Wang University of Science and Technology of China

|

Please find attached the complete dimensions. |

Mon Dec 14 10:14:16 2009, Jinhong Wang, Trigger of DRS4 Mon Dec 14 10:14:16 2009, Jinhong Wang, Trigger of DRS4

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn) |

Tue Dec 15 14:38:09 2009, Stefan Ritt, Trigger of DRS4 Tue Dec 15 14:38:09 2009, Stefan Ritt, Trigger of DRS4

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

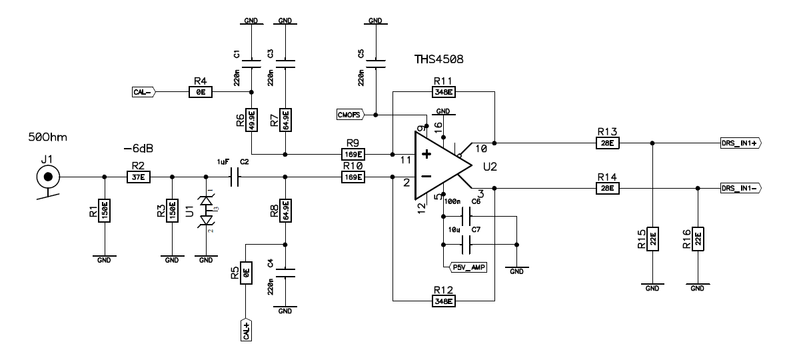

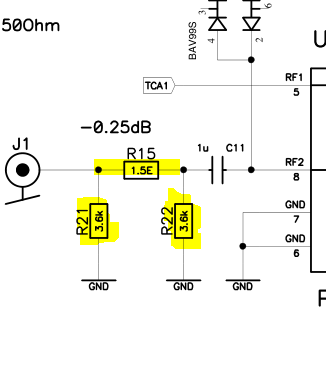

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest. |

Mon Dec 21 10:17:05 2009, Jinhong Wang, Trigger of DRS4 Mon Dec 21 10:17:05 2009, Jinhong Wang, Trigger of DRS4

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn) |

Mon Dec 21 16:52:08 2009, Stefan Ritt, Trigger of DRS4 Mon Dec 21 16:52:08 2009, Stefan Ritt, Trigger of DRS4

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

The amplitude of the analog signal is not degraded by the transparent mode, since the signal is buffered on the chip, and the output of this buffer is send off the chip. The waveform digitizing of course requires quite some current to charge up all capacitors, so there is maximum current of ~1mA for 5 GSPS. If you only have a weak signal source, your bandwidth might be limited by that. On the evaluation board for example we use passive transformers to produce the differential input signal from a single-ended signal. Although the transformers are rated 1 GHz Bandwidth, we only achieve 200 MHz with the passive transformers. By using active high speed differential drivers, you can get about 700 MHz right now.

If you have two channels with 500 ns and 510 ns trigger latency, there is no difference in the "domino stop position" since there is only one domino circuit per chip which can be stopped. So the stop position is the same for all eight channels on a chip. |

Tue Dec 22 01:30:55 2009, Jinhong Wang, Trigger of DRS4 Tue Dec 22 01:30:55 2009, Jinhong Wang, Trigger of DRS4

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

The amplitude of the analog signal is not degraded by the transparent mode, since the signal is buffered on the chip, and the output of this buffer is send off the chip. The waveform digitizing of course requires quite some current to charge up all capacitors, so there is maximum current of ~1mA for 5 GSPS. If you only have a weak signal source, your bandwidth might be limited by that. On the evaluation board for example we use passive transformers to produce the differential input signal from a single-ended signal. Although the transformers are rated 1 GHz Bandwidth, we only achieve 200 MHz with the passive transformers. By using active high speed differential drivers, you can get about 700 MHz right now.

If you have two channels with 500 ns and 510 ns trigger latency, there is no difference in the "domino stop position" since there is only one domino circuit per chip which can be stopped. So the stop position is the same for all eight channels on a chip.

|

So you mean there is an analog buffer per channel? The analog signal is buffered there, before entering the sampling cells? Then, when will the buffer content be released and cleared? How shall I handle "Dwite" and "Denable" during a complete operation when an analog signal arrives in the transparent mode? I cannot find more information beyond the datasheet, a detailed description of the transparent mode (and the analog buffer, if possible) will be really helpful for me.

Best,

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn) |

Tue Dec 22 09:07:27 2009, Stefan Ritt, Trigger of DRS4 Tue Dec 22 09:07:27 2009, Stefan Ritt, Trigger of DRS4

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

| Stefan Ritt wrote: |

|

| Jinhong Wang wrote: |

|

Dear Mr. S. Ritt

The following is my confusion about the trigger of DRS4. It mainly concertrates on the generation of trigger signal to stop DRS4 sampling process for readout of sampled waveform.

As metioned in the datasheet of DRS4, the chip samples the analog input every domino sampling period. After finished sampling a waveform, the sampling process can be stoped by lowering the DWRITE while keeping DENABLE high. But the analog input is asychronous to the Domino CLK. Then, how can we know when to stop the domino sampling process to read out the sampled waveform? Of course, a trigger can be used. But from my present knowledge of DRS4, trigger can only be generated from analog input. Analog input is splited into two channels, one to DRS4 analog input, the other to FPGA as the trigger. However, splitting analog inputs increases the system design complexity, and may lower the total performace. So what is your suggestion?

In our system, there are 8 analog inputs to a signal DRS4 chip, the outputs of DRS4 chip are connected to an 8-channel 14 bit ADC ( AD9252). It wold be kind of you to inform me about the most applicable approach for readout of DRS4 sampled wavefrom.

Best regards.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

Indeed you have to make an external trigger. The evaluation board uses the "transparent mode" of the DRS4 to "mirror" the input signal at the output, then puts a comparator there. The schematics of the evaluation board is in the manual. This does then not degrate the analog performance. You can of course also split the signal at the input, this will only add a minor additional load to the input signal, since the load of the DRS4 chips itself is much bigger than that of any comparator.

An alternative is to turn on the transparent mode and continuously digitize all 8 outputs with your AD9252. Then you make the trigger purely digital in your FPGA. You can put there a comparator, or even more complex logic like multiplicity etc. Note however that this causes some latency, since the ADC has a pipeline which is quite long, so you have to buffer the latency of your trigger in the analog window of the DRS4 sampling cells. Like if you run the DRS4 at 1 GSPS, you can accomodate 1024 ns of sampling depth, which is good for maybe 500 ns of trigger latency plus 500 ns of the waveform of interest.

|

Thank you. The transparent mode can be really helpful. Can you provide me in more details of the chip's transparent mode? I am still confused about the following aspects.

I notice that DRS4 samples the analog wave in the way "clear before write", and in the transparent mode, there will be certain delay before the trigger logic stops the sampling process. So,does it mean that the waveform recording process per Domino sampling cycle will not degrade the amplitude of the analog signal? Hence, for two idential analog inputs, one with a trigger latency of 500 ns and the other of 510 ns, the sampled waveform is identical, what differs is the starting number of the first active sampling cell, where the reading process considered to be started. Is that right? Looking forward to your insight.

Best regrads.

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

The amplitude of the analog signal is not degraded by the transparent mode, since the signal is buffered on the chip, and the output of this buffer is send off the chip. The waveform digitizing of course requires quite some current to charge up all capacitors, so there is maximum current of ~1mA for 5 GSPS. If you only have a weak signal source, your bandwidth might be limited by that. On the evaluation board for example we use passive transformers to produce the differential input signal from a single-ended signal. Although the transformers are rated 1 GHz Bandwidth, we only achieve 200 MHz with the passive transformers. By using active high speed differential drivers, you can get about 700 MHz right now.

If you have two channels with 500 ns and 510 ns trigger latency, there is no difference in the "domino stop position" since there is only one domino circuit per chip which can be stopped. So the stop position is the same for all eight channels on a chip.

|

So you mean there is an analog buffer per channel? The analog signal is buffered there, before entering the sampling cells? Then, when will the buffer content be released and cleared? How shall I handle "Dwite" and "Denable" during a complete operation when an analog signal arrives in the transparent mode? I cannot find more information beyond the datasheet, a detailed description of the transparent mode (and the analog buffer, if possible) will be really helpful for me.

Best,

Sincerely,

Jinhong Wang (wangjinh@mail.ustc.edu.cn)

|

There is one analog buffer per channel at the output, as indicated on the FUNCTIONAL BLOCK DIAGRAM of the datasheet. The section ANALOG INPUTS clearly states that the input signal has to load directly the sampling capacitors.

All other people using the chip so far correctly understood these things so far, so I believe more information beyond the datasheet is not necessary. I believe you have a principal problem of understanding, which can hardly be clarified by email. Best would be if you directly call me, I can then explain things to you. |

Wed Dec 30 14:28:33 2009, aliyilmaz, normal_mode_in_drs_exam.cpp Wed Dec 30 14:28:33 2009, aliyilmaz, normal_mode_in_drs_exam.cpp

|

Dear Mr. S. Ritt

i am Ms. student , am working with your DRS4 board to calculate the time of flight of the cosmic particle which passes trough the hodoscope . i see the signals at scope , which is negative (i don't want to take positive side of the signal).

i am using your drs_exap.cpp file to take the data, i set the analog trigger source , threshold level is negative, like this(b->SetTriggerLevel(-30, true) ); but the exam file also registers the positive side of signal (i think that is spike or internal reflection), is it possible to eliminate this spike? Also i want to register the data just after the threshold value, but that is always triggered, i think that caused from the mode. Is it possible to set the trigger mode to normal in exam file?,and how can i do that?

Best regards.

Sincerely,

Ali YILMAZ (ali.yilmaz@roma1.infn.it)

|

Mon Jan 11 16:32:21 2010, Stefan Ritt, normal_mode_in_drs_exam.cpp Mon Jan 11 16:32:21 2010, Stefan Ritt, normal_mode_in_drs_exam.cpp

|

| aliyilmaz wrote: |

|

Dear Mr. S. Ritt

i am Ms. student , am working with your DRS4 board to calculate the time of flight of the cosmic particle which passes trough the hodoscope . i see the signals at scope , which is negative (i don't want to take positive side of the signal).

i am using your drs_exap.cpp file to take the data, i set the analog trigger source , threshold level is negative, like this(b->SetTriggerLevel(-30, true) ); but the exam file also registers the positive side of signal (i think that is spike or internal reflection), is it possible to eliminate this spike? Also i want to register the data just after the threshold value, but that is always triggered, i think that caused from the mode. Is it possible to set the trigger mode to normal in exam file?,and how can i do that?

Best regards.

Sincerely,

Ali YILMAZ (ali.yilmaz@roma1.infn.it)

|

Please note that SetTriggerLevel(level, polarity) needs "level" in volts, not millivolts, so you need SetTriggerLevel(-0.3, true). The trigger mode is not specified with any library call, but depends on what your program does. If you always poll on IsBusy(), then you are already in "normal" mode. The auto mode can only be achieved on the user application level by doing an "artifical" trigger by calling SoftTrigger() if there are no hardware triggers for a certain time. |

Sun Jan 31 23:52:15 2010, Hao Huan, Failure In Flashing Xilinx PROM Sun Jan 31 23:52:15 2010, Hao Huan, Failure In Flashing Xilinx PROM

|

Hi Stefan,

I have an old-version DRS4 evaluation board which doesn't have the latest firmware. I tried to flash the drs_eval1.ipf boundary scan chain into the XCF02S PROM with Xilinx IMPACT, and the firmware seemed to go through into the PROM. However, when I started the DRS command line interface to test the firmware it kept on reporting errors like

musb_write: requested 10, wrote -116, errno 0 (No error)

musb_read error -116

musb_write: requested 10, wrote -22, error 0 (No error)

musb_read error -116

and so on. Finally the program made a dumb recognition of the board as

Found mezz. board 0 on USB, serial #0, firmware revision 0

Do you have any idea which caused this problem? Thanks! |

Mon Feb 1 08:30:42 2010, Stefan Ritt, Failure In Flashing Xilinx PROM Mon Feb 1 08:30:42 2010, Stefan Ritt, Failure In Flashing Xilinx PROM

|

| Hao Huan wrote: |

|

Hi Stefan,

I have an old-version DRS4 evaluation board which doesn't have the latest firmware. I tried to flash the drs_eval1.ipf boundary scan chain into the XCF02S PROM with Xilinx IMPACT, and the firmware seemed to go through into the PROM. However, when I started the DRS command line interface to test the firmware it kept on reporting errors like

musb_write: requested 10, wrote -116, errno 0 (No error)

musb_read error -116

musb_write: requested 10, wrote -22, error 0 (No error)

musb_read error -116

and so on. Finally the program made a dumb recognition of the board as

Found mezz. board 0 on USB, serial #0, firmware revision 0

Do you have any idea which caused this problem? Thanks!

|

A firmware update requires a power cycle of the evaluation board. Have you tried that? I attached for you reference the current drs_eval1.mcs file, which is meant to go into the XCF02S PROM. There were recent changes also in the DRS library, and I'm not sure if yous if recent enough. So I put also the current C files which go with the firmware. They contain also some improvements which should reduce the intrinsic noise of the board. |

Wed Feb 10 02:57:55 2010, pepe sanchez lopez, Hello Wed Feb 10 02:57:55 2010, pepe sanchez lopez, Hello

|

hello i am an student and i want to do my final project with drs4 board and i really can´t find how to open waveform file and how can i save or opened many of them quickly.

if you can tell me how i will be very grateful.

thanks,

kind regards. |

Wed Feb 10 15:35:09 2010, Stefan Ritt, Hello Wed Feb 10 15:35:09 2010, Stefan Ritt, Hello

|

| pepe sanchez lopez wrote: |

|

hello i am an student and i want to do my final project with drs4 board and i really can´t find how to open waveform file and how can i save or opened many of them quickly.

if you can tell me how i will be very grateful.

thanks,

kind regards.

|

There is no built-in possibility to open waveform files, you have to write your own programs to do that. |

Mon Feb 15 19:43:34 2010, Ron Grazioso, Problem reading oscilloscope binary waveform output Mon Feb 15 19:43:34 2010, Ron Grazioso, Problem reading oscilloscope binary waveform output

|

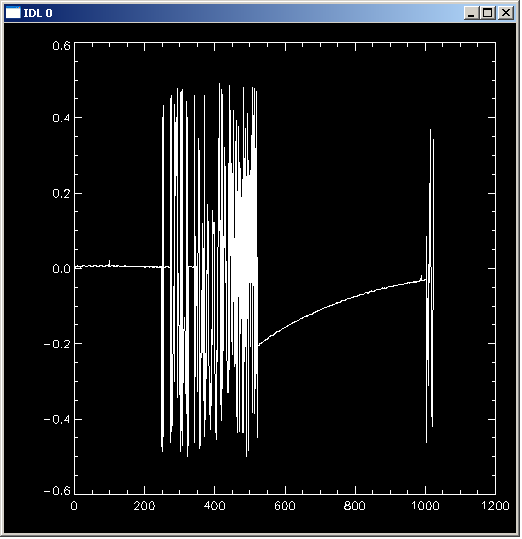

I have saved some waveforms using the oscilloscope application in both binary and xml. I can see that the xml file gives me proper data values but when I try to read the binary file using IDL, it does not seem correct. This is a screen shot of the pulse I saved:

But when I open the binary file in IDL using:

data = uintarr(1024) ;unsigned integer array

readu,lun1,data

free_lun,lun1

close,lun1

;Convert bits to Volts

data=data*0.000015259-0.5

window,0,xs=512,ys=512

plot,data[*]

I get: I get:

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

Thanks, Ron

|

Tue Feb 16 09:38:59 2010, Stefan Ritt, Problem reading oscilloscope binary waveform output Tue Feb 16 09:38:59 2010, Stefan Ritt, Problem reading oscilloscope binary waveform output

|

| Ron Grazioso wrote: |

|

It looks like the pulse is there but there is something corrupting the data only in binary form. Is there a setting that may not be correct?

|

Yes, but you have to recompile the oscilloscope application. Find following line in the source file DOFrame.cpp:

m_WFfd = open(filename.char_str(), O_RDWR | O_CREAT | O_TRUNC | O_TEXT, 0644);

and replace it with

m_WFfd = open(filename.char_str(), O_RDWR | O_CREAT | O_TRUNC | O_BINARY, 0644);

that fixes the problem. To compile the program, you need MS Visual C++ and you have to install the vxWidgets library. Let me know if you have any problem with that.

Anyhow I plan a major software update soon (weeks), which not only fixes this problem, but also reduces the noise considerably by doing a kind of two-fold calibration.

- Stefan |

Sun Feb 21 13:41:35 2010, Stefan Ritt, Real Time Conference 2010 Sun Feb 21 13:41:35 2010, Stefan Ritt, Real Time Conference 2010

|

Hello,

may I draw your attention to the upcoming Real Time Conference 2010, taking place in Lisbon, Portugal, May 23rd to May 28th, 2010.

http://rt2010.ipfn.ist.utl.pt/

Several groups which are developing DRS4 electronics will come to this conference and present their work, so it will be a good opportunity to exchange ideas and experiences. There will also be a short course on digital pulse shape processing, which is highly relevant for our field.

Looking forward to see you in Lisbon,

Stefan |

Sat Feb 20 01:56:05 2010, Hao Huan, PLLLCK signal of DRS4 Sat Feb 20 01:56:05 2010, Hao Huan, PLLLCK signal of DRS4

|

Hi Stefan,

in the latest DRS4 datasheet I only saw your data of the DRS4 PLL locking time for 6GSPS sampling speed, with other rows "TBD". Have you tried those lower frequencies? According to the datasheet I think the PLLLCK should be stabily low when the PLL is locked; am I right? However when I try my design with the DRS4 chip and feed the reference clock signal at 0.5MHz or 2MHz, the PLLLCK I get can never stabilize. There could be some problem in the PCB circuit connection, but I want to confirm with you since I'm confused with those "TBD" blanks.

Thanks a lot!

|

Sat Feb 20 09:54:48 2010, Stefan Ritt, PLLLCK signal of DRS4 Sat Feb 20 09:54:48 2010, Stefan Ritt, PLLLCK signal of DRS4

|

| Hao Huan wrote: |

|

Hi Stefan,

in the latest DRS4 datasheet I only saw your data of the DRS4 PLL locking time for 6GSPS sampling speed, with other rows "TBD". Have you tried those lower frequencies? According to the datasheet I think the PLLLCK should be stabily low when the PLL is locked; am I right? However when I try my design with the DRS4 chip and feed the reference clock signal at 0.5MHz or 2MHz, the PLLLCK I get can never stabilize. There could be some problem in the PCB circuit connection, but I want to confirm with you since I'm confused with those "TBD" blanks.

Thanks a lot!

|

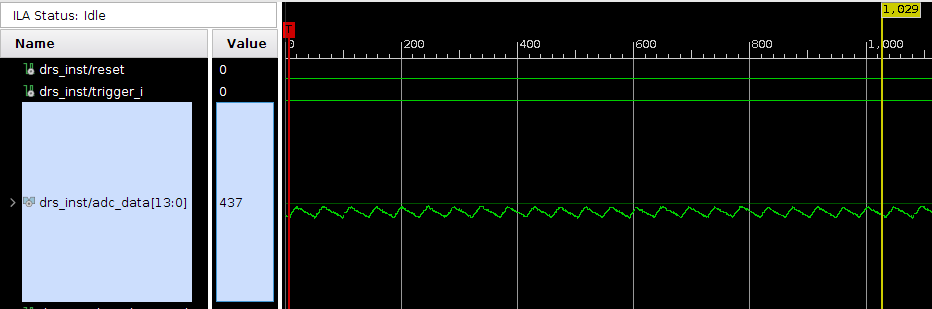

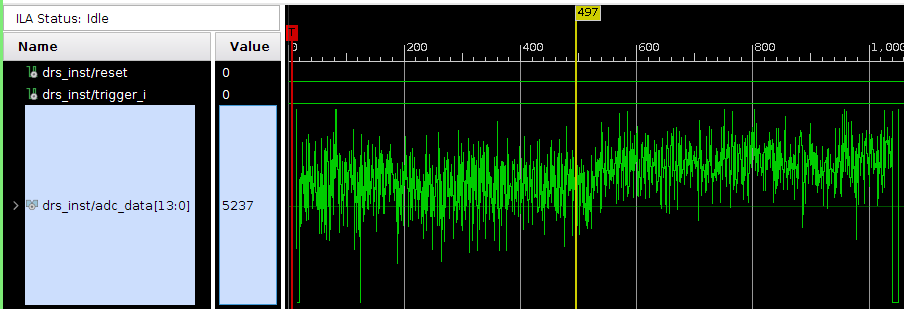

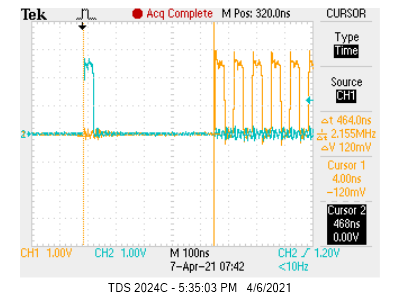

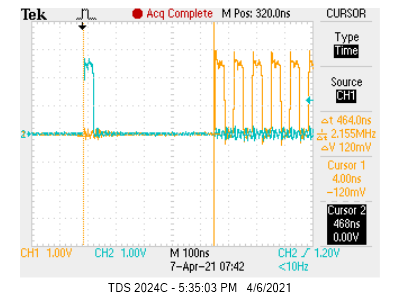

The locking time is typically 20-30 cycles of the external reference clock, I will update the numbers in the datasheet soon. I attached a screenshot of the chip when starting up at 1 GHz (0.5 MHz REFCLK), so you can see the behaviour. The upper curver is the DTAP signal, the lower curve the PLLLCK signal. As you can see, the PLLLCK signal is not purely digital. Actually it's a simple XOR between the REFCLK and the DTAP signal, so you need an external 4.7nF capacitor to "integrate" this signal. Without this capacitor, you would see small negative spikes whenever there is s small phase shift between the DTAP and the REFCLK signal. Have a look at your DTAP signal, is it in phase with the REFCLK? |

Sun Feb 21 00:46:01 2010, Hao Huan, PLLLCK signal of DRS4 Sun Feb 21 00:46:01 2010, Hao Huan, PLLLCK signal of DRS4

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Hi Stefan,

in the latest DRS4 datasheet I only saw your data of the DRS4 PLL locking time for 6GSPS sampling speed, with other rows "TBD". Have you tried those lower frequencies? According to the datasheet I think the PLLLCK should be stabily low when the PLL is locked; am I right? However when I try my design with the DRS4 chip and feed the reference clock signal at 0.5MHz or 2MHz, the PLLLCK I get can never stabilize. There could be some problem in the PCB circuit connection, but I want to confirm with you since I'm confused with those "TBD" blanks.

Thanks a lot!

|

The locking time is typically 20-30 cycles of the external reference clock, I will update the numbers in the datasheet soon. I attached a screenshot of the chip when starting up at 1 GHz (0.5 MHz REFCLK), so you can see the behaviour. The upper curver is the DTAP signal, the lower curve the PLLLCK signal. As you can see, the PLLLCK signal is not purely digital. Actually it's a simple XOR between the REFCLK and the DTAP signal, so you need an external 4.7nF capacitor to "integrate" this signal. Without this capacitor, you would see small negative spikes whenever there is s small phase shift between the DTAP and the REFCLK signal. Have a look at your DTAP signal, is it in phase with the REFCLK?

|

Thanks! I see. The capacitor is important. However I'm a little confused... If PLLLCK=DTAP XOR REFCLK, shouldn't it integrate to low instead of high when the two clocks are in phase? I must have some misunderstanding here. So if we ignore any realistic complexity and assume DTAP is perfectly locked with REFCLK, will PLLLCK be always low or high? I'm sorry I do not know how the DRS internal PLL and its input/output work... |

Sun Feb 21 13:47:03 2010, Stefan Ritt, PLLLCK signal of DRS4 Sun Feb 21 13:47:03 2010, Stefan Ritt, PLLLCK signal of DRS4

|

| Hao Huan wrote: |

|

Thanks! I see. The capacitor is important. However I'm a little confused... If PLLLCK=DTAP XOR REFCLK, shouldn't it integrate to low instead of high when the two clocks are in phase? I must have some misunderstanding here. So if we ignore any realistic complexity and assume DTAP is perfectly locked with REFCLK, will PLLLCK be always low or high? I'm sorry I do not know how the DRS internal PLL and its input/output work...

|

Actually the XOR is followed by an inverter, so it will integrate to high if the two clocks are in phase. |

Sun Feb 21 20:27:46 2010, Hao Huan, PLLLCK signal of DRS4 Sun Feb 21 20:27:46 2010, Hao Huan, PLLLCK signal of DRS4

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

Thanks! I see. The capacitor is important. However I'm a little confused... If PLLLCK=DTAP XOR REFCLK, shouldn't it integrate to low instead of high when the two clocks are in phase? I must have some misunderstanding here. So if we ignore any realistic complexity and assume DTAP is perfectly locked with REFCLK, will PLLLCK be always low or high? I'm sorry I do not know how the DRS internal PLL and its input/output work...

|

Actually the XOR is followed by an inverter, so it will integrate to high if the two clocks are in phase.

|

Got it. Thank you! By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior? |

Sun Feb 21 20:33:57 2010, Stefan Ritt, PLLLCK signal of DRS4 Sun Feb 21 20:33:57 2010, Stefan Ritt, PLLLCK signal of DRS4

|

| Hao Huan wrote: |

|

By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior?

|

If the WSRin is fed internally to WSROUT, then the level of the WSRIN pin does not matter, it's just disconnected. You can leave the pin open without problem. WSROUT is however active, so you can observe the internal state of the write shift register. In the default configuration (8x1024 sampling cells), all 8 channels are active all the time, so the WSR is loaded with ones. The inverter at the output then makes all zeros from this. If you configure the chip as 4x2048 cells, then you will observe switching bits at WSROUT. |

Mon Feb 22 17:23:59 2010, Hao Huan, PLLLCK signal of DRS4 Mon Feb 22 17:23:59 2010, Hao Huan, PLLLCK signal of DRS4

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior?

|

If the WSRin is fed internally to WSROUT, then the level of the WSRIN pin does not matter, it's just disconnected. You can leave the pin open without problem. WSROUT is however active, so you can observe the internal state of the write shift register. In the default configuration (8x1024 sampling cells), all 8 channels are active all the time, so the WSR is loaded with ones. The inverter at the output then makes all zeros from this. If you configure the chip as 4x2048 cells, then you will observe switching bits at WSROUT.

|

Sorry; WSROUT also has an inverter? Actually I have one more stupid question about the shift registers: when we assert the address bits to operate on one shift register, e.g. WSR, we use SRIN to give input and SROUT to read output; but how does the shift register know whether we're reading or writing? Or it will just receive input from SRIN and give output at SROUT at the same time?

Thank you so much! |

Wed Mar 3 14:37:40 2010, Stefan Ritt, PLLLCK signal of DRS4 Wed Mar 3 14:37:40 2010, Stefan Ritt, PLLLCK signal of DRS4

|

| Hao Huan wrote: |

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

By the way I have another question: when the default operation mode of the DRS4 chip is used, i.e. WSRIN is fed internally to WSROUT, at the external pins is it necessary to leave the WSRIN open? Or any input through the pin will not affect the Domino wave running? Also I observe that WSROUT will be always low when the chip is running in this mode; is it the supposed behavior?

|

If the WSRin is fed internally to WSROUT, then the level of the WSRIN pin does not matter, it's just disconnected. You can leave the pin open without problem. WSROUT is however active, so you can observe the internal state of the write shift register. In the default configuration (8x1024 sampling cells), all 8 channels are active all the time, so the WSR is loaded with ones. The inverter at the output then makes all zeros from this. If you configure the chip as 4x2048 cells, then you will observe switching bits at WSROUT.

|

Sorry; WSROUT also has an inverter? Actually I have one more stupid question about the shift registers: when we assert the address bits to operate on one shift register, e.g. WSR, we use SRIN to give input and SROUT to read output; but how does the shift register know whether we're reading or writing? Or it will just receive input from SRIN and give output at SROUT at the same time?

|

Actually I double checked the schematics, WSROUT has NO inverter at the output. So the output should be always one in a 8x1024 channel configuration.

Concerning the read/write you are right. On each clock cycle, SRIN will be shifted into the first bit, and the last bit will be visible at SROUT. |

Wed Mar 3 17:36:31 2010, Hao Huan, Initialization of the Domino Circuit Wed Mar 3 17:36:31 2010, Hao Huan, Initialization of the Domino Circuit

|

Hi Stefan,

I read in the datasheet that every time after power up the Domino wave in DRS4 needs to be started and stopped once to initialize the Domino circuit. However in your firmware it seems the chip immediately goes into the idle state after reset. Is that Domino circuit initialization really necessary?

Also an aside question: in your firmware the readout process has the SRCLK sent to DRS4 only about 200ns later after RSRLOAD gets asserted instead of immediately following RSRLOAD. Is there any reason for that?

Thanks a lot!

|

Wed Mar 3 17:49:30 2010, Stefan Ritt, Initialization of the Domino Circuit Wed Mar 3 17:49:30 2010, Stefan Ritt, Initialization of the Domino Circuit

|

| Hao Huan wrote: |

|

Hi Stefan,

I read in the datasheet that every time after power up the Domino wave in DRS4 needs to be started and stopped once to initialize the Domino circuit. However in your firmware it seems the chip immediately goes into the idle state after reset. Is that Domino circuit initialization really necessary?

Also an aside question: in your firmware the readout process has the SRCLK sent to DRS4 only about 200ns later after RSRLOAD gets asserted instead of immediately following RSRLOAD. Is there any reason for that?

Thanks a lot!

|

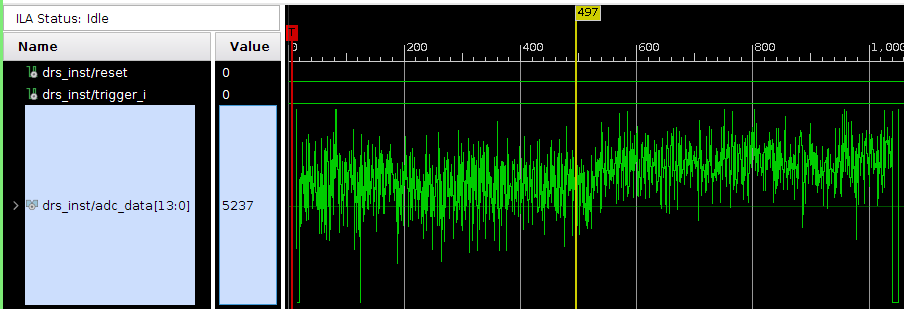

The start/stop requirement is obsolete and has been replaced by elog:10. I need to update this in the datasheet. The delay between the RSRLOAD and the SRCLK has the following reason: On the RSRLOAD the first sampling cell is output to the chip and to the ADC. This can sometimes be a rather high swing, which needs some time to settle, and some warm-up for the output driver. But actually I never really measured it, so it's there just as a safety margin. But I would encourage you to try to reduce this time and see it the first few bins of the readout change in offset. |

Thu Mar 4 19:14:10 2010, Hao Huan, Readout of DRS Data Thu Mar 4 19:14:10 2010, Hao Huan, Readout of DRS Data

|

Hi Stefan,

thanks to your help I can now successfully keep the Domino wave running at a stable frequency and maintain the channel cascading information in the Write Shift Register. (Since you told me WSR always reads and writes at the same time, I think I need to rewrite the information back every time after reading out from WSR to decide from which channel my data come, don't I?)

However I'm still having difficulty in reading out from the DRS cells. I use the ROI readout mode and assume as long as I give a pulse on RSRLOAD the data will come out one by one. However, what I get is just a constant with some noise, which seems I'm always reading from the same cell. Actually I'm not very clear about how it works. What's the mechanism for RSRLOAD and do I have to initialize the Read Shift Register to use the ROI mode? Also I read in the datasheet that WSROUT will give RSR output when DWRITE is low. Sometimes I see some random bits from this output and sometimes I see all zero's. What is the reasonable output I should see from WSROUT, say, when I'm running in the transparent mode with DWRITE low?

Thank you very much!

|

Fri Mar 5 23:29:04 2010, Hao Huan, Readout of DRS Data Fri Mar 5 23:29:04 2010, Hao Huan, Readout of DRS Data

|

| Hao Huan wrote: |

|

Hi Stefan,

thanks to your help I can now successfully keep the Domino wave running at a stable frequency and maintain the channel cascading information in the Write Shift Register. (Since you told me WSR always reads and writes at the same time, I think I need to rewrite the information back every time after reading out from WSR to decide from which channel my data come, don't I?)

However I'm still having difficulty in reading out from the DRS cells. I use the ROI readout mode and assume as long as I give a pulse on RSRLOAD the data will come out one by one. However, what I get is just a constant with some noise, which seems I'm always reading from the same cell. Actually I'm not very clear about how it works. What's the mechanism for RSRLOAD and do I have to initialize the Read Shift Register to use the ROI mode? Also I read in the datasheet that WSROUT will give RSR output when DWRITE is low. Sometimes I see some random bits from this output and sometimes I see all zero's. What is the reasonable output I should see from WSROUT, say, when I'm running in the transparent mode with DWRITE low?

Thank you very much!

|

Hi Stefan,

I tried again and confirmed the problem... In the full readout mode I could successfully read out all the data, but in the ROI mode if I naively apply a pulse at RSRLOAD the results are not right. Is there anything I should be careful about in the ROI readout mode?

Thanks!

|

Thu Mar 11 11:45:52 2010, Stefan Ritt, Readout of DRS Data Thu Mar 11 11:45:52 2010, Stefan Ritt, Readout of DRS Data

|

| Hao Huan wrote: |

|

Hi Stefan,

thanks to your help I can now successfully keep the Domino wave running at a stable frequency and maintain the channel cascading information in the Write Shift Register. (Since you told me WSR always reads and writes at the same time, I think I need to rewrite the information back every time after reading out from WSR to decide from which channel my data come, don't I?)

|

Yes you do. But if you have WSRLOOP=1 in the config register, this is done automatically. So the SR output is visible at the pin and will be fed back into the input.

| Hao Huan wrote: |

|

However I'm still having difficulty in reading out from the DRS cells. I use the ROI readout mode and assume as long as I give a pulse on RSRLOAD the data will come out one by one.

|

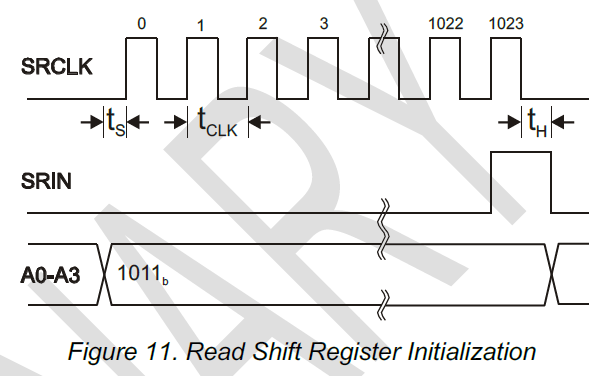

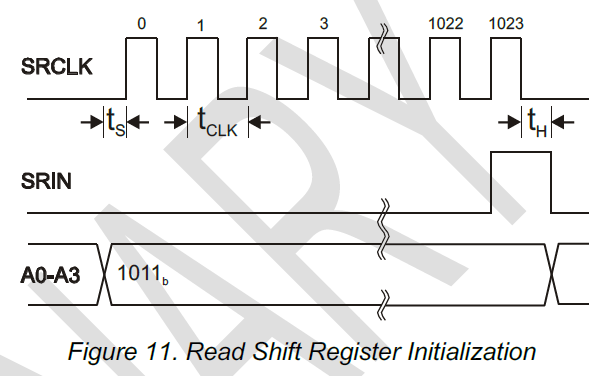

That's not correct. Have a look at Figure 14 of the datasheet. Do you see a single RSRLOAD pulse or many? There is only one RSRLOAD pulse to initialize the readout shift register, then the cells are clocked by SRCLK pulses.

| Hao Huan wrote: |

|

Also I read in the datasheet that WSROUT will give RSR output when DWRITE is low. Sometimes I see some random bits from this output and sometimes I see all zero's. What is the reasonable output I should see from WSROUT, say, when I'm running in the transparent mode with DWRITE low?

|

A single RSRLOAD pulse loads the RSR with a "1" at the domino stop position and "0" in all other places. A pulse on SRCLK shifts this "1" down the RSR. When it arrives at cell #1023, it will be visible for one clock cycle at WSROUT. The "double" functionality of WSROUT has the following background: Assume you use channel cascading 2x2048. Now the domino wave stopps in cell 1020 of the first channel for example. You have to read cells 1020,1021,1022,1024 of the first channel, then you continue with 0,1,2 on the second channel. But how do you know that you have to switch channels after the first four clock cycles? The SROUT output encodes the stop position (in this case 1020), but it needs 10 clock cycles before the information is available, so you don't have it after four cycles. That's where WSROUT comes into play: Since it outputs RSR bit by bit, it will show three "0", then a "1", when you are at cell 1023. Then you know that you have to switch channels immediately. That's why I output RSR via WSROUT if DWRITE is low.

|

Thu Mar 11 21:37:32 2010, Hao Huan, Input Bandwidth of the DRS Chip Thu Mar 11 21:37:32 2010, Hao Huan, Input Bandwidth of the DRS Chip

|

Hi Stefan,

I read in the DRS datasheet that the input bandwidth if 950MHz. However, it also says the output bandwidth in the transparent mode is 50MHz. Since in the transparent mode the input is routed to the output, does it mean the input bandwidth also gets reduced in the transparent mode? I don't know how the transparent mode works inside the chip of course, but this value would be important since if the hardware discriminators are connected to the output of DRS, we have to always work in the transparent mode.

Thanks!

|

Fri Mar 12 08:04:44 2010, Stefan Ritt, Input Bandwidth of the DRS Chip Fri Mar 12 08:04:44 2010, Stefan Ritt, Input Bandwidth of the DRS Chip

|

| Hao Huan wrote: |

|

I read in the DRS datasheet that the input bandwidth if 950MHz. However, it also says the output bandwidth in the transparent mode is 50MHz. Since in the transparent mode the input is routed to the output, does it mean the input bandwidth also gets reduced in the transparent mode? I don't know how the transparent mode works inside the chip of course, but this value would be important since if the hardware discriminators are connected to the output of DRS, we have to always work in the transparent mode.

|

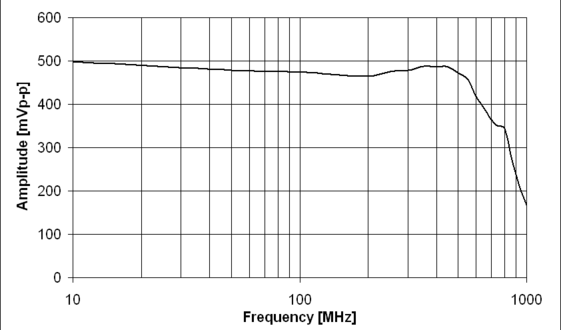

In transparent mode, the input signal also gets routed to the output, where it goes through an output buffer, which limits the bandwidth to about 50 MHz, but only for the output. The effective bandwidth to the sampling cells is not changed. Please note however that the 950 MHz are for the "chip only". We measured this by keeping the input amplitude from a function generator constant at the input pin of the chip (measured with a high speed oscilloscope). Since each signal source has a non-zero impedance, the signal tends to "shrink" at high bandwidth, and we had to adjust the level of the function generator to keep the amplitude constant at high frequencies. If you do a realistic input stage with the THS4508 for example, the achievable bandwidth will be around 800 MHz. |

Tue Mar 9 23:28:45 2010, Hao Huan, Serial Interface Frequency of the DRS Chip Tue Mar 9 23:28:45 2010, Hao Huan, Serial Interface Frequency of the DRS Chip

|

Hi Stefan,

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

Thanks!

|

Wed Mar 10 10:07:28 2010, Stefan Ritt, Serial Interface Frequency of the DRS Chip Wed Mar 10 10:07:28 2010, Stefan Ritt, Serial Interface Frequency of the DRS Chip

|

| Hao Huan wrote: |

|

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

|

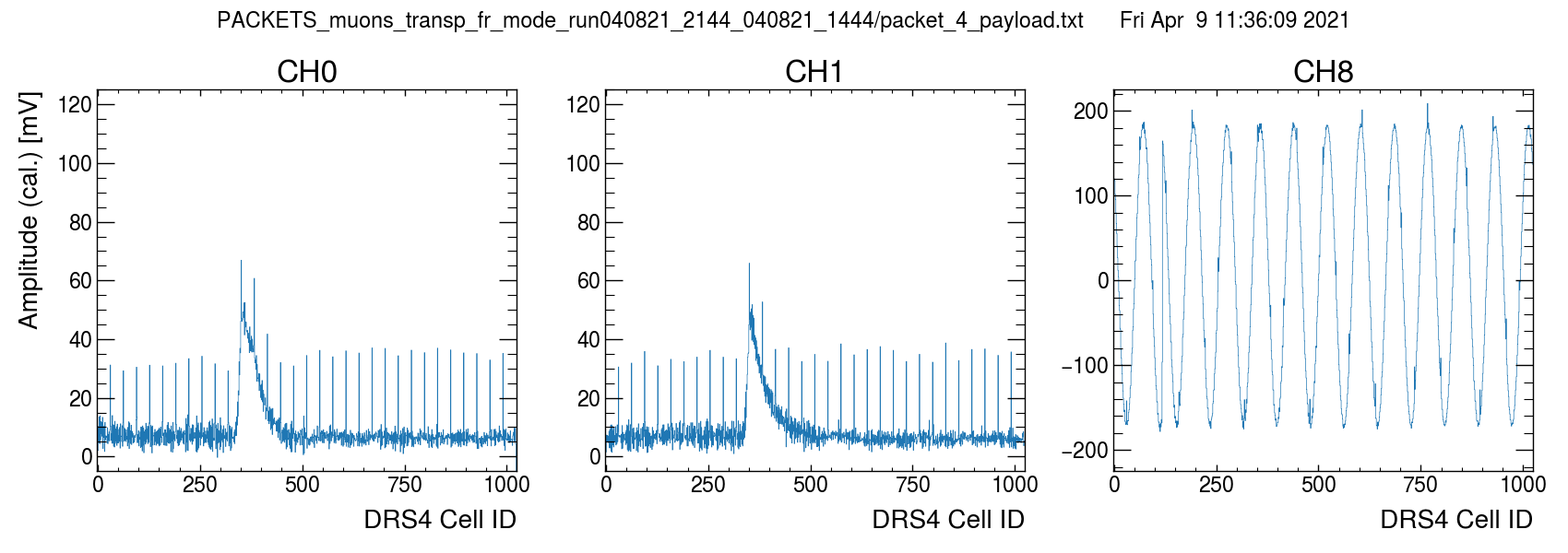

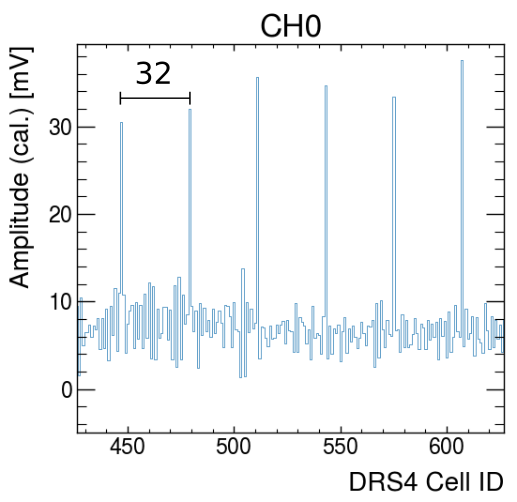

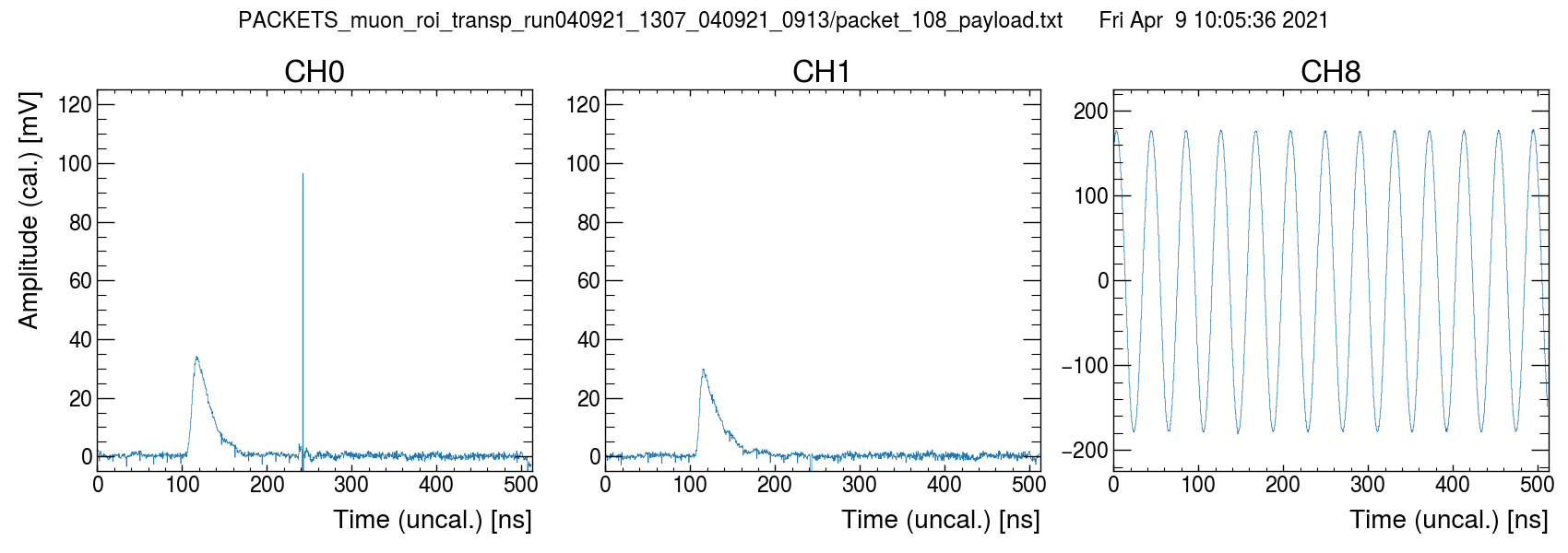

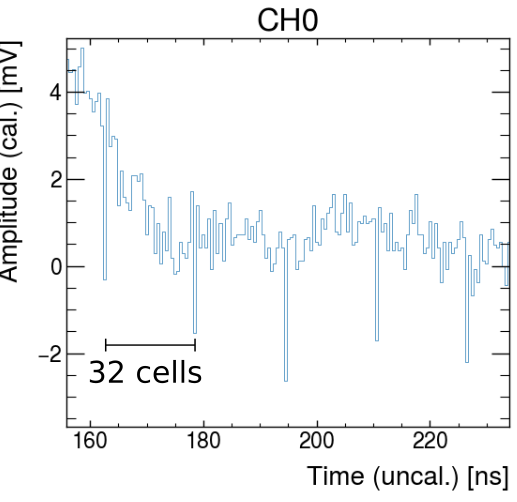

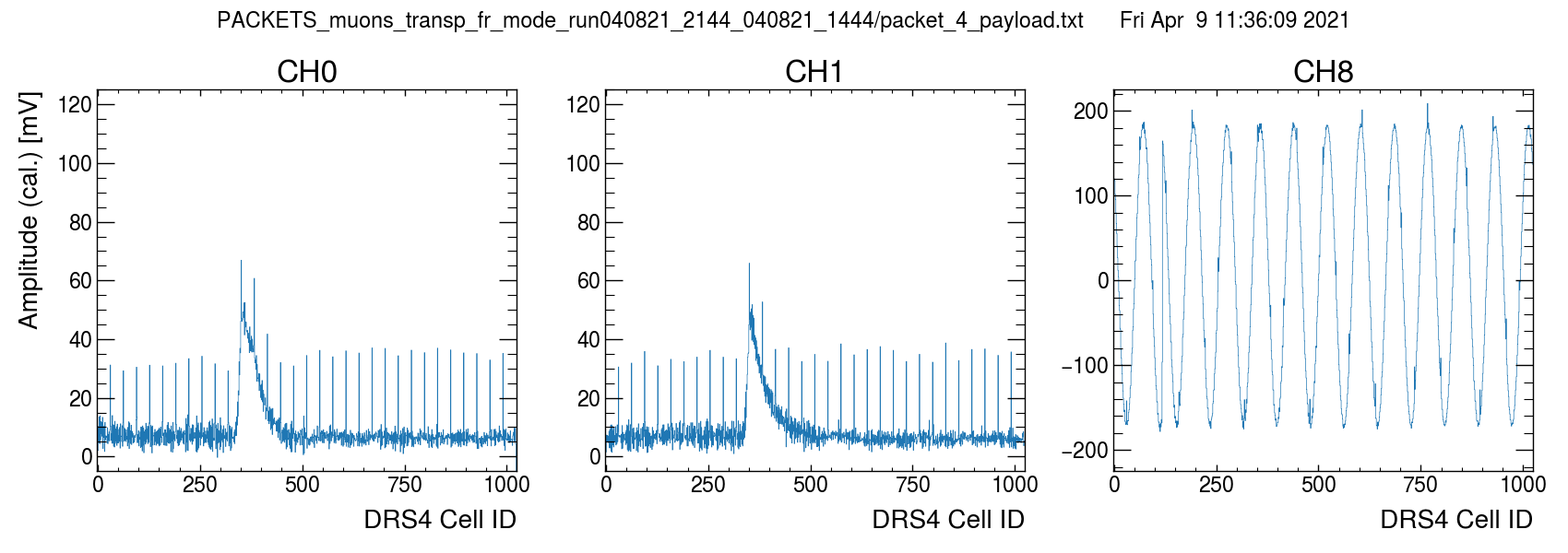

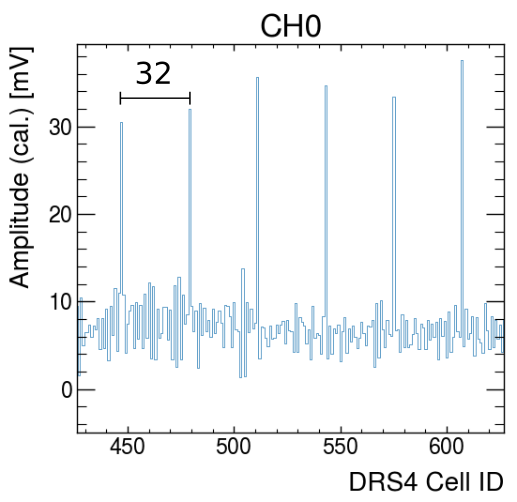

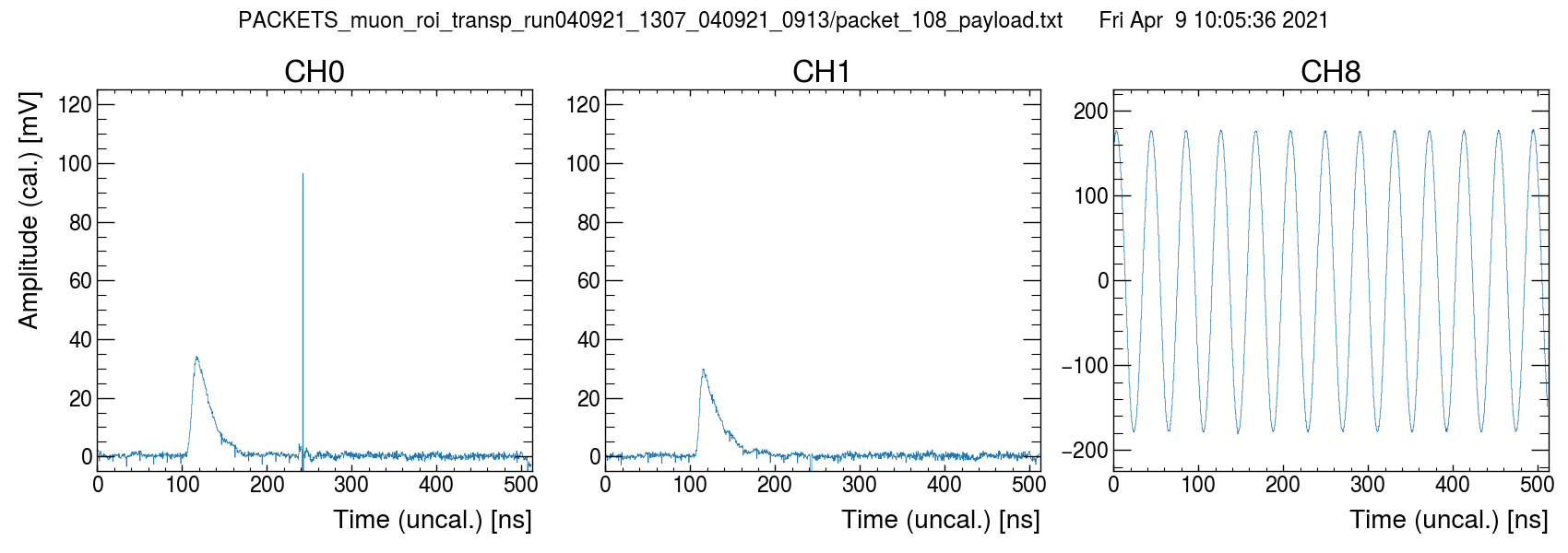

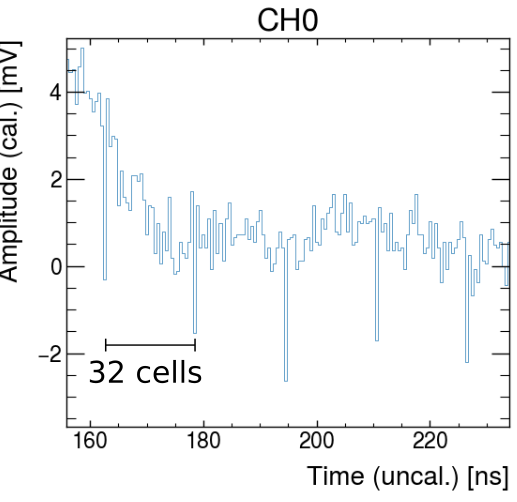

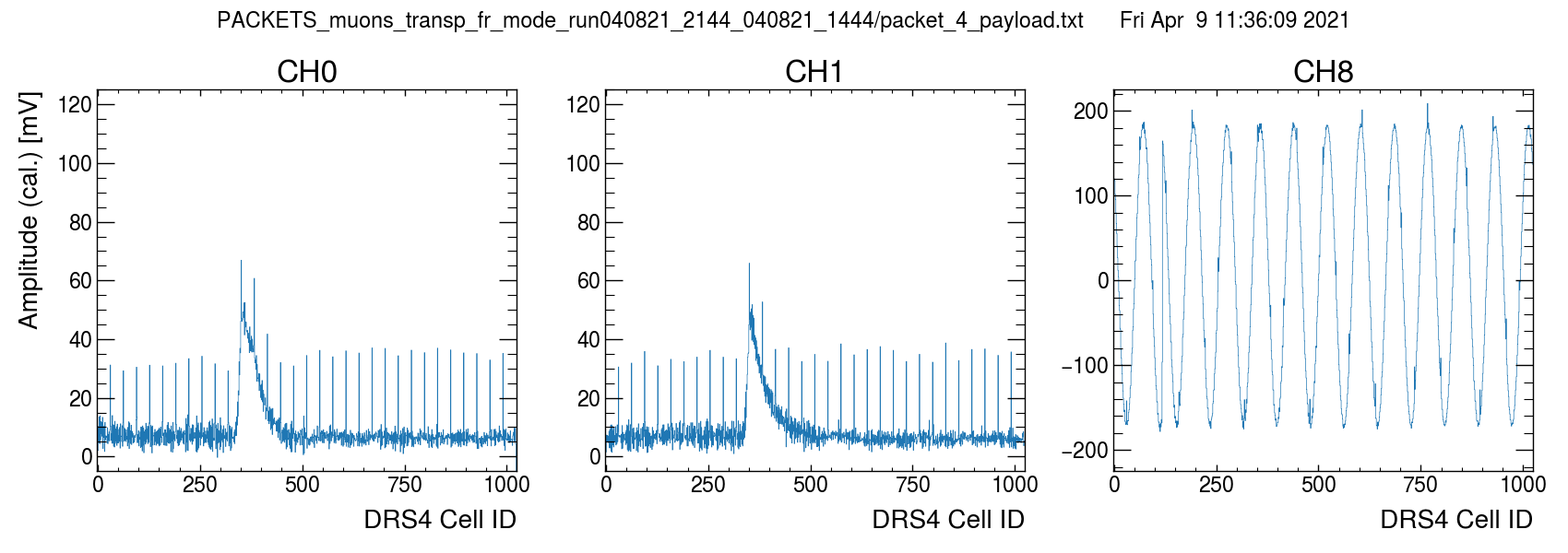

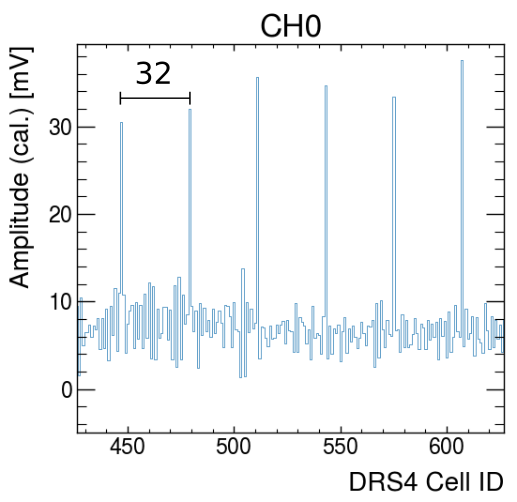

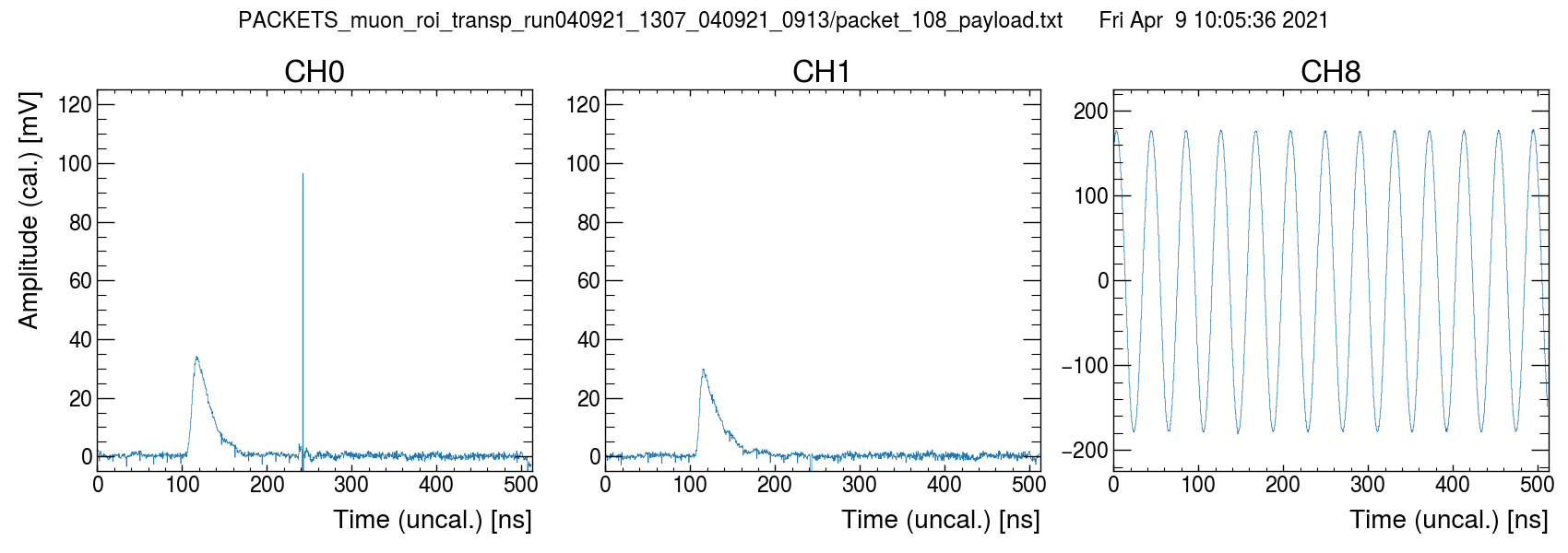

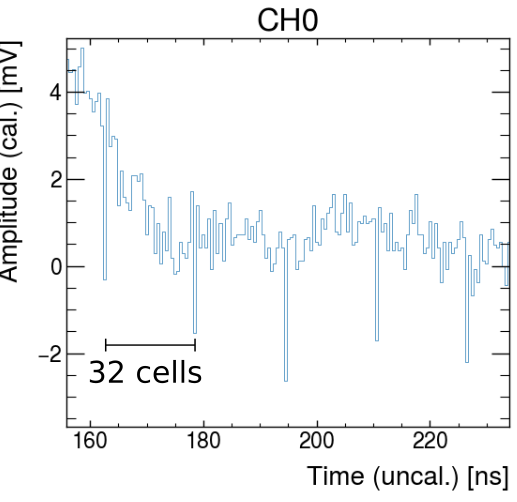

The reason for the 16.5 MHz is the following:

After each block of 32 bins, the DRS4 chip switches an internal segment, which causes some small spike at the analog output of the chip. This spike is a bit wider than 30ns, so if everything is digitized with 33 MHz, then you see small spiked each 32 cells. The appropriate solution would be to modify the firmware to digitize all cells with 30ns (33 MHz) and all cells with the spike with ~50 ns (20 MHz). If you do the ROI readout mode, you don't know for the first 10 cells if one of them belong to this class, since the cell address takes 10 cycles to be read out. So you would first have to read 10 cells, and then if you realize that one of them is one of the problematic ones (cell number modulo 32 is zero), you have to re-read the first 10 cells, and digitize the problematic cell with a longer settling time. Now this is a bit complicated to implement in the firmware, so I was just too lazy to do it and decided to digitize everything with 16.5 MHz. But if you are worried about the dead time, you should consider implementing the mentioned algorithm. |

Thu Mar 18 21:38:10 2010, Hao Huan, Serial Interface Frequency of the DRS Chip Thu Mar 18 21:38:10 2010, Hao Huan, Serial Interface Frequency of the DRS Chip

|

| Stefan Ritt wrote: |

|

| Hao Huan wrote: |

|

in the DRS4 datasheet I read that the optimal frequency for SRCLK is 33MHz. However in the evaluation board firmware SRCLK is toggled at rising edges of the internal 33MHz clock, i.e. the frequency of SRCLK itself is 16.5MHz instead. Is that frequency better than 33MHz?

|

The reason for the 16.5 MHz is the following:

After each block of 32 bins, the DRS4 chip switches an internal segment, which causes some small spike at the analog output of the chip. This spike is a bit wider than 30ns, so if everything is digitized with 33 MHz, then you see small spiked each 32 cells. The appropriate solution would be to modify the firmware to digitize all cells with 30ns (33 MHz) and all cells with the spike with ~50 ns (20 MHz). If you do the ROI readout mode, you don't know for the first 10 cells if one of them belong to this class, since the cell address takes 10 cycles to be read out. So you would first have to read 10 cells, and then if you realize that one of them is one of the problematic ones (cell number modulo 32 is zero), you have to re-read the first 10 cells, and digitize the problematic cell with a longer settling time. Now this is a bit complicated to implement in the firmware, so I was just too lazy to do it and decided to digitize everything with 16.5 MHz. But if you are worried about the dead time, you should consider implementing the mentioned algorithm.

|

Thanks! The suggested algorithm looks promising. However, if the spikes take place only for those specific cells, is it possible to absorb them into the offset calibration? |

Thu Mar 18 22:10:41 2010, Stefan Ritt, Serial Interface Frequency of the DRS Chip Thu Mar 18 22:10:41 2010, Stefan Ritt, Serial Interface Frequency of the DRS Chip

|

| Hao Huan wrote: |

|

Thanks! The suggested algorithm looks promising. However, if the spikes take place only for those specific cells, is it possible to absorb them into the offset calibration?

|

No, since they are not constant. The bus segments charge up between readouts with a time constant of about 0.5s. So if you do the readout with 1Hz event rate and with 100Hz event rate, the peaks will differ by a factor up to 10, so a constant offset correction cannot take care of that. |

Sun Mar 21 02:03:44 2010, Hao Huan, PLL Loop Filter Configuration Sun Mar 21 02:03:44 2010, Hao Huan, PLL Loop Filter Configuration

|

Hi Stefan,

in the datasheet it says at 6GSPS the typical loop filter parameters are 220Ω, 2.2nF and 27nF. If I want to run the Domino wave nominally at 1GHz, i.e. with a reference clock frequency around 0.5MHz, is there any recommended loop filter configuration? Is the setup of the evaluation board, that is, 220Ω, 3.3nF and 33nF an optimal choice?

Thank you very much.

|

Mon Mar 22 09:12:19 2010, Stefan Ritt, PLL Loop Filter Configuration Mon Mar 22 09:12:19 2010, Stefan Ritt, PLL Loop Filter Configuration

|

| Hao Huan wrote: |

|

in the datasheet it says at 6GSPS the typical loop filter parameters are 220Ω, 2.2nF and 27nF. If I want to run the Domino wave nominally at 1GHz, i.e. with a reference clock frequency around 0.5MHz, is there any recommended loop filter configuration? Is the setup of the evaluation board, that is, 220Ω, 3.3nF and 33nF an optimal choice?

|

The setup of the evaluation board is a good compromise which runs between 1 GHz and 5 GHz. Unfortunately I never found the time to investigate this in more detail. So if someone is willing to measure settling time and phase jitter with various combinations of R, C1 and C2, I'm more than happy to include this into the datasheet. |

Tue Apr 13 10:45:18 2010, lorenzo neri, evaluation board used like a counter Tue Apr 13 10:45:18 2010, lorenzo neri, evaluation board used like a counter

|

Hi all

it is possible to use the evaluation board like a counter?

I'm interested in the arriving time of all self trigger event in to a channel.

the input signal are 2V TTL of 10 ns at 50ohm, and the time acquisition window is 1 second.

can someone help me?

thanks in advance,

Lorenzo |

Tue Apr 13 13:12:43 2010, Stefan Ritt, evaluation board used like a counter Tue Apr 13 13:12:43 2010, Stefan Ritt, evaluation board used like a counter

|

| lorenzo neri wrote: |

|

Hi all

it is possible to use the evaluation board like a counter?

I'm interested in the arriving time of all self trigger event in to a channel.

the input signal are 2V TTL of 10 ns at 50ohm, and the time acquisition window is 1 second.

|

The evaluation board is as good or bad as an digital oscilloscope to work like a counter. At 1 GSPS, you have a window of one microsecond, which is certainly too short for your application. |

Fri Apr 9 17:14:45 2010, Hao Huan, Baseline Variation In Data Fri Apr 9 17:14:45 2010, Hao Huan, Baseline Variation In Data

|

Hi Stefan,

when I sample a constant input with the DRS 4 chip, there was a baseline variation showing up as a saw-tooth pattern which grows with the absolute value of the differential input. Do you think this is the kind of baseline variation mentioned in the evaluation board manual, i.e. coming from clock jitter in ADC sampling?

Thanks a lot!

|

Tue Apr 13 13:56:07 2010, Stefan Ritt, Baseline Variation In Data Tue Apr 13 13:56:07 2010, Stefan Ritt, Baseline Variation In Data

|

| Hao Huan wrote: |

|

Hi Stefan,

when I sample a constant input with the DRS 4 chip, there was a baseline variation showing up as a saw-tooth pattern which grows with the absolute value of the differential input. Do you think this is the kind of baseline variation mentioned in the evaluation board manual, i.e. coming from clock jitter in ADC sampling?

Thanks a lot!

|

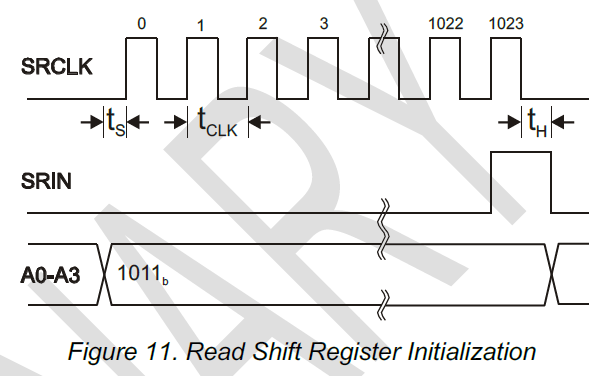

Please post an oscilloscope screenshot here and I can tell you. |